有些人可能认为数字电路,特别是使用CMOS和BiCMOS的数字电路很容易设计。但就像生活中的大多数事情一样,拥有多年经验的专业人士让工作看起来很容易!马戏团表演者毫不费力地玩弄许多物品。混凝土饰面营造出光滑的表面,顶级厨师可快速制作美食。现在回到电路设计。数字设计不就是将一些逻辑门串在一起吗?

要是生活这么简单就好了。适当的电源管理、电源去耦和接地对于成功的设计至关重要。

在本教程中,我们将讨论CMOS和BiCMOS IC,并展示一个简单的错误 - 没有V抄送——触发奇怪的行为。我们将解释为什么低功耗CMOS器件可能会很热。最后,我们研究这与电路导通时间的关系。

请注意,我们不是在谈论特定的应用程序或部件。本主题是 IC 设计中特有的,超越了任何特定的器件用途。这里的重点是细节,以及精心设计不会浪费任何东西——空间、电流、功率,你能想到的——或者烧伤你的手!

热门的CMOS/BiCMOS,或者为什么我在IC上烫伤了手指?

CMOS或BiCMOS的标志之一是低功耗。CMOS栅极仅在转换时消耗功率,因此这些电路在低速下运行。

很好,但为什么董事会很热?

图1所示为一个简单的CMOS电路。它是互补的(N和P器件),(因此称为互补金属氧化物半导体)。它是一和零,如此简单。在任何给定时刻,一个设备打开,另一个设备关闭。可能出现什么问题?事实证明,有些条件会导致电路消耗大量功率。

图1.典型的CMOS输入电路。

当CMOS电路大约介于1和<>之间时,顶部和底部晶体管都部分导通。因此,速度越快,每秒的转换次数就越多,使用的功率就越多。只要过渡快,零件就不会长时间停留在中间位置,大家都很高兴。表<>显示了一些安全逻辑高电平和低电平占电源电压的百分比。

| 表 1.MAX5391数字电位器的安全逻辑高电平和低电平 | ||||||

| 参数 | 象征 | 条件 | 最小值 | 典型值 | MAX | 单位 |

| 数字输入 | ||||||

| 最小输入高电压 | VIH | VDD= 2.6V 至 5.5V | 70 | % × VDD | ||

| VDD= 1.7V 至 2.6V | 75 | |||||

| 最大输入低电压 | V伊利诺伊州 | VDD= 2.6V 至 5.5V | 30 | % × VDD | ||

| VDD= 1.7V 至 2.6V | 25 | |||||

图2.CMOS输入引脚上的电压与电源电流的关系。数据为MAX5391数字电位器。

逻辑电平通常指定为电源电压的百分比。图2的波形是通过缓慢改变输入电压而形成的。遗憾的是,如果应用在 2.6V 和 5V 电源下,它将比适当的 80 和 5 消耗多 0 倍的电流。在7V逻辑摆幅的情况下,如果信号小于4.3V,则为安全零;如果高于<>.<>V,则为安全电压。

MAX5391将5V逻辑与5V电源接口,并可适应3V逻辑与3V电源。现在假设有人想将此器件与输入中的3V逻辑配对,但使用5V电源?零情况有效,但消耗的功率是必要功率的四到八倍。这就是CMOS可能运行过热的原因。正确的解决方法是在以不同电压运行的逻辑之间使用逻辑电平转换器。

其他关断或导通 — CMOS 逻辑问题

一般来说,人类喜欢看人。工程师尤其喜欢细节,而究竟什么是如此重要的开启和关闭?

问题实际上与电源排序有关。IC设计人员希望同时或至少按规定的顺序施加提供给所有引脚的电源。系统工程师知道,如果没有非凡的努力和大量额外的电路,这几乎是不可能的。因此,大多数电路必须自生自灭,至少在功率稳定后的几秒钟内不要自我破坏。(值得庆幸的是,现代部件不像一些早期的IC,如果不按规定的顺序供电,它们会在内部闩锁和自毁。然而,有些电路(如逻辑、ASIC或处理器)必须在逻辑电平信号施加到其输入之前上电。系统设计者必须理解为什么这是真的,不是理论上的,而是真正的事实。

大多数具有几年经验的系统设计人员都见过有人试图对CMOS逻辑问题进行故障排除。问题来来去去,似乎是随机的。就在事情开始变得有意义时,一切都变了。行为正常的电路节点突然不是。你猜到答案了吗?是的,当然!CMOS缺少电源。CMOS需要的功率非常小,如果一个输入引脚处于逻辑高电平,它就可以工作。它是如何工作的?

图3.典型的ESD保护结构。

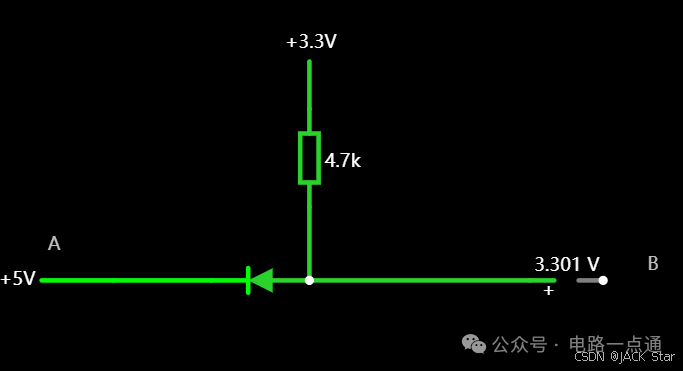

想象一组没有V的逻辑门抄送应用(图3)。在这里,该组拥有所有 V抄送在公共汽车上绑在一起的别针。现在,将一个逻辑高电平从外部正确供电的电路施加到信号引脚C。高电平通过顶部ESD二极管至V抄送总线。现在所有的门都有了电,似乎在工作......直到引脚C上的逻辑高电平变为零或低电平。然后,该逻辑部分停止工作,直到任何输入引脚变为高电平。有了像上面这样的几个输入引脚,该小组似乎在做愚蠢、不合逻辑的事情。这种情况对故障排除并不有趣,并导致了一个基本的设计规则:始终从基础开始 - 它是否插入,电源和接地是否在适当的电压下存在?

IC内部的ESD结构设计用于在客户将其安装到产品的PC板上之前保护该器件。IC内部的ESD二极管尺寸有限;它们无法承受来自外部来源的系统 ESD 事件。电力线浪涌和近距离雷击将使内部IC ESD二极管不堪重负。固定ESD存在实际限制,PC板和系统上需要外部ESD部件。

想象一下,一个电路有一个强大的电源连接到上面的引脚C。V抄送长时间关闭。顶部ESD二极管将尝试为V上的所有内容供电抄送轨。但是,ESD二极管很小,可能会随着时间的推移而失效。在这种情况下,可能有原因 V抄送例如,为了降低功耗而被删除。因此,添加一个与顶部ESD二极管并联的外部二极管可以解决这个问题。外部二极管Si或肖特基将承载电流并保护IC。

结论

经验的智慧希望使我们能够围绕一些令人沮丧的情况进行设计。如果没有,至少我们可以避免一些痛苦的教训。注重细节很重要。CMOS和BiCMOS IC的导通和关断时间存在特殊问题,因此我们解释了如何在没有V的情况下估计它们的导通时间并计算CMOS电路的行为抄送应用的。最后,如果不保持安全的和零电平,CMOS/BiCMOS器件可能会非常“燃烧”。最好的解决方法是在不同电压之间运行的逻辑电平转换器。

一句古老的谚语说:“一盎司的预防胜过一磅的治疗。在电路设计中当然如此。对设计中的数字逻辑系列有良好的工作知识是确保所得电路可靠、保持冷却且不会使用超过必要电流的最佳方法。预先的想法可以节省以后的召回或修订或董事会旋转。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18220浏览量

254628 -

CMOS

+关注

关注

58文章

5928浏览量

237840 -

ESD

+关注

关注

49文章

2256浏览量

174914

发布评论请先 登录

同步时序逻辑电路

异步时序逻辑电路

CMOS逻辑电路,CMOS逻辑电路是什么意思

高速电路信号完整性分析与设计—高速逻辑电路分析

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别

逻辑电路与时序逻辑电路的区别

什么是TTL逻辑电路 TTL与CMOS的区别和优缺点

TwinCAT3 EtherCAT抓包 | 技术集结

在使用TwinCAT测试EtherCATEOE功能时,我们会发现正常是无法使用Wireshark去进行网络抓包抓取EtherCAT报文的,今天这篇文章就带大家来上手EtherCAT抓包方式。准备环境硬件环境:EtherKit开发板网线一根Type-CUSB线一根软件环境TwinCAT3RT-ThreadstudiowiresharkEtherCATEOE工程

EtherCAT科普系列(8):EtherCAT技术在机器视觉领域的应用

机器视觉是基于软件与硬件的组合,通过光学装置和非接触式的传感器自动地接受一个真实物体的图像,并利用软件算法处理图像以获得所需信息或用于控制机器人运动的装置。机器视觉可以赋予机器人及自动化设备获取外界信息并认知处理的能力。机器视觉系统内包含光学成像系统,可以作为自动化设备的视觉器官实现信息的输入,并借助视觉控制器代替人脑实现信息的处理与输出。从而实现赋予自动化

新品 | 26+6TOPS强悍算力!飞凌嵌入式FCU3501嵌入式控制单元发布

飞凌嵌入式FCU3501嵌入式控制单元基于瑞芯微RK3588处理器开发设计,4xCortex-A76+4xCortex-A55架构,A76主频高达2.4GHz,A55核主频高达1.8GHz,支持8K编解码,NPU算力6TOPS,支持算力卡拓展,可以插装Hailo-8 26TOPS M.2算力卡。

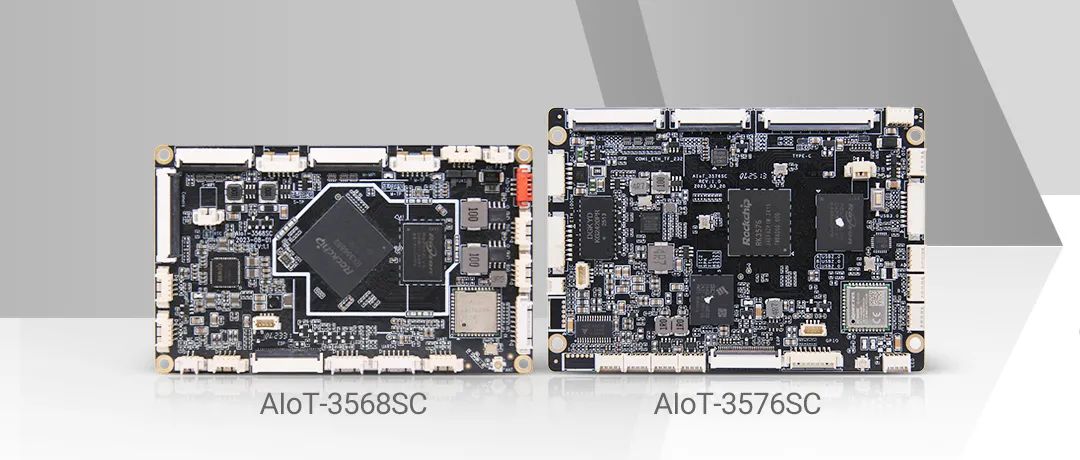

接口核心板必选 | 视美泰AIoT-3568SC 、 AIoT-3576SC:小身材大能量,轻松应对多场景设备扩展需求!

在智能硬件领域,「适配」是绕不开的关键词。无论是小屏设备的”寸土寸金”,还是模具开发的巨额成本,亦或是多产品线兼容的复杂需求,开发者总在寻找一款能「以不变应万变」的核心解决方案。视美泰旗下的AIoT-3568SC与AIoT-3576SC接口核心板系列,可以说是专为高灵活适配场景而生!无需为设备尺寸、模具限制或产品线差异妥协,一块核心板,即可释放无限可能。为什

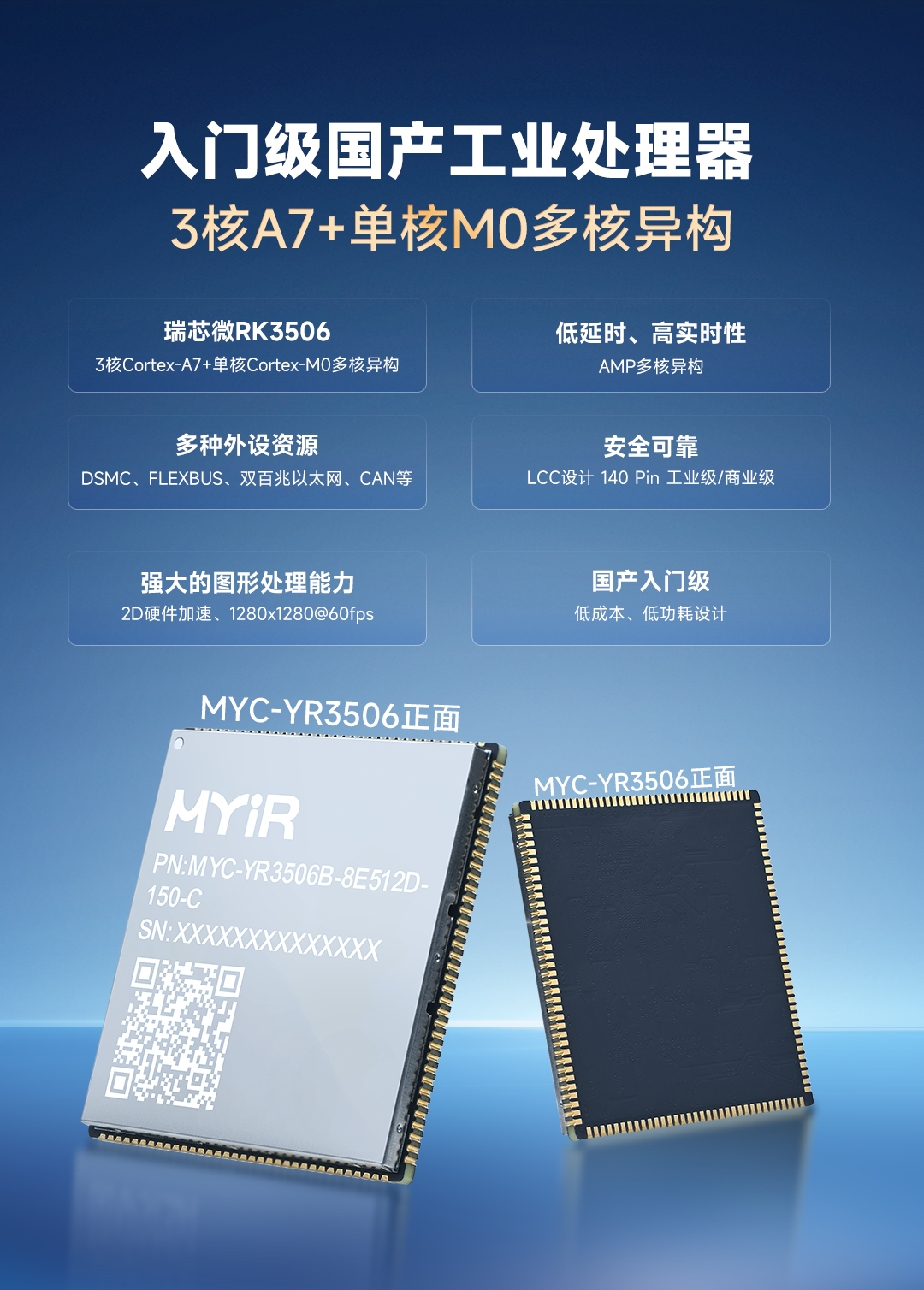

3核A7+单核M0多核异构,米尔全新低功耗RK3506核心板发布

近日,米尔电子发布MYC-YR3506核心板和开发板,基于国产新一代入门级工业处理器瑞芯微RK3506,这款芯片采用三核Cortex-A7+单核Cortex-M0多核异构设计,不仅拥有丰富的工业接口、低功耗设计,还具备低延时和高实时性的特点。核心板提供RK3506B/RK3506J、商业级/工业级、512MB/256MBLPDDR3L、8GBeMMC/256

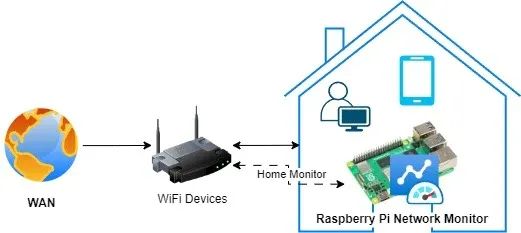

搭建树莓派网络监控系统:顶级工具与技术终极指南!

树莓派网络监控系统是一种经济高效且功能多样的解决方案,可用于监控网络性能、流量及整体运行状况。借助树莓派,我们可以搭建一个网络监控系统,实时洞察网络活动,从而帮助识别问题、优化性能并确保网络安全。安装树莓派网络监控系统有诸多益处。树莓派具备以太网接口,还内置了Wi-Fi功能,拥有足够的计算能力和内存,能够在Linux或Windows系统上运行。因此,那些为L

STM32驱动SD NAND(贴片式SD卡)全测试:GSR手环生物数据存储的擦写寿命与速度实测

在智能皮电手环及数据存储技术不断迭代的当下,主控 MCU STM32H750 与存储 SD NAND MKDV4GIL-AST 的强强联合,正引领行业进入全新发展阶段。二者凭借低功耗、高速读写与卓越稳定性的深度融合,以及高容量低成本的突出优势,成为大规模生产场景下极具竞争力的数据存储解决方案。

芯对话 | CBM16AD125Q这款ADC如何让我的性能翻倍?

综述在当今数字化时代,模数转换器(ADC)作为连接模拟世界与数字系统的关键桥梁,其技术发展对众多行业有着深远影响。从通信领域追求更高的数据传输速率与质量,到医疗影像领域渴望更精准的疾病诊断,再到工业控制领域需要适应复杂恶劣环境的稳定信号处理,ADC的性能提升成为推动这些行业进步的重要因素。行业现状分析在通信行业,5G乃至未来6G的发展,对基站信号处理提出了极

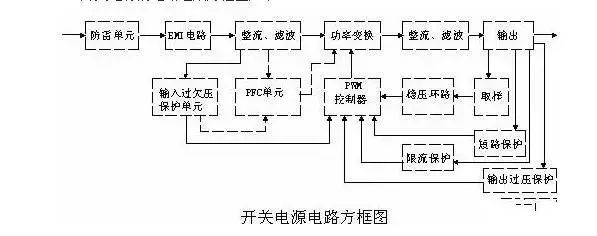

史上最全面解析:开关电源各功能电路

01开关电源的电路组成开关电源的主要电路是由输入电磁干扰滤波器(EMI)、整流滤波电路、功率变换电路、PWM控制器电路、输出整流滤波电路组成。辅助电路有输入过欠压保护电路、输出过欠压保护电路、输出过流保护电路、输出短路保护电路等。开关电源的电路组成方框图如下:02输入电路的原理及常见电路1AC输入整流滤波电路原理①防雷电路:当有雷击,产生高压经电网导入电源时

有几种电平转换电路,适用于不同的场景

一.起因一般在消费电路的元器件之间,不同的器件IO的电压是不同的,常规的有5V,3.3V,1.8V等。当器件的IO电压一样的时候,比如都是5V,都是3.3V,那么其之间可以直接通讯,比如拉中断,I2Cdata/clk脚双方直接通讯等。当器件的IO电压不一样的时候,就需要进行电平转换,不然无法实现高低电平的变化。二.电平转换电路常见的有几种电平转换电路,适用于

瑞萨RA8系列教程 | 基于 RASC 生成 Keil 工程

对于不习惯用 e2 studio 进行开发的同学,可以借助 RASC 生成 Keil 工程,然后在 Keil 环境下愉快的完成开发任务。

共赴之约 | 第二十七届中国北京国际科技产业博览会圆满落幕

作为第二十七届北京科博会的参展方,芯佰微有幸与800余家全球科技同仁共赴「科技引领创享未来」之约!文章来源:北京贸促5月11日下午,第二十七届中国北京国际科技产业博览会圆满落幕。本届北京科博会主题为“科技引领创享未来”,由北京市人民政府主办,北京市贸促会,北京市科委、中关村管委会,北京市经济和信息化局,北京市知识产权局和北辰集团共同承办。5万平方米的展览云集

道生物联与巍泰技术联合发布 RTK 无线定位系统:TurMass™ 技术与厘米级高精度定位的深度融合

道生物联与巍泰技术联合推出全新一代 RTK 无线定位系统——WTS-100(V3.0 RTK)。该系统以巍泰技术自主研发的 RTK(实时动态载波相位差分)高精度定位技术为核心,深度融合道生物联国产新兴窄带高并发 TurMass™ 无线通信技术,为室外大规模定位场景提供厘米级高精度、广覆盖、高并发、低功耗、低成本的一站式解决方案,助力行业智能化升级。

智能家居中的清凉“智”选,310V无刷吊扇驱动方案--其利天下

炎炎夏日,如何营造出清凉、舒适且节能的室内环境成为了大众关注的焦点。吊扇作为一种经典的家用电器,以其大风量、长寿命、低能耗等优势,依然是众多家庭的首选。而随着智能控制技术与无刷电机技术的不断进步,吊扇正朝着智能化、高效化、低噪化的方向发展。那么接下来小编将结合目前市面上的指标,详细为大家讲解其利天下有限公司推出的无刷吊扇驱动方案。▲其利天下无刷吊扇驱动方案一

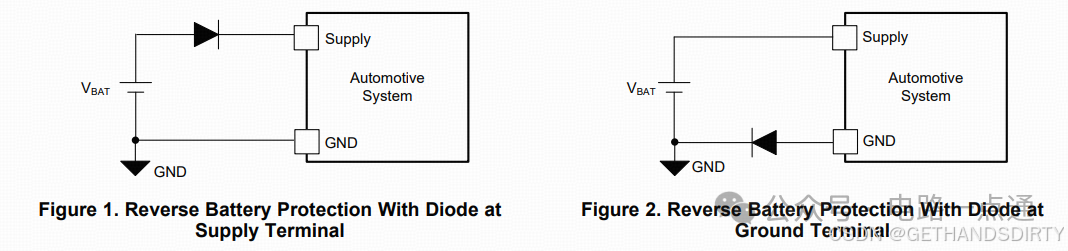

电源入口处防反接电路-汽车电子硬件电路设计

一、为什么要设计防反接电路电源入口处接线及线束制作一般人为操作,有正极和负极接反的可能性,可能会损坏电源和负载电路;汽车电子产品电性能测试标准ISO16750-2的4.7节包含了电压极性反接测试,汽车电子产品须通过该项测试。二、防反接电路设计1.基础版:二极管串联二极管是最简单的防反接电路,因为电源有电源路径(即正极)和返回路径(即负极,GND),那么用二极

为什么我的CMOS逻辑电路会烧坏

为什么我的CMOS逻辑电路会烧坏

评论