本文介绍了晶体和晶体振荡器的规格和特性,并有助于指定晶体和与晶体供应商合作。本文介绍了晶体的重要性能特征,包括谐振频率、谐振模式、负载电容、串联电阻、保持器电容、运动电感和电容、温度校准和驱动电平。

介绍

石英是一种压电材料,当放置在电场中时会移动。石英晶体是一块振动的石英。石英晶体有多种形状和尺寸可供选择,并且性能规格范围很广。这些规格包括谐振频率、谐振模式、负载电容、串联电阻、保持电容、运动电感和电容、温度校准和驱动电平。如果您了解这些参数以及它们与晶体性能的关系,您将成功地为您的应用指定晶体。

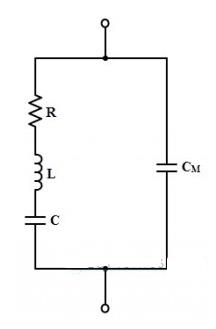

石英晶体可以建模为与并联电容器并联的串联LRC电路。图1显示了这个通用电路模型。

图1.通用晶体模型(基本模式)。

现在,我们将详细查看每个关键性能规格。

共振频率

低于30MHz的晶体通常指定在基频;高于 30MHz 时,它们通常指定为 3RD/ V千,甚至 7 个千泛音。(泛音仅在奇数倍处出现。因此,重要的是要知道振荡器是在基波模式下还是在泛音模式下工作。

泛音在概念上类似于谐波,只是晶体振荡泛音不是基波的精确整数倍。泛音选择基于使用尽可能低的泛音,这将导致晶体的基频低于30MHz。供应商校准 3RD泛音水晶在 3RD泛音,不是根本。例如,大多数晶体供应商会自动给你一个3RD泛音 50MHz 晶体(如果未指定基频模式或泛音模式)。如果插入 50MHz,则 3RD泛音晶体 进入专为基波模式晶体设计的振荡器电路,您可能会有一个以 50/3 或 16.666MHz 运行的振荡器!如果您不知道晶体的频率模式,请联系振荡器电路的设计者或制造商。

晶体供应商提供泛音晶体,因为随着频率的增加,石英材料变得越来越薄。15MHz至30MHz之间的晶体以基波或3RD泛音。从大约 30MHz 开始,石英变得如此薄,以至于在制造过程中难以处理,晶体供应商不喜欢处理薄石英。考虑到薄石英涉及的额外制造工作,选择泛音模式而不是基频模式指定的晶体可以大大降低成本。

石英晶体加工的最新发明是倒台面晶体,可以在更高的基波模式频率下制造出更薄的结构。倒置台面晶体具有两个显著的优点:它们可实现不太复杂的高频振荡器设计;它们通过避免使用外部电感器/电容来从晶体中感应出适当的泛音振荡模式来减少元件数量。.倒台面晶体的制造商可以指定远高于30MHz的基波模式晶体。但请注意,并非所有晶体供应商都可以提供倒置台面技术。请记住,泛音模式晶体不能用于基波模式振荡器,反之亦然。在这种情况下,泛音模式晶体可能会振荡,但频率不正确。

共振模式

晶体有两种共振模式,并联和串联,所有晶体都表现出两种共振模式。振荡器电路针对一种模式或另一种模式进行校准,但不能同时校准两种模式。对于频率精度要求不高于100ppm的应用,谐振模式通常不是问题。但是,如果您试图将频率(或时间)控制在100ppm以内,则谐振模式规格变得很重要。晶体供应商主要关心的是晶体在制造过程中以哪种模式进行校准。知道这些信息后,晶体供应商随后在客户指定的串联谐振或并联谐振中设置一个振荡器电路,并校准晶体。图2显示了晶体阻抗行为与频率的关系,以及每种谐振模式的相对位置。

图2.晶体阻抗与频率的关系。

负载电容

负载电容是使用并联谐振振荡模式时的重要规格。图2显示,晶体并联谐振模式始终高于串联谐振频率,并以感抗为特征。在并联谐振振荡模式下,晶体的电感(运动电感)与振荡器的负载电容并联,从而形成LC谐振电路。该LC确定振荡器频率。如果您的振荡器使用并行谐振,晶体供应商必须知道振荡器电路采用的负载电容。负载电容只是将晶体放置在振荡器电路中时与晶体本身并联的外部电路电容量。然后,晶体供应商将确保您的晶体在工厂使用相同的负载电容进行校准。供应商在负载电容方面非常灵活。询问他们可以指定什么负载电容范围。振荡器应在晶体供应商可接受的负载电容范围内。

对于串联谐振晶体,可以忽略负载电容规格。这是正确的,因为晶体的运动电感和运动电容是决定振荡频率的唯一LC元件。

在图2中,当晶体模型的净电感元件与晶体的内部保持电容共振时,就会发生反谐振。反谐振不用于振荡器设计。

串联电阻

串联电阻是与晶体本身的LC模型串联的有效电阻元件(见图1)。振荡器电路可以容忍一定程度的串联电阻,但不能太大。大多数晶体的典型范围为25Ω至100Ω。晶体供应商通常表征该电阻,并指定串联电阻的典型值或最大值。过大的晶体串联电阻会导致振荡器启动失败,因此必须在振荡器设计中内置足够的裕量。

上述准则的一个例外是32.768kHz手表晶体,其串联电阻可以在几十千欧姆。因此,对于此应用,振荡器电路必须适应这种高串联电阻。如果不解决这个问题,将导致32.768kHz振荡器不振荡。您不应期望使用专为 10MHz 晶体设计的振荡器和 32.768kHz 晶体。这是行不通的。

保持器电容

所有晶体都有小电极,将晶体连接到封装引脚。电极形成与晶体LC模型并联的分流电容,如图1所示。根据晶体的尺寸和封装,支架电容可能会有所不同。典型值范围为 2pF 至 6pF。一些振荡器不能容忍过大的保持电容。在较高频率下尤其如此,因为保持器电容的电抗会降低。确保晶体供应商的支架电容在振荡器的允许范围内。作为一般规则,最小化保持座电容(越小越好)。

运动电感和电容

运动电感和电容是晶体供应商提供的规格。它们描述了构成晶体电LC模型的L和C值。L与C的极端比值得注意,因为它在工作频率下会产生非常大的感性和容性电抗值。这些大值使晶体具有极高的“品质因数”,也称为“Q”。(Q是储存的能量与耗散能量的比值,也称为谐振频率下的电抗与串联电阻之比。对于 LRC 电路,Q = 1/R * 平方 (L/C)。(此推导超出了本文的范围。高Q值是理想的,因为较高的Q值意味着振荡器负载电容变化时的频率偏移较小,而由于振荡器电源电压等其他外部因素引起的偏移较小。根据您的应用,您的振荡器电路可能需要也可能不需要运动电感和电容的规格。

温度校准

石英晶体的频率随温度而变化。频率变化的量取决于石英从原始晶体切割的角度。随着频率的容差变小,温度范围也随之减小。AT切割晶体最常用于其在宽温度范围内的最高稳定性。

驱动器级别

必须限制晶体中的功率耗散,否则石英晶体实际上会因过度的机械振动而失效。由于非线性行为,晶体特性也随驱动电平而变化。分析振荡器设计以确定晶体中的功耗。功耗是晶体电流平方乘以晶体串联电阻的乘积。对于并联谐振振荡器,晶体电流等于负载电容两端的RMS电压除以负载电容在振荡器频率下的电抗。对于串联谐振晶体,晶体电流是晶体两端的RMS电压除以晶体内部串联电阻。晶体制造商将为特定产品线指定最大驱动级别。

总结意见

随着晶体出现在更多使用微控制器、数字信号处理器和数据转换器的产品中,预计晶体的使用量将会增加。晶体技术也在向前发展,从而带来更好的性能和更低的成本。目前,采用锁相环(PLL)的器件可以低成本地获得更高的频率,例如MAX9471/MAX9472,从最小200MHz的石英晶体输入输出高达5MHz的信号。将光纤技术与MAX3610等PLL结合使用,可获得212.5MHz的更高性能输出信号,抖动低至0.7ps有效值来自 26.56MHz 晶体输入。

乍一看,晶体似乎是简单的元件,只需插入电路即可。然而,对实际电路模型的分析以及对关键参数的理解揭示了它们的复杂性,并简化了将它们设计到下一个应用中的过程。

审核编辑:郭婷

-

微控制器

+关注

关注

48文章

7547浏览量

151331 -

转换器

+关注

关注

27文章

8696浏览量

147105 -

振荡器

+关注

关注

28文章

3832浏览量

139049

发布评论请先 登录

相关推荐

石英晶体的工作原理

石英晶体的结构,有哪些基本特性?

石英晶体好坏怎么判断

石英晶体的等效模型是什么?石英晶体阻抗与频率之间有什么关系?

指定石英晶体-Specifying Quartz Cryst

指定石英晶体

指定石英晶体

评论