DS5250高速安全微控制器采用80引脚四方扁平封装(QFP),是DS5002FP的引脚兼容、高性能升级版。从DS5002FP升级到DS5250可提供更高的性能、更严格的安全性和扩展的功能集,而无需更改现有的硬件设计。

升级的好处包括执行速度更快(DS25上高达5250MHz),改进的程序存储器三重DES加密,以及支持RSA等公钥加密算法的4096位模块化加速器引擎。扩展的内部SRAM、额外的时钟模式和双数据指针提高了编写应用代码时的灵活性。为DS5002FP开发的软件可以直接移植到DS5250上,只需进行极少的更改。

DS5250高速安全微控制器采用80引脚四方扁平封装(QFP),是DS5002FP的引脚兼容、高性能升级版。由于DS5250支持与DS5002相同的功能集,因此在现有设计中可直接替代DS5002FP。为DS5002的DS5250FP端口编写的软件,只需很少或无需更改,即可轻松提高系统性能和安全性,同时启用DS5250的功能(表1)。

性能

与DS5250FP相比,DS5002具有更高的最大时钟频率,每机器周期所需的时钟更少。其精简内核仅用5002个时钟周期执行单字节指令,而不是DS12FP的<>个时钟周期。

1kB指令高速缓存降低了程序存储器加密对执行速度的影响,因此,即使在3DES加密处于活动状态的情况下,DS5250的性能也比在相同时钟频率下的DS2FP平均提高5.5002倍。

| DS5002FP | DS5250 | 特征 |

| 性能 | ||

| 16兆赫 | 25兆赫 | 最大时钟频率 |

| 12 | 4 | 每个机器周期的时钟数 |

| 25.2 | 8.4* | 每条指令的平均时钟数 |

| 0.63 | 3.9* | 平均MIPS |

| 安全 | ||

| 80 位专有算法(单字节) | 单个 DES 或 3DES(8 字节块) | 加密程序存储器中的数据(与程序执行并行解密) |

| 不 | 是的 | 程序和 MOVX 存储器的单独加密 |

| 没有 | 4096 位 MAA 引擎(1024 位公钥模块化幂运算,650 毫秒内) | 公钥加密支持 |

| SDI引脚 | SDI引脚:无电池/电池连接;低温 (< 60°C)** | 破坏性复位 (DRS) 触发器 |

| 不 | 是(可选) | 端口写入时的定时访问 |

| 48 字节 | 1024 字节 | 矢量内存 |

| 不 | 是的 | 独特的激光内径 |

| 不 | 是的 | 安全装载机 |

| 灵活性 | ||

| 1x,空闲,停止 | 1x,空闲,停止;2倍/4倍(晶体倍增器);除以 1024 (PMM);内部环形振荡器 | 振荡器时钟模式 |

| 1 | 2 | 串行端口 |

| 2 | 3 | 定时器 |

| 2 | 6 | 外部中断 |

| 不 | 硬件和加载器ROM | 闪存支持 |

| 不 | 是的** | 实时时钟 |

|

*零拉伸周期,16位标准寻址模式。 **仅限 100 引脚 QFP。 |

||

安全

DS5250外部程序存储器采用单DES或3DES加密自动保护;数据存储器可以选择加密。与DS5002FP一样,加密密钥由板载随机数发生器自动生成和加载。DS5250使用单独的密钥进行程序存储器和数据存储器加密,对程序存储器使用8字节块加密,而不是逐字节加密,从而提高安全性。

DS5250提供4kB内部SRAM,可用作程序存储器、数据存储器或两者兼而有之;1kB的SRAM可以选择用作扩展堆栈。

除DES和3DES外,DS5250还包括一个4096位MAA引擎,以支持RSA等公钥加密算法。扩展的片内矢量RAM(1024字节,DS48FP为5002字节)为存储关键数据和代码(如中断和复位处理程序)提供了更多空间。

为了保护内部和外部存储器,DS5250根据多种条件触发破坏性复位(DRS)。与DS5002FP一样,SDI引脚上的信号清除存储器加密密钥、矢量RAM和任何外部电池备份存储器。此外,DS5250在电池丢失或新连接时触发DRS。

DS5250可编程规避功能可防止在短时间内出现异常(用户选择)复位次数的试错攻击。启用后,此安全模式会根据用户选择的时间以递增的延迟响应重复的重置攻击。根据遇到的重置次数,恢复执行之前的延迟时间可能会从几秒钟增加到几小时再到几周。在最高安全级别下,DS5250可以响应暴力攻击,将执行永久锁定在ROM内,使器件在完全擦除之前无法使用。

针对攻击的另一种对策是对所有输出端口写入进行可选的定时访问限制。这增加了攻击者必须正确加密才能将可识别模式写入 I/O 端口的指令字节数。

灵活性

与DS5250FP相比,DS5002提供了一组扩展的片内资源,提高了应用和系统设计的灵活性。除了增加1kB的矢量RAM外,DS5250还提供4kB的内部SRAM,可用作程序存储器、数据存储器或两者兼而有之。在该内部SRAM中,1kB可以选择用作扩展堆栈。

在时钟控制和电源管理方面,DS5250提供了DS5002FP支持的标准停止和空闲模式以外的许多功能。时钟倍频器允许外部晶体频率在内部增加一倍或四倍,从而扩大用于产生给定时钟速率的晶体范围,并允许降低外部EMI。电源管理模式 (PMM) 将外部晶体频率除以 1024,以在不需要全速运行期间降低功耗。如果在PMM期间需要对串行输入或中断进行快速响应,则可以使用回切功能自动恢复到全速操作以响应这些输入。工作频率约为12MHz的内部环形振荡器代替外部晶体输入,允许快速退出停止模式,而无需等待晶体振荡器预热。

将设计升级到DS5250的要求

DS5250支持DS5002FP的大部分功能。例外情况是:

DS5250使用专用数据总线(BA14–BA0和BD7–BD0)访问所有外部存储器(或存储器映射I/O)。不支持使用端口 0 和 2 上的多路复用地址/数据总线访问内存。

程序内存缓存允许尽可能快地执行程序。因此,与缓存操作自然相关的填充和停止可能会影响 I/O 计时或位爆炸操作。

DS5250程序存储器空间的安全增强可能会使组交换和/或存储器覆盖方案复杂化。具体而言,程序加密密钥修改器寄存器寄存器等功能以及程序和数据存储器使用不同的加密方案可能需要重新评估DS5002FP的存储器映射操作方法。

DS5250不支持可重编程外设控制器(RPC)模式。

如果设计依赖于这些特性之一,则可能需要对DS5250进行一些细微的修改。

此外,通过专用数据总线访问的外部RAM的时序要求从DS5002FP到DS5250略有变化。交流时序分析将验证RAM和DS5250是否兼容,特别是当DS5250的运行频率超过DS5002FP的最大16MHz时。

将软件从DS5002FP移植到DS5250

DS5002FP和DS5250共享相同的指令集,DS5002FP中的大多数特殊功能寄存器(SFR)在DS5250中具有相同的位置和功能。但是,将现有的DS5002FP软件移植到DS5250时,可能需要进行一些更改。

内存配置

DS5002FP和DS5250(仅限80引脚QFP)通过专用地址总线访问存储器时支持两种类型的外部存储器配置。

图1中的多芯片配置显示了连接到V的MSEL引脚抄送以及连接到专用总线的四个 32kB x 8 SRAM 器件。两个器件(由/CE2和/CE1启用)映射为64kB的程序存储器,另外两个器件(由/CE4和/CE3启用)映射为64kB的数据存储器。要选择此配置,请使用以下 SFR 设置:

ACON.1 (AM1) 和 ACON.0 (AM0) 应设置为 0 以选择 16 位寻址模式(以便与现有软件兼容)。

MSIZE应设置为00h以选择32kB芯片大小。请注意,此寄存器只能在ROM加载器模式或用户加载器模式下设置。

MCON.1 (PM) 应设置为 1 以选择非分区模式。

程序存储器自动加密;PBCC.0 (TDESE) 位选择是将单个 DES (TDESE = 0) 还是 3DES (TDESE = 1) 加密用于程序存储器。此位只能在ROM加载器模式或用户加载器模式下设置。

如果需要数据存储器加密,DMOS.1 (C3EE) 和 DMOS.2 (C4EE) 应设置为 1。这些位中的每一个都控制一个内存设备上的加密。

图1.在多芯片存储器配置中,外部程序和数据存储器分布在四个32kB x 8 SRAM器件上。

在单芯片配置中(图 2),MSEL 引脚接地,单个 128kB x 8 SRAM 器件连接到专用总线。该器件(由/CE1启用)用于程序和数据存储器,/CE2和/CE3转换为两条附加地址线。要选择此配置,应使用以下 SFR 设置:

ACON.1 (AM1) 和 ACON.0 (AM0) 应设置为 0 以选择 16 位寻址模式(以便与现有软件兼容)。

MSIZE应设置为XX001001b,以选择128kB的芯片大小。请注意,此寄存器只能在ROM加载器模式或用户加载器模式下设置。

程序存储器自动加密;PBCC.0 (TDESE) 位选择是将单个 DES (TDESE = 0) 还是 3DES (TDESE = 1) 加密用于程序存储器。此位只能在ROM加载器模式或用户加载器模式下设置。

数据存储器会自动加密。

图2.在单芯片存储器配置中,一个128kB x 8 SRAM器件可容纳外部程序和数据存储器。

处理中断

DS5002FP支持的5250个中断源中有5250个在DS<>上得到相同的支持。DS<>也支持电源故障中断,但有以下区别:

电源故障中断向量位于 33 小时而不是 2Bh;其优先级(0,最高)保持不变。

此中断的使能位位于 WDCON.5 (EPFI) 处。

指示已发生电源故障事件的标志位于 WDCON.4 (PFI) 中。

确定复位源

在DS5002FP上,上电复位时,/POR位(PCON.6)被清除,软件可以检查该位以确定复位的原因。在DS5250上,POR位(WDCON.6)执行此功能;但是,当上电复位发生时,会设置(未清除)此位。这两个位都需要软件重置定时访问写入。

DS5250精简内核仅用5002个时钟周期执行单字节指令,而不是DS12FP的<>个时钟周期。

看门狗控制

看门狗在所有部件上的功能相同。但是,在DS5250上控制看门狗时,以下更改和添加适用:

使能看门狗位位于WDCON.1 (EWT)。

看门狗复位位位于WDCON.2 (RWT)。

指示已发生监视程序计时器重置的标志位于 WDCON.2 (WTRF)。与DS5002FP上的WTR位不同,该位必须显式写入0才能清除。

DS63提供看门狗中断(矢量5250h)。如果由 EWDI (EIE.4) 位启用此中断,则会在看门狗复位发生之前触发,从而允许根据需要由软件处理看门狗超时。DS1上的WD0–WD7 (CKCON.6-5250)位控制看门狗中断和复位的时间段,但复位时间默认为与DS5002FP大致相同的值。

随机数生成

随机数寄存器(RNR)在所有三个部分中的功能相同。但是,在DS5250上,指示新随机数准备就绪的位位于RAMST.0(RNRF)。在DS5250上生成新的随机数所需的时间约为30ms。

CRC运营

DS5250支持新的CRC-32计算功能,计算CRC-16值的过程不同。

DS5250没有CRC (C1h)、CRCLow (C2h)和CRCHigh(C3h)寄存器。

要执行 CRC-16 计算,首先通过将 CRCNT (RAMST.16) 位清除为 1 来选择 CRC-0 模式。然后将CRC数据值写入CRC1(B1h)寄存器,允许至少五个机器周期(或写入之间的三个NOP)使CRC寄存器有时间建立。写入最后一个值后,可以从CRC16:CRC2读取CRC-1值。

不再需要将CRC LSB字节写回引擎两次以清除CRC寄存器。在DS5240上,将任何值写入CRC2会自动将CRC1、CRC2、CRC3和CRC4清除为0。

| 装置 | 主动123T |

| 定时器2 |

CKCON.5 (T2M): 时钟模式选择 P1.1 (T2EX), P1.0 (T2): 外部输入 T2CON: 标志和模式控制 T2MOD: 模式控制 TH2, TL2: 定时器计数 MSB/LSB RCAP2H, RCAP2L: 定时器捕获 MSB/LSB |

| 数据指针 |

DPH1、DPL1:数据指针 1 MSB/LSB DPS:数据指针选择 |

| CRC: 32 |

RAMST.1 (CRCNT): CRC 16/32 Select CRC1, CRC2, CRC3, CRC4: I/O 寄存器 |

| 德斯发动机 |

UDESC:DES 发动机控制 UDESD:DES 发动机数据输入/输出 |

| 模块化加速器发动机 |

MAS0、MAS1:操作大小选择 MACT:加速器控制寄存器 |

| 用户加载器模式 |

ACON.6 (ULME): 用户加载模式启用 PEK1、PEK2、DEK、ROMST、PBCD、 PBCC:加密/加载控制 |

| 激光内径 | BP:引导加载程序密码寄存器 |

| 晶体倍增器和电源管理 | PMR:电源管理寄存器 |

| 扩展的 1kB 堆栈 |

ESP:扩展堆栈指针 RAMST.5、RAMST.4:RAMST1 模式选择 |

| 输出端口定时:访问保护 | RAR.3 (TAP):定时:访问端口启用 |

结论

DS5250的许多新功能无需任何硬件更改即可使用。表 2 总结了这些新功能以及控制这些功能的 SFR。

DS5250的特性集比DS5002FP提高了安全性、性能和灵活性。只需稍作改动即可将软件移植到DS5250,轻松升级DS5002FP设计。

将设计升级到 100 引脚 QFP

DS5250采用100引脚QFP封装,除了与DS80FP引脚对引脚兼容并支持DS5002FP存储器接口模式外,具有5002引脚封装的所有特性。它还提供以下功能:

扩展的内存接口选项,高达 4MB 的程序和数据存储器以及 4MB 的内存映射 I/O

板载 RTC(由外部 32.768kHz 晶体驱动),可用于时间戳和自行设定的到期日期

温度传感器,可触发 DRS 以响应低温攻击

额外的SDI输入引脚,可连接到中断,以实现软件控制的篡改响应

外部闪存的硬件支持(DS5250包含加载器ROM支持)

审核编辑:郭婷

-

微控制器

+关注

关注

48文章

7840浏览量

153292 -

存储器

+关注

关注

38文章

7606浏览量

165845 -

QFP

+关注

关注

1文章

31浏览量

14763

发布评论请先 登录

相关推荐

高速安全微控制器DS5250电子资料

DS5250 pdf datasheet

DS5002FP/DS5002 pdf datasheet

DS5250中文资料 (高速安全微控制器)

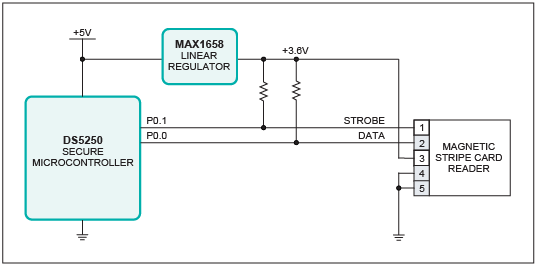

DS5250与磁卡读卡器的连接

利用DS5250产生RSA密钥

DS5002FP-16 DS5002FP-16 - (Maxim Integrated) - 嵌入式 - 微控制器

DS5002FMN-16 DS5002FMN-16 - (Maxim Integrated) - 嵌入式 - 微控制器

DS5002FPM-16 DS5002FPM-16 - (Maxim Integrated) - 嵌入式 - 微控制器

DS5250与磁条读卡器接口

DS5250微控制器的模幂时序

利用DS5250产生RSA密钥

使用Keil C编译器处理DS5250

通过将DS5250用作安全协处理器来提高系统安全性

使用DS5250作为DS5002的直接升级

使用DS5250作为DS5002的直接升级

评论