SPI接口概述

AT32的SPI接口提供软件编程配置选项,根据软件编程配置方式不同,可以分别作为SPI和I2S使用。 本文将分SPI和I2S分别介绍SPI接口作SPI或I2S的功能特性以及配置流程。

AT32 SPI特点:

可编程配置的全双工或半双工通信

--全双工同步通信

--半双工同步通信(可以根据软件编程配置选择传输方向:发送或接收)

可编程配置主/从模式

可编程配置的CS模式:硬件/软件CS模式

可编程配置的时钟极性和相位

可编程配置的数据传输顺序(MSB/LSB)

可编程配置的错误中断标志(CS脉冲异常,接收溢出错误,主模式错误,CRC校验错误)

数据接收/发送均支持DMA

兼容TI的SSP协议(即TI模式)

AT32 I2S特点:

可编程配置的操作模式

--从设备发送

--从设备接收

--主设备发送

--主设备接收

可编程配置的时钟极性

可编程配置的时钟频率(8KHz到192KHz)

可编程配置的数据位数(16位,24位,32位)

可编程配置的声道位数(16位,32位)

可编程配置的音频协议

--I2S飞利浦标准

--高字节对齐标准(左对齐)

--低字节对齐标准(右对齐)

--PCM标准(长帧/短帧)

支持I2S全双工

支持DMA传输

在通讯期间可提供频率固定为256倍Fs(音频采样频率)的外设主时钟

SPI功能介绍

本章主要介绍SPI基本功能,以及AT32 SPI的各种附加可配置选项。

SPI硬件接口

SPI接口定义如下:

CS:片选引脚(可选)。 通常由主机输出,从机输入。 后续CS管理章节作详细介绍。

SCK:时钟引脚。 由主机输出,从机输入。

MISO:主收从发引脚。 主机则作为接收数据引脚,从机则做为发送数据引脚。

MOSI:主发从收引脚。 主机则作为发送数据引脚,从机则作为接收数据引脚。

以下介绍几种常见的SPI通信接线方式。

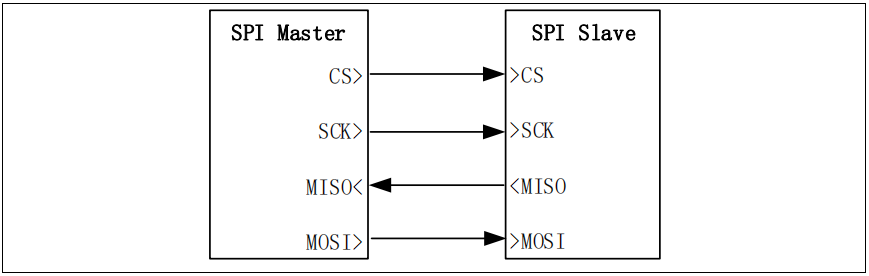

1)如下图1,是单主单从、全双工、CS硬件模式的应用接线示意图。

图1 SPI单主单从、全双工、硬件CS管理接线示意

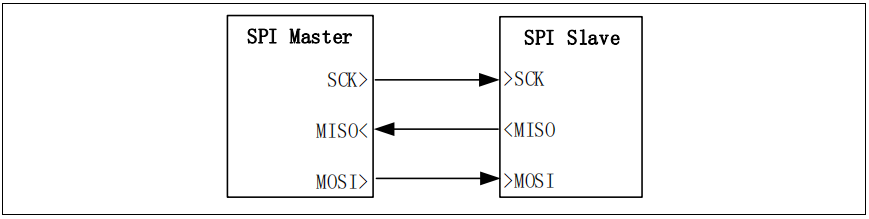

2)如下图2,是单主单从、全双工、CS软件模式的应用接线示意图。 在CS软件管理模式下,无需使用CS引脚,主/从机的CS引脚都可以释放给其他应用使用。 此时,从机对SWCSIL位清0或置1等效于“硬件CS模式”下的CS引脚输入低电平和高电平。 主机则必须将SWCSIL位置1,以保证正确的处于主机模式。

图2 SPI单主单从、全双工、软件CS管理接线示意

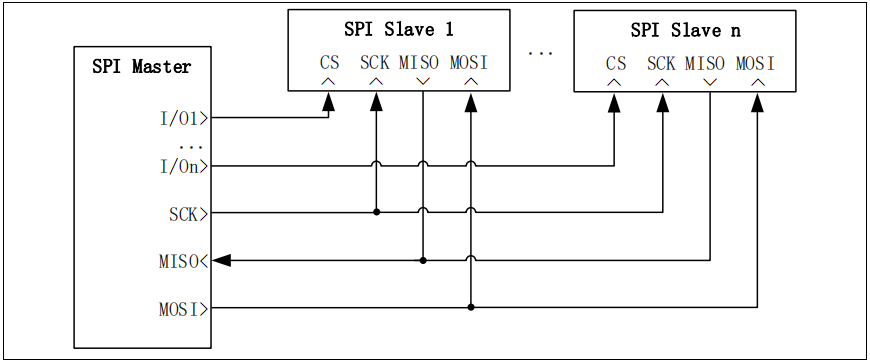

3)如下图3,是单主多从全双工接线示意。

主机使用普通I/O口1n输出以驱动从机1n的片选CS,主机的SCK,MISO,MOSI和从机的SCK,MISO,MOSI引脚一对多连接。 此时SPI主机可以通过I/O1~n的选择与多个从机进行分时通信。 此时从机必须使用硬件CS模式。 主机可以使用软件CS模式,主机CS对应的引脚可以释放给其他应用使用。

图3 SPI单主多从、全双工接线示意

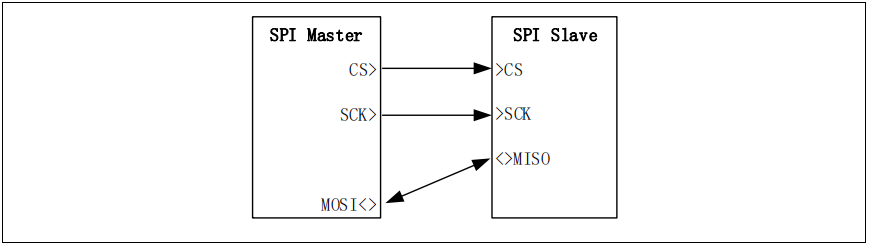

4)如下图4,AT32的SPI增加了SPI半双工模式,此模式下只需要使用3线即可通信。

主机使用MOSI进行数据收/发。 当主机配置为半双工发送模式(SLBEN=1,SLBTD=1)时,主机MOSI为输出引脚,用于发送数据; 当主机配置为半双工接收模式(SLBEN=1,SLBTD=0)时,主机MOSI为输入引脚,用于接收数据。

从机使用MISO进行数据收/发。 当从机配置为半双工发送模式(SLBEN=1,SLBTD=1)时,从机MISO为输出引脚,用于发送数据; 当从机配置为半双工接收模式(SLBEN=1,SLBTD=0)时,从机MISO为输入引脚,用于接收数据。

图4 SPI单主单从、半双工接线示意

SPI数据接收和发送

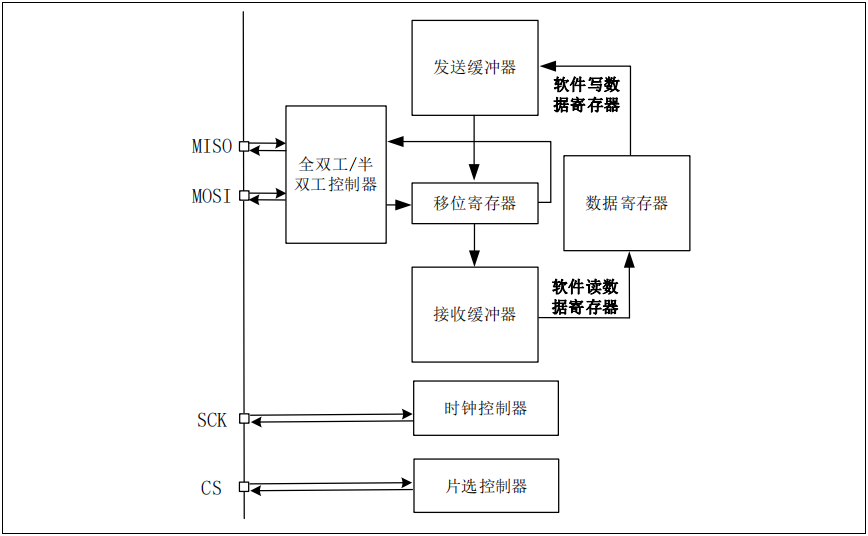

如下图5,用户软件程序可以读和写数据寄存器,其他部分全由硬件自动完成。

以全双工,硬件CS管理,8bit数据格式为例。 收发一笔数据的流程如下:

作为SPI主机时:

软件使能SPI(SPIEN=1)后,硬件控制CS引脚输出低电平,以片选从机。 之后软件往数据寄存器写入数据,如下图5的“软件写数据寄存器”处,相当于往发送缓冲器写入待发送数据,之后硬件会自动将发送缓冲器的待发送数据搬运到移位寄存器。 同时将发送缓冲器空标志置1(TDBE=1),以提醒软件又可以往数据寄存器写入下一笔待发送的数据。 之后硬件立即开始在SCK引脚上输出时钟信号,并在MOSI引脚上发出待发送数据的第一bit数据。 之后硬件从MISO引脚上读取待接收数据的第一bit数据并放入移位寄存器中(移位寄存器由于之前发送了1bit数据,此时正好有一bit位置可以存放收到的数据)。 之后硬件会通过移位寄存器自动发送和接收剩下的7bit数据。 之后硬件会将移位寄存器中接收到的8bit数据搬运到接收缓冲器中,并将接收缓冲器满标志置1(RDBF=1),以提醒软件可以通过读取数据寄存器来读取刚刚接收到的这笔数据。

作为SPI从机时:

软件使能SPI(SPIEN=1)后,软件往数据寄存器写入数据,相当于往发送缓冲器写入待发送数据,然后硬件会将发送缓冲器空标志清0(TDBE=0),以提醒软件此时发送缓冲器已有待发送数据了。 之后硬件检测CS引脚和SCK引脚,等待来自主机的片选和时钟信号。 检测到片选和时钟信号之后,硬件自动将发送缓冲器的待发送数据搬运到移位寄存器并在MISO引脚上发出待发送数据的第一bit。 同时将发送缓冲器空标志置1(TDBE=1),以提醒软件又可以往数据寄存器写入下一笔待发送的数据。 之后硬件从MOSI引脚上读取待接收数据的第一bit数据并放入移位寄存器中(移位寄存器由于之前发送了1bit数据,此时正好有一bit位置可以存放收到的数据)。 之后硬件根据在SCK上的时钟信号,会在MISO和MOSI引脚上发送和接收剩下的7bit数据。 之后硬件会将移位寄存器中接收到的8bit数据搬运到接收缓冲器中,并将接收缓冲器满标志置1(RDBF=1),以提醒软件可以通过读取数据寄存器来读取刚刚接收到的这笔数据。

也可以参考下一小节“SPI时序”来理解SPI收发逻辑。

图5 SPI数据接收/发送框图

SPI时序

本节介绍SPI通信时序。 包括全双工和半双工的主/从通信时序。

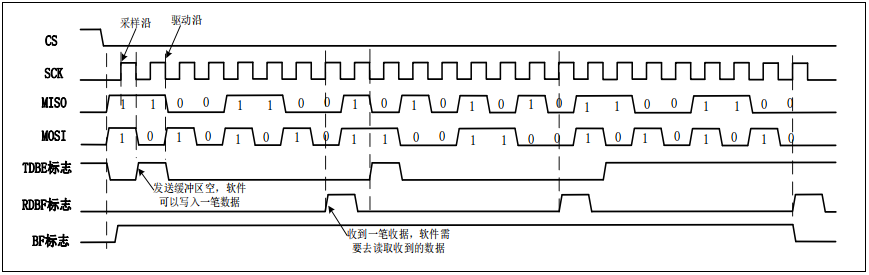

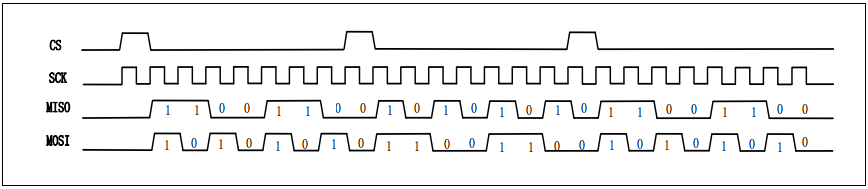

1、SPI全双工时序

以全双工、硬件CS管理、单主单从通信为例。

其中主机端相关配置如下:

MSTEN=1:设备为主机;

SLBEN=0:全双工模式;

CLKPOL=0:SCK空闲输出低电平;

CLKPHA=0:SCK第一个边沿开始进行数据捕获;

FBN=0:帧位个数为8bit;

SWCSEN=0,HWCSOE=1:使用硬件CS管理;

主机发送数据(MOSI):0xAA,0xCC,0xAA;

从机发送数据(MISO):0xCC,0xAA,0xCC。

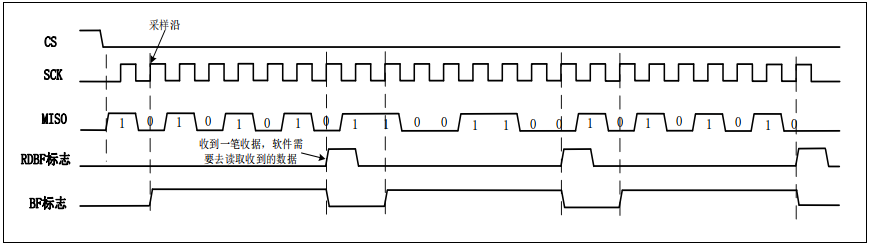

主机端时序见下图 6 :

图6 硬件CS管理-全双工-主机通信时序

其中从机端相关配置如下:

MSTEN=0:设备为从机

SLBEN=0:全双工模式;

CLKPOL=0:SCK空闲低电平

CLKPHA=0:SCK第一个边沿进行数据捕获

FBN=0:帧位个数为8bit

SWCSEN=0:使用硬件CS管理

主机发送数据(MOSI):0xAA,0xCC,0xAA

从机发送数据(MISO):0xCC,0xAA,0xCC

从机端时序见下图 7 :

图7 硬件CS管理-半双工-从机通信时序

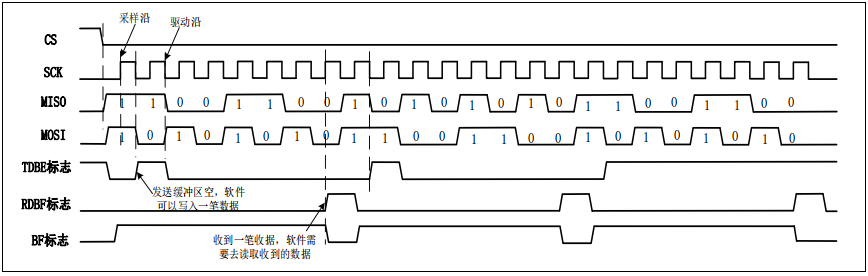

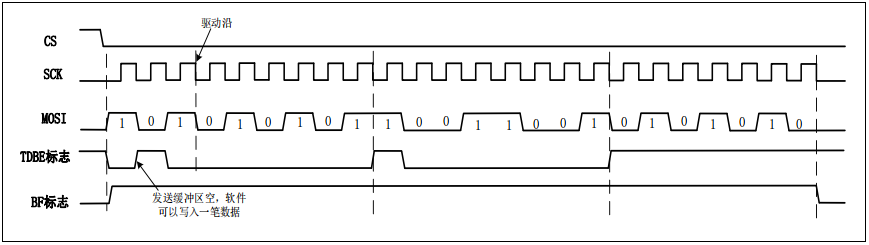

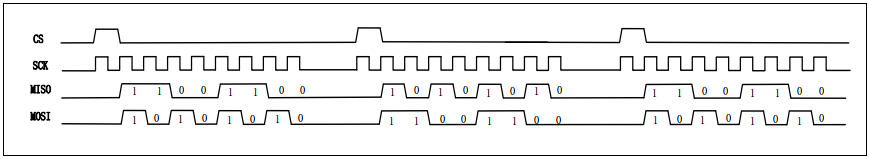

2、SPI半双工时序

半双工时序下,有主机发送、从机接收、主机接收、从机发送4种模式。

1)以半双工、硬件CS管理、主机发送-从机接收通信为例。

其中主机端相关配置如下:

MSTEN=1 :设备为主机;

SLBEN=1 :使能单线双向半双工模式;

SLBTD=1 :发送模式;

CLKPOL=0:SCK空闲输出低电平;

CLKPHA=0:SCK第一个边沿开始进行数据捕获;

FBN=0:帧位个数为8bit;

SWCSEN=0,HWCSOE=1:使用硬件CS管理;

主机发送数据:0xAA,0xCC,0xAA;

主机端时序见下图 8 :

图8 硬件CS管理-半双工-主发时序

其中从机端相关配置如下:

MSTEN=0:设备为从机;

SLBEN=1 :使能单线双向半双工模式;

SLBTD=0 :接收模式;

CLKPOL=0:SCK空闲低电平;

CLKPHA=0:SCK第一个边沿进行数据捕获;

FBN=0:帧位个数为8bit;

SWCSEN=0:使用硬件CS管理;

从机接收数据:0xAA,0xCC,0xAA;

从机端时序见下图 9 :

图9 硬件CS管理-半双工-从收时序

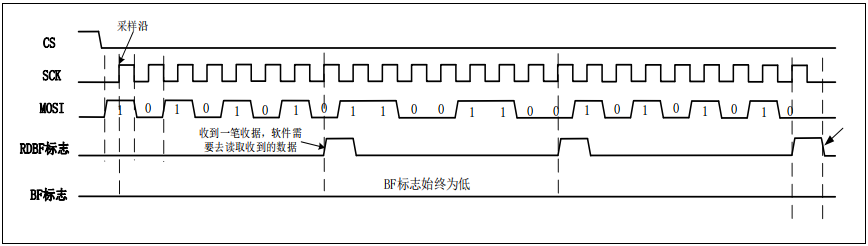

2)以半双工、硬件CS管理、主机接收-从机发送通信为例。

其中主机端相关配置如下:

MSTEN=1 :设备为主机;

SLBEN=1 :使能单线双向半双工模式;

SLBTD=0 :接收模式;

CLKPOL=0:SCK空闲输出低电平;

CLKPHA=0:SCK第一个边沿开始进行数据捕获;

FBN=0:帧位个数为8bit;

SWCSEN=0,HWCSOE=1:使用硬件CS管理;

主机接收数据:0xAA,0xCC,0xAA;

主机端时序见下图10:

此模式下,较为特别的是,SPI主机一旦使能(SPIEN=1),就会连续不断的输出时钟。 因此,主机在接收完需要接收的数据后,需要关闭SPI。 在本例中,接收完连续的3笔数据后,也就是下图10的箭头处,需要关闭SPI,输出多余的时钟。

另外,如下图10,此模式下,BF标志始终为低。

图10 硬件CS管理-半双工-主收时序

其中从机端相关配置如下:

MSTEN=0:设备为从机;

SLBEN=1 :使能单线双向半双工模式;

SLBTD=1 :发送模式;

CLKPOL=0:SCK空闲低电平;

CLKPHA=0:SCK第一个边沿进行数据捕获;

FBN=0:帧位个数为8bit;

SWCSEN=0:使用硬件CS管理;

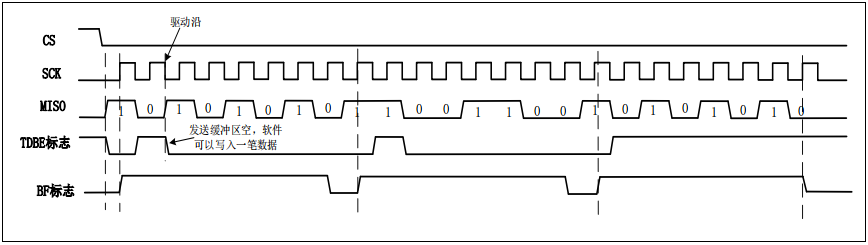

从机发送数据:0xAA,0xCC,0xAA;

从机端时序见下图 11 :

图11 硬件CS管理-半双工-从发时序

SPI数据收发方式

SPI的接收和发送如前文所述,是通过操作数据寄存器来完成的。 而根据操作数据寄存器的方法,SPI有以下3种数据接收发送方式。

轮询方式

轮询方式不需要使能SPI中断和DMA。 只需要在main函数中不断读取STS寄存器,并判断TDBE和RDBF标志是否置起,以确定何时向数据寄存器写入待发送数据,何时从数据寄存器读取接收到的数据。 比较耗费CPU资源,不建议使用此方式。 具体请参考“案例1--SPI全双工轮询方式通信”一节。

中断方式

中断方式需要开启“发送数据缓冲器空中断使能”和“接收数据缓冲器满中断使能”,即设置TDBEIE=1,RDBFIE=1。 并配置和使能SPI中断。 之后在SPI中断里进行数据的发送和接收,避免了轮询方式的等待耗时,占用CPU资源相对较少。 具体请参考“案例4--SPI半双工中断方式通信”或“案例5--SPI半双工中断方式通信--加收发切换”一节。

DMA方式

DMA方式需要开启SPI的DMA接收/发送功能(DMAREN=1,DMATEN=1)。 并配置DMA通道映射到SPI和使能DMA。 之后的接收和发送均由DMA完成,收/发过程不再需要软件参与,不占用CPU资源。 具体请参考“案例2--SPI全双工DMA方式通信”一节。

时钟控制器

SPI协议采用同步传输。 作主机时,需要时钟控制器产生通信时钟用于SPI接口的数据收发,并且需要将该通信时钟通过SCK引脚输出给从机,用于从机的数据收发; 作从机时,需要外部提供通信时钟,从SCK引脚输入到SPI接口内部作为通信时钟使用。 对用户而言,可软件配置的主要有极性、相位、分频系数三个参数。

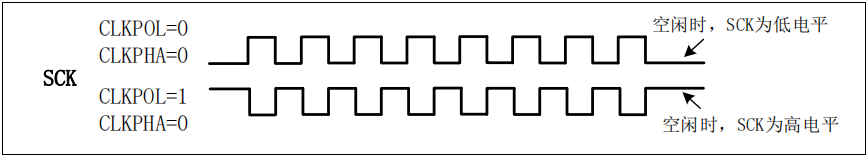

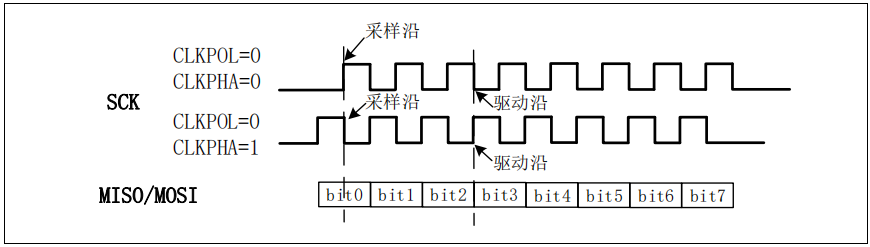

极性

SPI时钟极性,即空闲时SCK引脚输出的电平。 通过配置CLKPOL位来选择SPI时钟极性。

如下图12:CLKPOL=0时,SCK空闲为低电平; CLKPOL=1时,SCK空闲为高电平。

图12 时钟极性对比

相位

SPI时钟相位,即SPI数据捕获边缘。 通过配置CLKPHA位来选择SPI时钟极性。

如下图13:

CLKPHA=0时,第一个边沿为捕获采样边沿。 在本例中(CLKPOL=0),也就是上升沿为采样沿; 相对的,本例中下降沿为驱动沿。

CLKPHA=1时,第二个边沿为捕获采样边沿。 在本例中(CLKPOL=0),也就是下降沿为采样沿; 相对的,本例中上升沿为驱动沿。

图13 时钟相位对比

分频系数

SPI时钟是从APB时钟分频得到的,通过配置MDIV[3:0]和MDIV3EN来选择需要的分频系数,以确定SPI时钟。 分频系数仅主机配置有效。 从机需要外部提供时钟,因此此项配置无效。

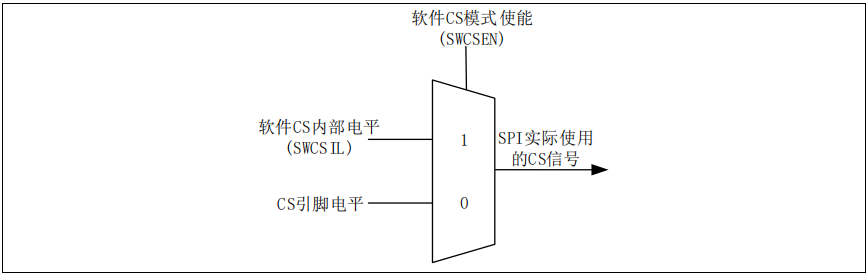

CS管理

SPI CS包含硬件和软件管理两种模式,又根据主机/从机的不同,有不同的配置和应用场景。

在CS为输入模式时(HWCSOE=0),如下图14,主机和从机均通过SWCSEN位来选择SPI实际使用的CS信号来自软件设置(SWCSIL)还是外部CS引脚电平。

在CS为输出模式时(HWCSOE=1),软件CS模式相关配置无效。

图14 SPI数据接收/发送框图

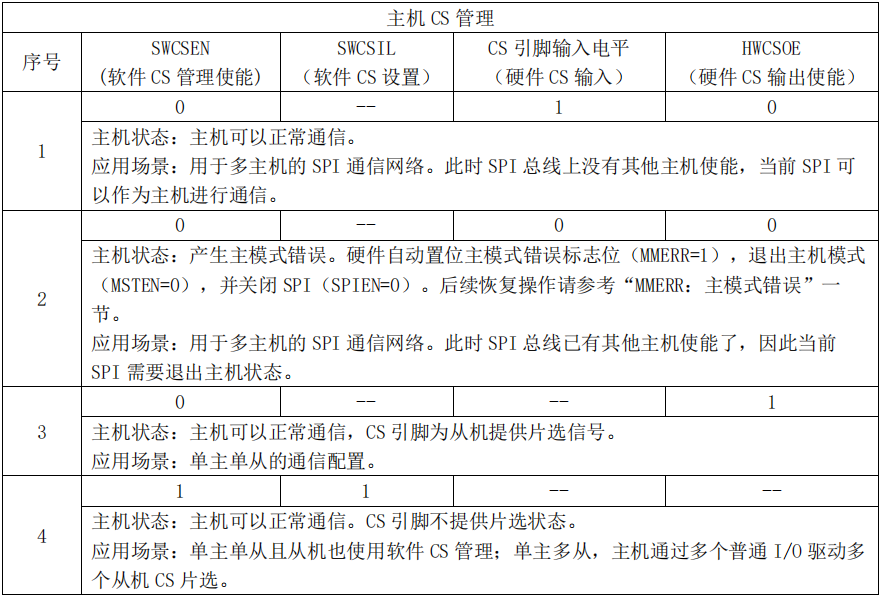

以下分别列出了主机和从机在不同的CS管理模式下的状态和应用场景。

主机CS管理:

下表1列出了几种主机CS管理的配置及应用场景。

表1 SPI主机CS管理配置

注:“--”表示此项配置无效,建议保持默认配置。

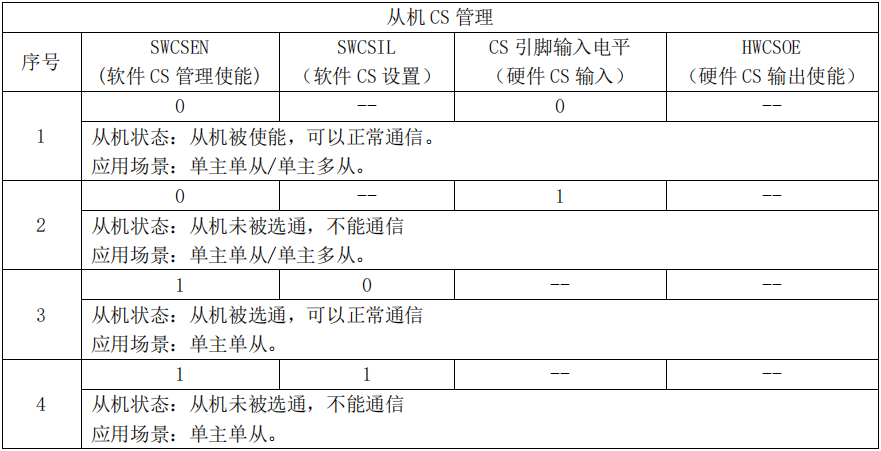

从机CS管理:

下表2列出了从机CS管理的几种配置和应用场景。 其中,从模式下HWCSOE配置无效,该位只在主模式下有效。

表2 SPI从机CS管理配置

注:“--”表示此项配置无效,建议保持默认配置。

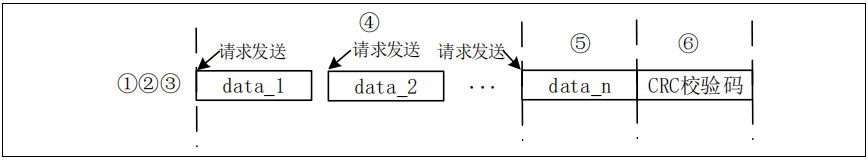

CRC校验

AT32 SPI具有独立的发送和接收CRC计算单元,用户可通过软件配置使能此功能。 使能CRC校验之后:硬件会对发送的数据进行CRC计算,并将计算得到的CRC校验码放在SPI_TCRC寄存器中,CRC校验码紧接在数据之后发送; 且硬件会在接收一笔数据时对接收到的数据进行CRC计算,并将计算得到的CRC校验码放在SPI_RCRC寄存器中,硬件会在一笔连续的数据接收完成后将最后接收到的CRC校验码与SPI_RCRC寄存器中的校验码进行比较,如果不符,CRC校验错误位(CCERR)会置起,若使能了错误中断(ERRIE=1),将会产生中断。

另外,SPI通信方式使用DMA和使用轮询/中断方式时,CRC功能的软件操作步骤有区别,如下:

轮询 /中断方式:

①配置CRC多项式:配置SPI_CPOLY寄存器和需要通信的SPI一致(默认值为0x0007);

②使能CRC功能:CCEN=1;

③使能SPI:SPIEN=1;

④发送待发送的数据data_1~data_n;

⑤请求发送CRC校验码:NTC=1。

注:NTC置1的时间参考下图15的⑤段,需要在最后一笔数据(data_n)写入数据寄存器到发送完成之间。 实际编写软件代码时,建议在data_n写入数据寄存器之后立即将NTC置1。

⑥硬件自动在data_n发送完成后立即发送CRC校验码(此时无需软件参与)。

轮询方式使用CRC功能可参考“案例6--SPI CRC功能使用”。

图15 CRC使用流程(轮询/中断方式)

DMA方式:

SPI在使用DMA方式通信时,不需要软件代码去设置请求发送CRC校验码,即不需要去置位NTC位。 具体步骤如下:

①配置DMA:请参考“案例2--SPI全双工DMA方式通信”的DMA配置部分;

②配置CRC多项式:配置SPI_CPOLY寄存器和需要通信的SPI一致(默认值为0x0007);

③使能CRC功能:CCEN=1;

④使能SPI:SPIEN=1;

⑤数据及CRC接收完成后需关闭SPI和DMA,之后再开启,准备下一次通信。

TI模式(TI SSP协议)

AT32 SPI接口支持TI SSP协议,即TI模式。 用户可以通过将TIEN位置1来使能TI模式。

使能TI模式后,SPI接口将按照TI协议要求产生时钟SCK,和片选信号CS。 也就是CS软/硬件管理相关控制位、时钟极性/相位相关控制位配置无效,请保持默认设置。 使能TI模式后,帧格式(8/16bit)配置、CRC校验、DMA等功能仍然可以使用。

TI模式下,连续和不连续通信稍有区别。 连续通信时,只有第一笔数据发送时有一个dummy CLK; 不连续通信时,每笔数据都有一个dummy CLK。 参考下图16和图17。

TI模式连续通信时序图见下图16。 主机发送数据(MOSI):0xAA,0xCC,0xAA; 从机发送数据(MISO):0xCC,0xAA,0xCC。

图16 TI模式连续通信时序图

TI模式不连续通信时序图见下图17。 主机发送数据(MOSI):0xAA,0xCC,0xAA; 从机发送数据(MISO):0xCC,0xAA,0xCC。

图17 TI模式不连续通信时序图

注:AT32只有部分型号支持TI模式。 AT32F425/F435/F437等型号支持TI模式,AT32F403/F403A/F407/F413/F415等型号不支持TI模式。 具体请参考各型号的RM。

SPI错误

AT32的SPI有4种错误标志。 这4种错误标志共用一个错误中断使能位(ERRIE)。 也就是当ERRIE=1时,产生以下4种错误的任一错误就会进入SPI错误中断。

CSPAS--CS脉冲异常置位标志

在TI模式下,当SPI作从机使用时,SPI会在数据传输期间侦测非预期的CS脉冲,当发生CS脉冲异常置位错误,CSPAS被硬件置1,如果开启了错误中断使能(ERRIE=1),则会产生错误中断。 之后可以通过软件读SPI_STS清除该位。 当侦测到CS脉冲异常时,为避免数据错误,软件应当关闭SPI从机,重新配置SPI主机,再打开SPI从机以重新开始通信。

注:仅在TI模式下,CSPAS错误标志才有效。

ROERR-- 接收器溢出错误标志

当SPI数据寄存器已暂存一笔待读数据时,又收到一笔新数据,则会发生接收器溢出错误,ROERR被硬件置1,如果开启了错误中断使能(ERRIE=1),则会产生错误中断。 发生溢出错误之后,SPI_DT寄存器存放的是最早收到的那笔数据,发生溢出错误之后收到的数据都被丢弃。

之后依次读取SPI_DT寄存器和SPI_STS寄存器可清除该标志位。

MMERR-- 主模式错误标志

参考“CS管理”一节,当SPI主机为CS输入模式且CS引脚输入低电平时,会产生主模式错误,MMERR位会被硬件置1,且硬件会强制SPI进入从机模式(MSTEN清0)并关闭SPI(SPIEN清0)。 如果开启了错误中断使能(ERRIE=1),则会产生错误中断。

清除MMERR标志位并从错误状态恢复请严格按照以下步骤执行:

①拉高CS引脚电平;

②执行一次对SPI_STS寄存器的读或写操作;

③执行一次对SPI_CTRL1寄存器的写操作; (不需要改变SPI_CTRL1的值,只需要写这个动作)

④之后硬件会自动清除MMERR标志(此步骤不需要软件代码参与);

⑤之后软件可根据需要重新配置主/从模式和使能SPI。

CCERR--CRC****校验错误标志

当使能了CRC功能后,如果接收到的CRC校验码(发送方发送的校验码)和SPI_RCRC的校验码(接收方根据接收到的数据计算的校验码)不符,则硬件将CCERR位置1,如果开启了错误中断使能(ERRIE=1),则会产生错误中断。

由于发生了CRC校验错误,软件程序应当丢弃之前接收到的一笔数据,并重新通信。 软件对CCERR位写0可清除该标志位。

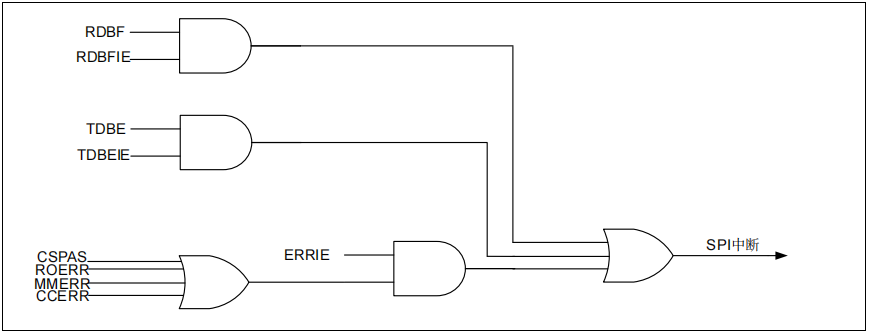

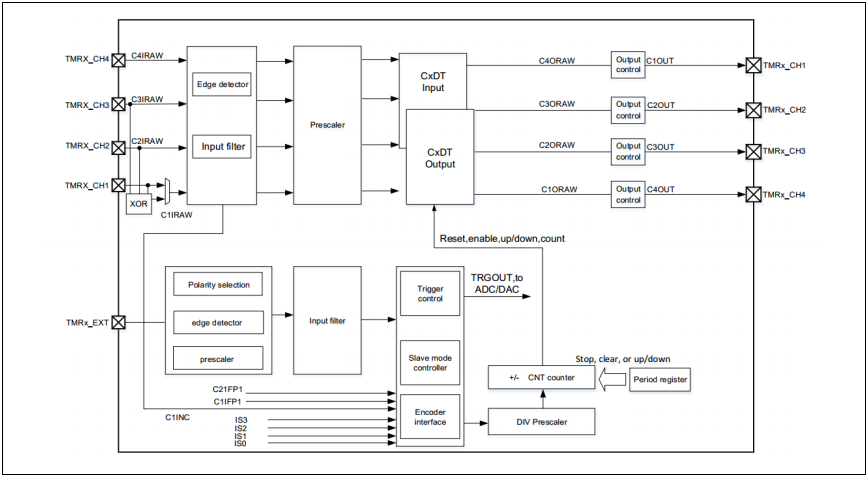

SPI中断

如下图18,SPI有一个全局中断向量。 SPI中断有三个中断源:接收缓冲器满、发送缓冲器空、通信错误(详见上一节“SPI错误”)。 这三个中断源分别有对应的使能位。

下图中,3个中断使能位定义如下:

RDBFIE:接收数据缓冲器满中断使能

TDBEIE:发送数据缓冲器空中断使能

ERRIE:错误中断使能

下图中,5个标志位定义如下:

ROERR:接收器溢出错误

MMERR:主模式错误

CCERR:CRC校验错误

RDBF:接收数据缓冲器满

TDBE:发送数据缓冲器空

图18 SPI中断示意

I2S功能介绍

I2S硬件接口

I2S接口定义如下:

WS:声道选择。 由主机输出,从机输入。

CK:时钟。 由主机输出,从机输入。

MCK:主时钟输出(可选)。 在通讯期间可提供频率固定为256倍Fs的外设主时钟,仅在作为主机时有效。

SD:数据。 主机/从机接收或发送数据均通过这个引脚。

以下是常见的I2S通信接线方式。

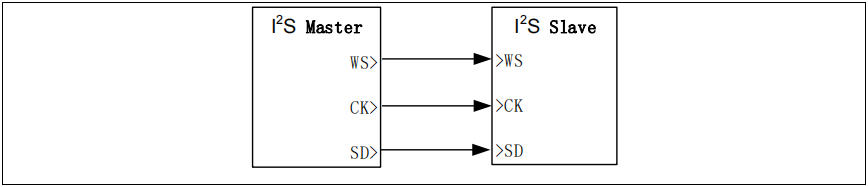

如下图19,是I2S主发从收的接线示意图。

图19 I2S主发从收通信接线示意

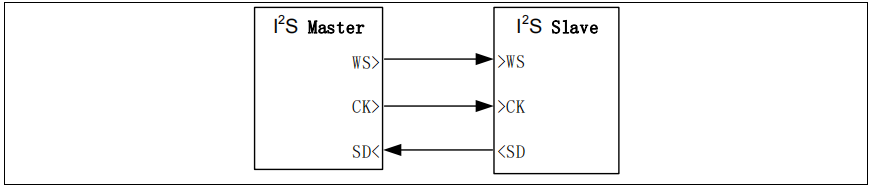

如下图20,是I2S主收从发的接线示意图。

图20 I2S主收从发通信接线示意

I2S数据接收和发送

I2S数据收发模块和上文的SPI共用数据寄存器和DMA映射,如上图5中的接收/发送缓冲器、移位寄存器也都是共用的,因此软件代码操作类似,请参考下文的I2S案例一节。 不过SPI默认是全双工,而I2S默认是半双工。 AT32也为用户提供I2S全双工功能,后文I2S全双工一节详细介绍。

I2S音频协议

AT32的I2S支持以下4种标准协议:

飞利浦标准:STDSLE=0b00;

高字节对齐标准(左对齐):STDSLE=0b01;

低字节对齐标准(右对齐):STDSLE=0b10;

PCM标准:STDSLE=0b11。

其中PCM标准又分为:

1、PCM长帧同步:PCMFSSEL=1;

2、PCM短帧同步:PCMFSSEL=0。

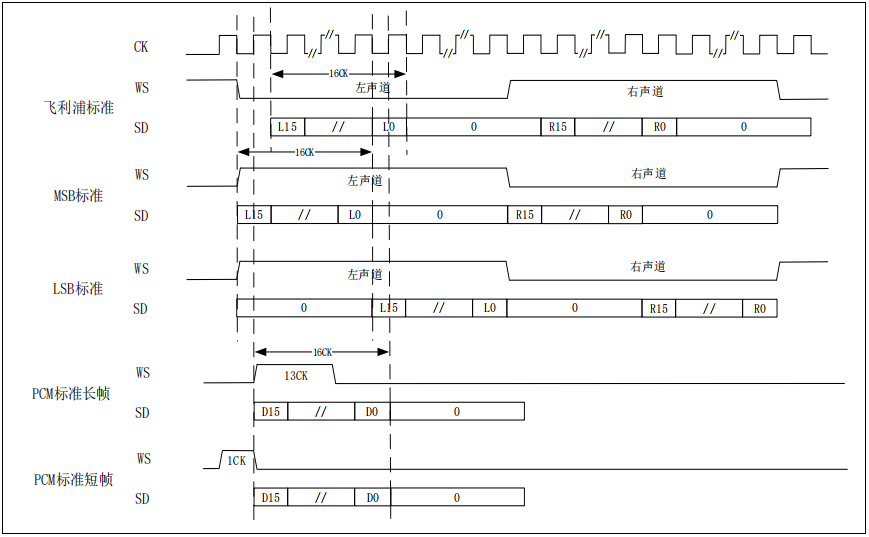

下图21在“16位数据-32位声道格式”,I2S时钟极性为低(I2SCLKPOL=0)条件下对比了几种音频标准一帧数据的通信时序。

飞利浦模式下:WS为低电平表示正在传输的声道为左声道,WS为高电平表示正在传输的声道为右声道。 数据左对齐,即高位对齐,低位的16个bit被硬件填充为0。

MSB标准下:WS为高电平表示正在传输的声道为左声道,WS为低电平表示正在传输的声道为右声道。 数据左对齐,即高位对齐,低位的16个bit被硬件填充为0。

LSB标准下:WS为高电平表示正在传输的声道为左声道,WS为低电平表示正在传输的声道为右声道。 数据右对齐,即低位对齐,高位的16个bit被硬件填充为0。

注:LSB标准下,数据发送顺序还是高位在前。

PCM标准长帧下:没有左右声道之分,WS的脉冲代表同步信号而不是左右声道。 WS脉冲长度为13个CK长度。

PCM标准短帧下:没有左右声道之分,WS的脉冲代表同步信号而不是左右声道。 WS脉冲长度为1个CK长度。

图21 I2S各音频标准时序对比

I2S帧格式

AT32的I2S支持3种数据位个数选择:

16位:I2SDBN=0b00

24位:I2SDBN=0b01

32位:I2SDBN=0b10

AT32的I2S支持2种声道位个数选择:

16位:I2SDBN=0

32位:I2SDBN=1

数据位个数和声道位个数组合有以下4种帧格式:

①16位数据-16位声道格式:I2SDBN=0b00,I2SDBN=0;

②16位数据-32位声道格式:I2SDBN=0b00,I2SDBN=1;

③24位数据-32位声道格式:I2SDBN=0b01,I2SDBN=1;

④32位数据-32位声道格式:I2SDBN=0b10,I2SDBN=1;

上述的第②、③帧格式中,由于声道位个数>数据位个数。 此时硬件会自动将多余的声道位填充为0。 可参考上图21中,“16位数据-32位声道格式”的时序。

上述的①、②帧格式,在接收/发送数据时,仅需要读取/写入一次16bit的DT寄存器; 而③、④帧格式,在接收/发送数据时,需要读取/写入两次16bit的DT寄存器。

I2S时钟控制器

I2S 采样率( Fs )

常见的音频的采样频率有:192KHz、96kHz、48kHz、44.1kHz、32kHz、22.05kHz、16kHz、11.025kHz、8kHz等。 而实际上AT32的I2S可以产生以上范围内的任何采样率。

例如采样率为192K,则表示每秒可传输192K帧音频数据。 对于飞利浦/MSB/LSB标准而言,一帧音频数据包含左、右通道两笔16/32bit的数据; 对于PCM标准而言,一帧数据仅包含一笔16/32bit的数据。

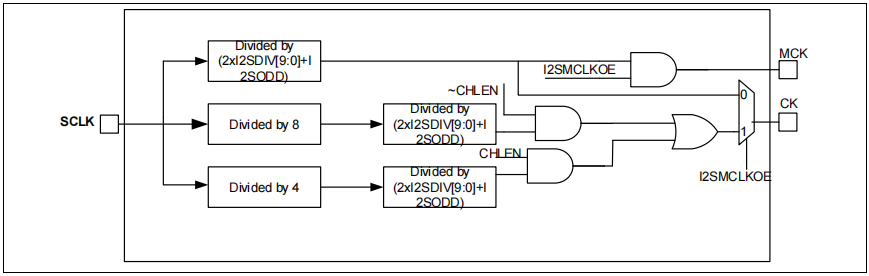

I2S 时钟( CK )和主时钟( MCK )

如下图22,I2S的时钟从系统时钟SCLK分频得来。 不过使用I2S时仍然需要使能挂载在APB时钟总线上的SPI接口时钟(SPIxEN=1),以用于I2S逻辑控制器等。

当需要输出主时钟(I2SMCLKOE=1),声道位个数为16bit(I2SDBN=0)时:

Fs=SCLK/[(162)((2*I2SDIV)+I2SODD)*8];

当需要输出主时钟(I2SMCLKOE=1),声道位个数为32bit(I2SDBN=1)时:

Fs=SCLK/[(322)((2*I2SDIV)+I2SODD)*4];

当不需要输出主时钟(I2SMCLKOE=0),声道位个数为16bit(I2SDBN=0)时:

Fs=SCLK/[(162)((2*I2SDIV)+I2SODD)];

当不需要输出主时钟(I2SMCLKOE=0),声道位个数为32bit(I2SDBN=1)时:

Fs=SCLK/[(322)((2*I2SDIV)+I2SODD)];

图22 I2S时钟

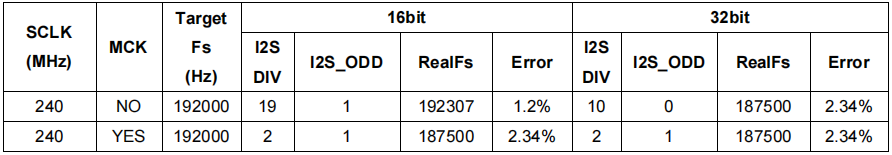

如下表3,示例了系统时钟为240MHz时,配置192K的采样率推荐的I2S时钟配置方案。

表3 I2S时钟配置方案示例

I2S全双工

AT32F403A/F407/F435/F437/F425等型号支持I2S全双工,AT32F403/F413/F415/F421等型号不支持I2S全双工,具体请参考对应型号RM文档。 不同型号MCU的I2S全双工实现方式也有所区别,本文会分别介绍AT32F403A/F407/F435/F437和AT32F425的I2S全双工功能。

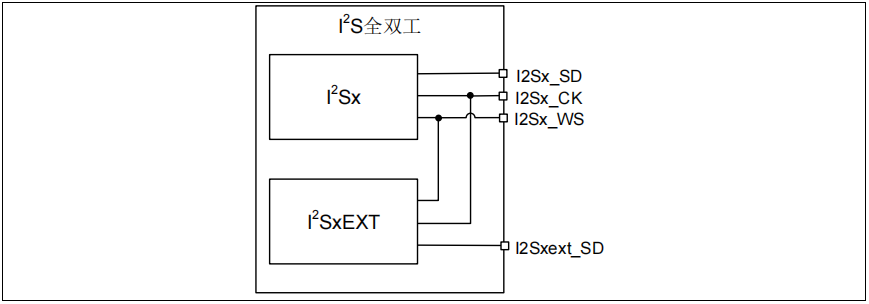

AT32F403A/F407/F435/F437的I2S****全双工

AT32F403A/F407/F435/F437为了支持I2S全双工模式,额外例化了两个I2S模块(I2S2EXT,I2S3EXT)。 I2S2可与I2S2EXT组合在一起支持全双工模式,I2S3可与I2S3EXT组合在一起支持全双工模式。 代码可参考“案例3—AT32F403A/F407/F435/F437 I2S全双工DMA方式通信”。

在I2Sx可与I2SxEXT组成全双工模块时,I2Sx可配置为主或从模式,I2SxEXT只能配置为从模式。 I2SxEXT共享I2Sx的CK和WS,对应的有以下几种配置方式:

I2Sx主发(OPERSEL=0b10); I2SxEXT从收(OPERSEL=0b01);

I2Sx主收(OPERSEL=0b11); I2SxEXT从发(OPERSEL=0b00)。

I2Sx从发(OPERSEL=0b00); I2SxEXT从收(OPERSEL=0b01);

I2Sx从收(OPERSEL=0b01); I2SxEXT从发(OPERSEL=0b00)。

注:I2S2EXT和I2S3EXT只用于I2S全双工模式,而不能单独使用。

图23 I2S全双工结构图

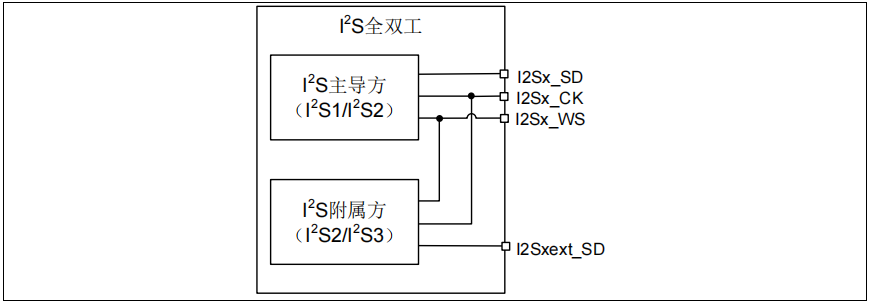

AT32F425的I2S全双工

AT32F425的I2S全双工实现方式和AT32F403A/F407/F435/F437不同。 AT32F425可以通过设置SCFG_CFG2寄存器中的I2S_FD将两个SPI组合在一起实现I2S全双工。 代码可参考“案例4—AT32F425 I2S全双工DMA方式通信”。 CK和WS由I2S主导方提供,附属方的CK和WS对应引脚可以释放给其他功能使用。 根据I2S_FD配置,有以下几种组合方式:

I2S_FD=0b00:I2S1~3各自独立半双工工作;

I2S_FD=0b01:I2S1和I2S3组成全双工模式,其中I2S1为主导方,I2S3为附属方。

I2S_FD=0b10:I2S2和I2S3组成全双工模式,其中I2S2为主导方,I2S3为附属方。

I2S_FD=0b11:I2S1和I2S2组成全双工模式,其中I2S1为主导方,I2S2为附属方。

图24 I2S全双工结构图

I2S错误

ROERR-- 接收器溢出错误标志

此错误标志和SPI一样,请参考前文“2.9.2 ROERR--接收器溢出错误标志”。

TUERR-- 发送器欠载错误标志位

在I2S从发模式下,如果在CK上检测到了数据驱动沿,但新的发送数据并没有被写入数据寄存器,则会产生发送器欠载错误,此时硬件会将TUERR位置1。 软件读SPI_STS寄存器可清除该标志位。 此错误标志仅使用I2S时有效。

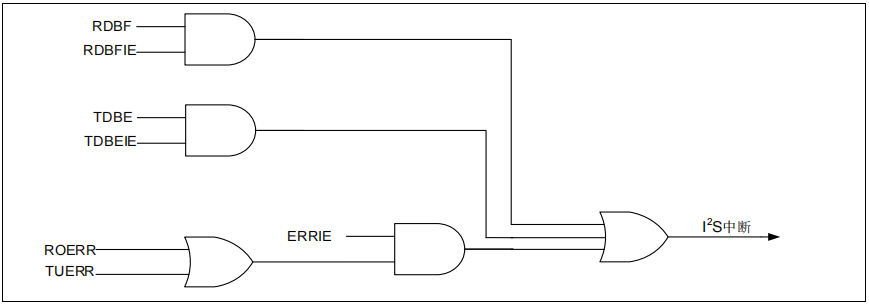

I2S中断

I2S和SPI共用一个全局中断向量,即下图25的“I2S中断”和上图18中的“SPI中断”共用同一个中断向量。 I2S中断有三个中断源:接收缓冲器满、发送缓冲器空、通信错误(详见上一节“I2S错误”)。 这三个中断源分别有对应的使能位。

下图中,3个中断使能位定义如下:

RDBFIE:接收数据缓冲器满中断使能(和SPI一样)

TDBEIE:发送数据缓冲器空中断使能(和SPI一样)

ERRIE: 错误中断使能(和SPI一样)

下图中,4个标志位定义如下:

ROERR:接收器溢出错误(和SPI一样)

TUERR:发送器欠载错误(仅I2S有这个错误标志)

RDBF:接收数据缓冲器满(和SPI一样)

TDBE:发送数据缓冲器空(和SPI一样)

图25 I2S中断示意

SPI案例

注:所有project都是基于keil5而建立,若用户需要在其他编译环境上使用,请参考

AT32xxx_Firmware_Library_V2.x.xprojectat_start_xxx emplates中各种编译环境(例如IAR6/7,keil4/5)进行简单修改即可。

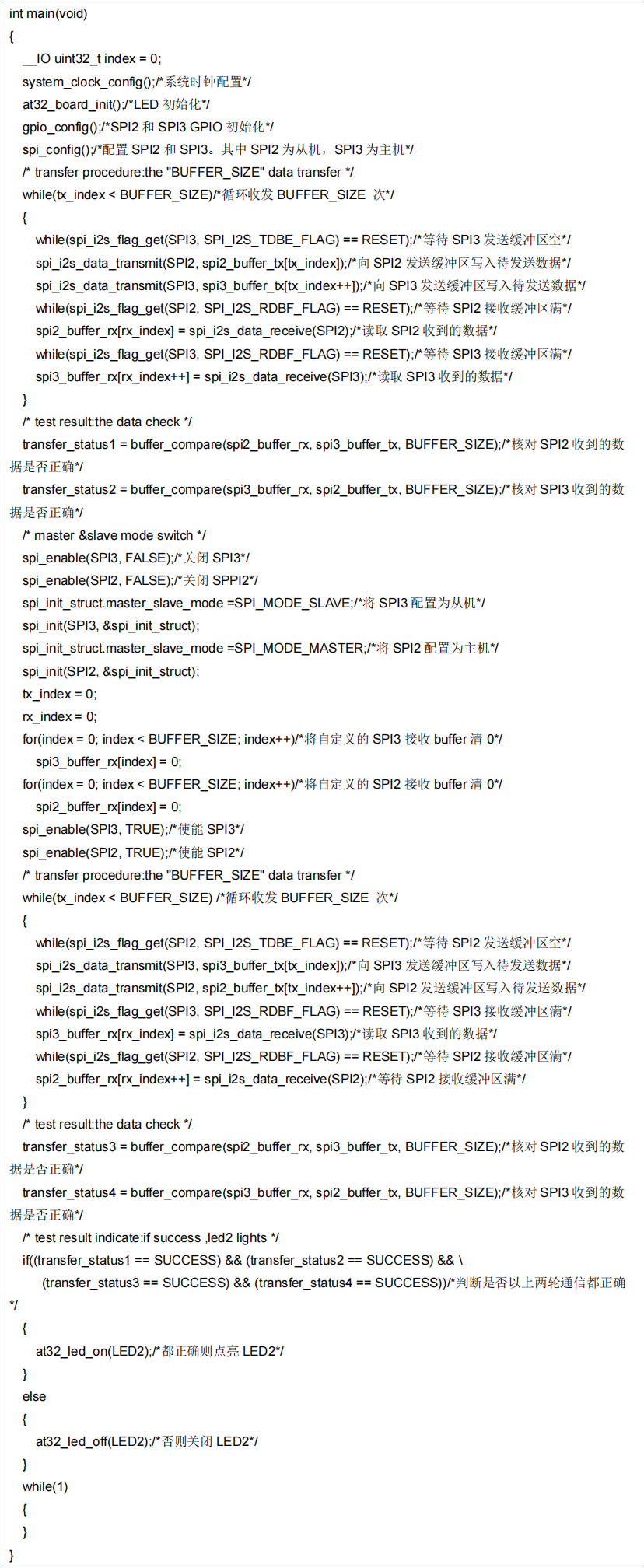

案例1-SPI全双工轮询方式通信

功能简介

实现SPI2和SPI3之间的全双工轮询通信。 接线如下:

SPI2 SPI3

PD1(短短板)<--->PC10(短单)

PC2(味噌)<--->PC11(味噌)

PD4(莫西)<--->PC12(莫西)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesspifullduplex_polling

软件设计

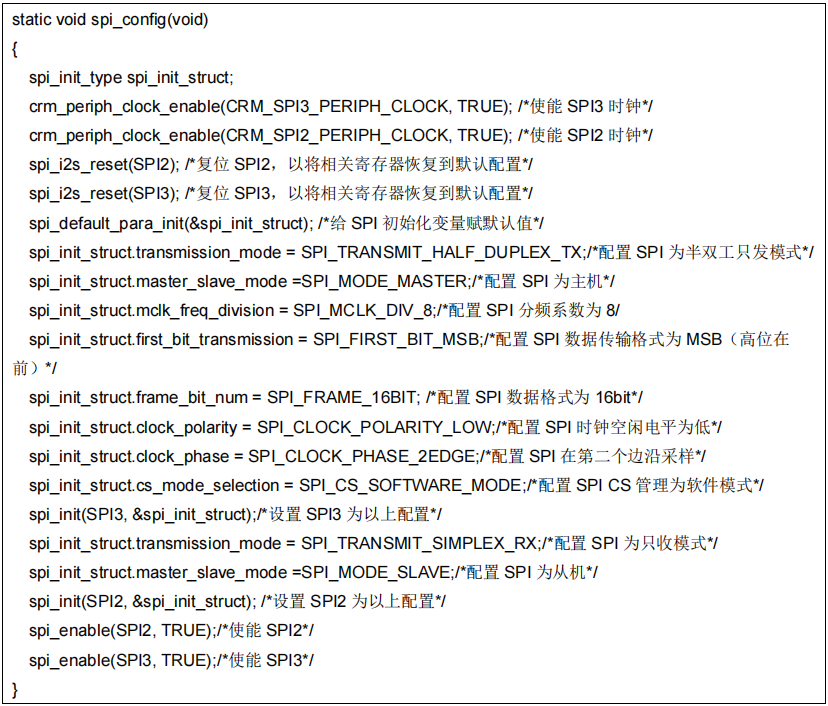

1)配置流程

配置SPI2和SPI3对应的GPIO;

配置SPI2和SPI3通信配置;

开始轮询通信。

2)代码介绍

main函数代码描述

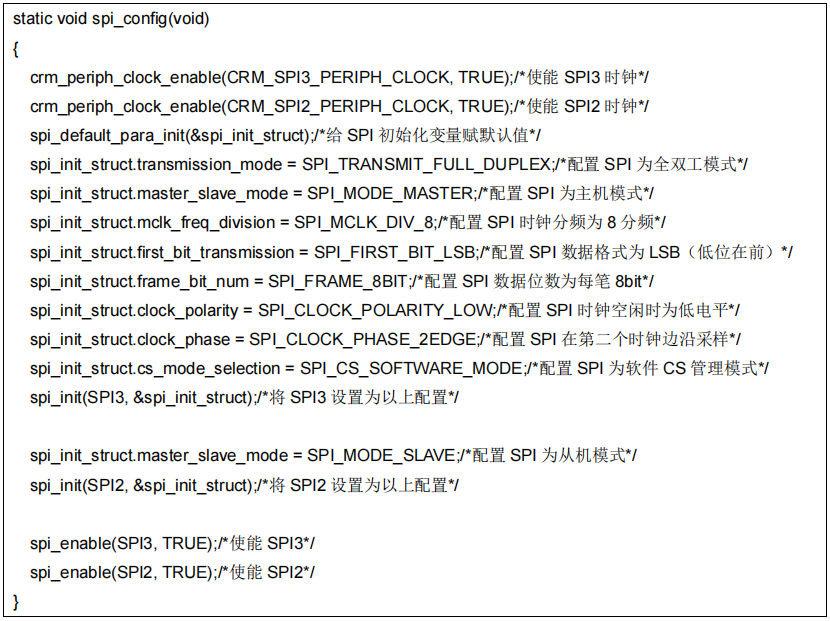

SPI通信配置函数代码描述

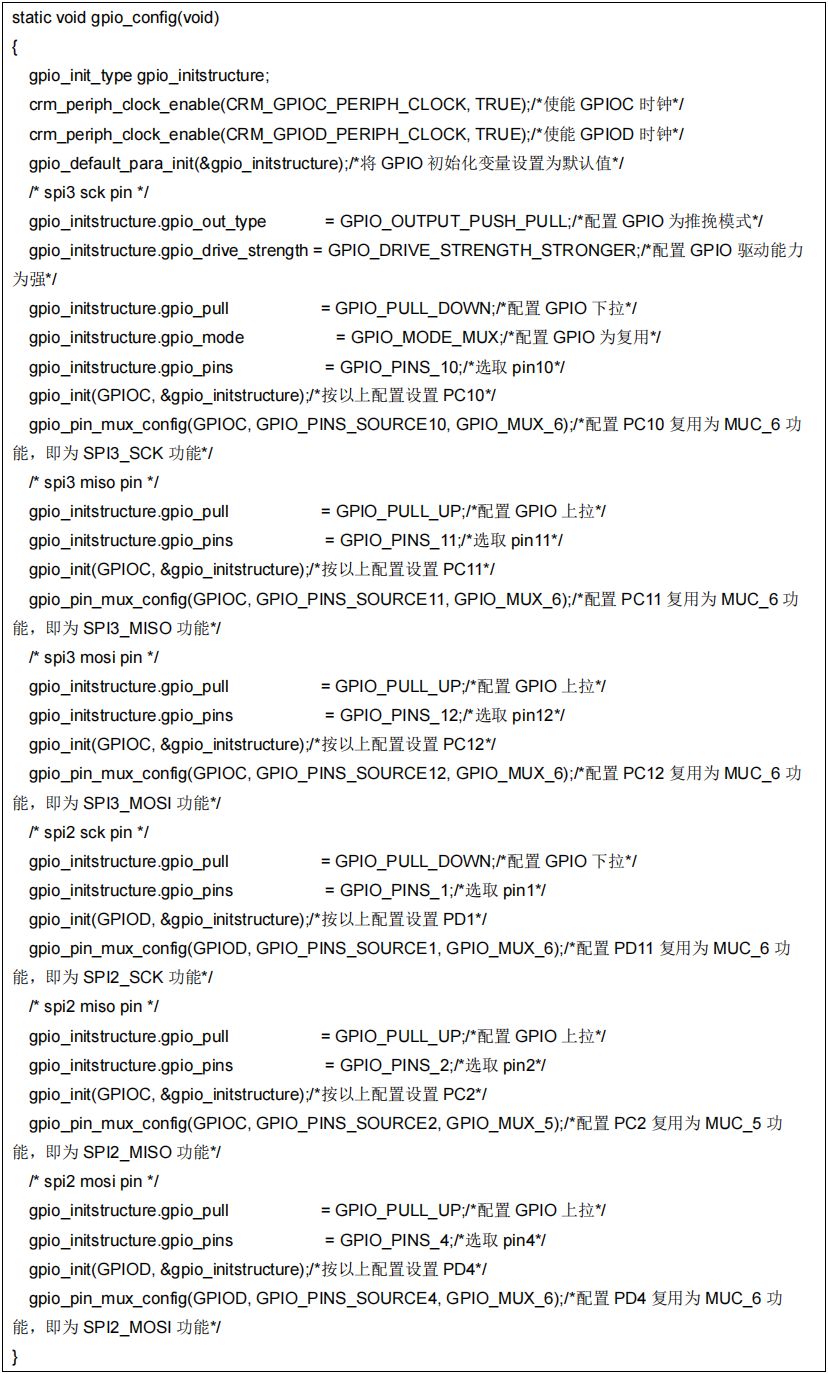

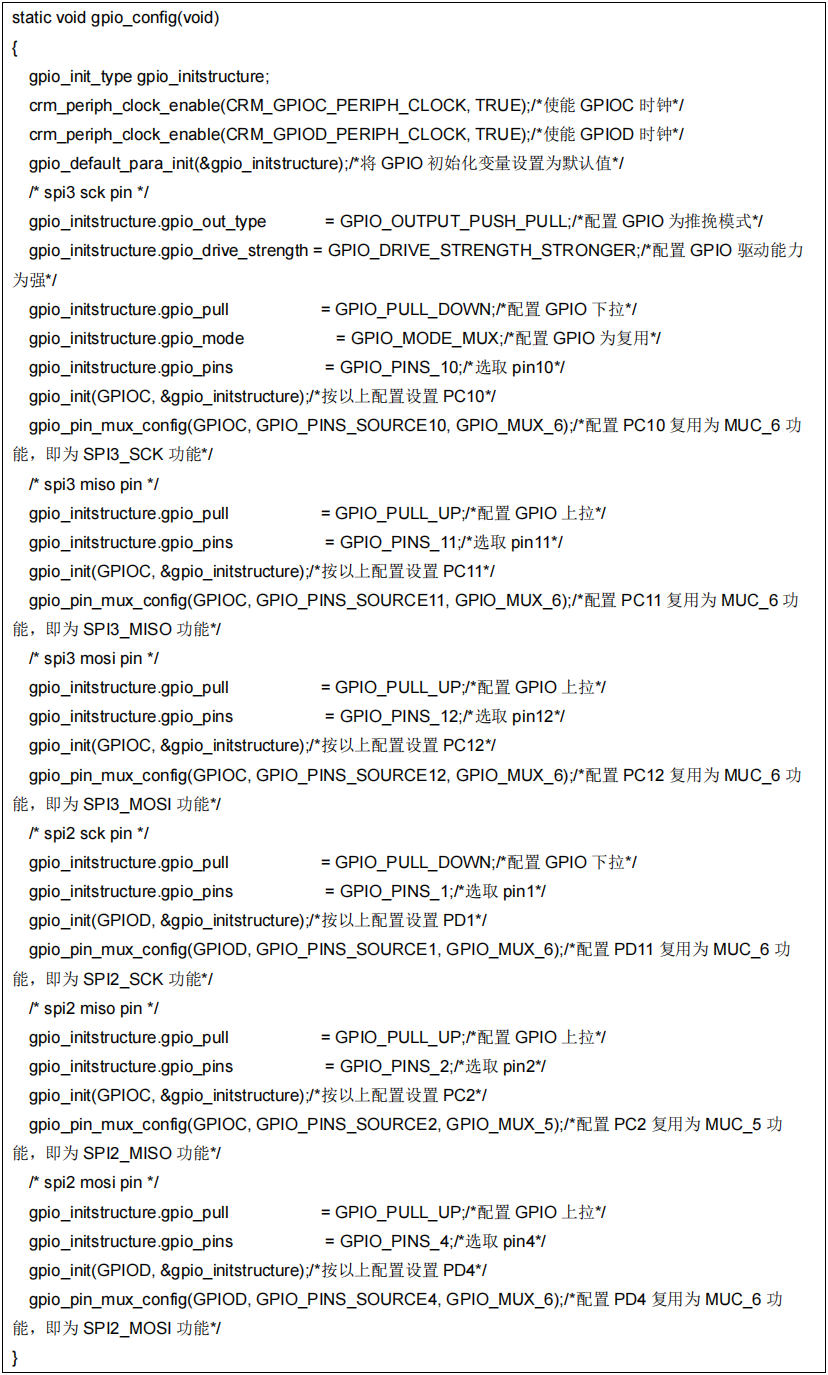

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

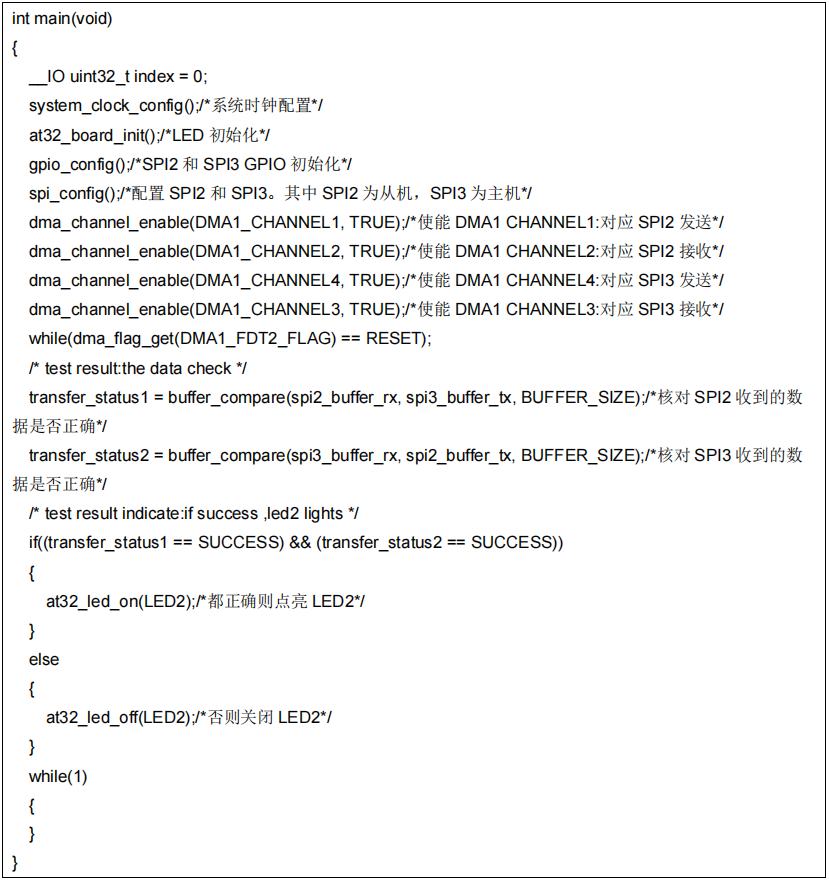

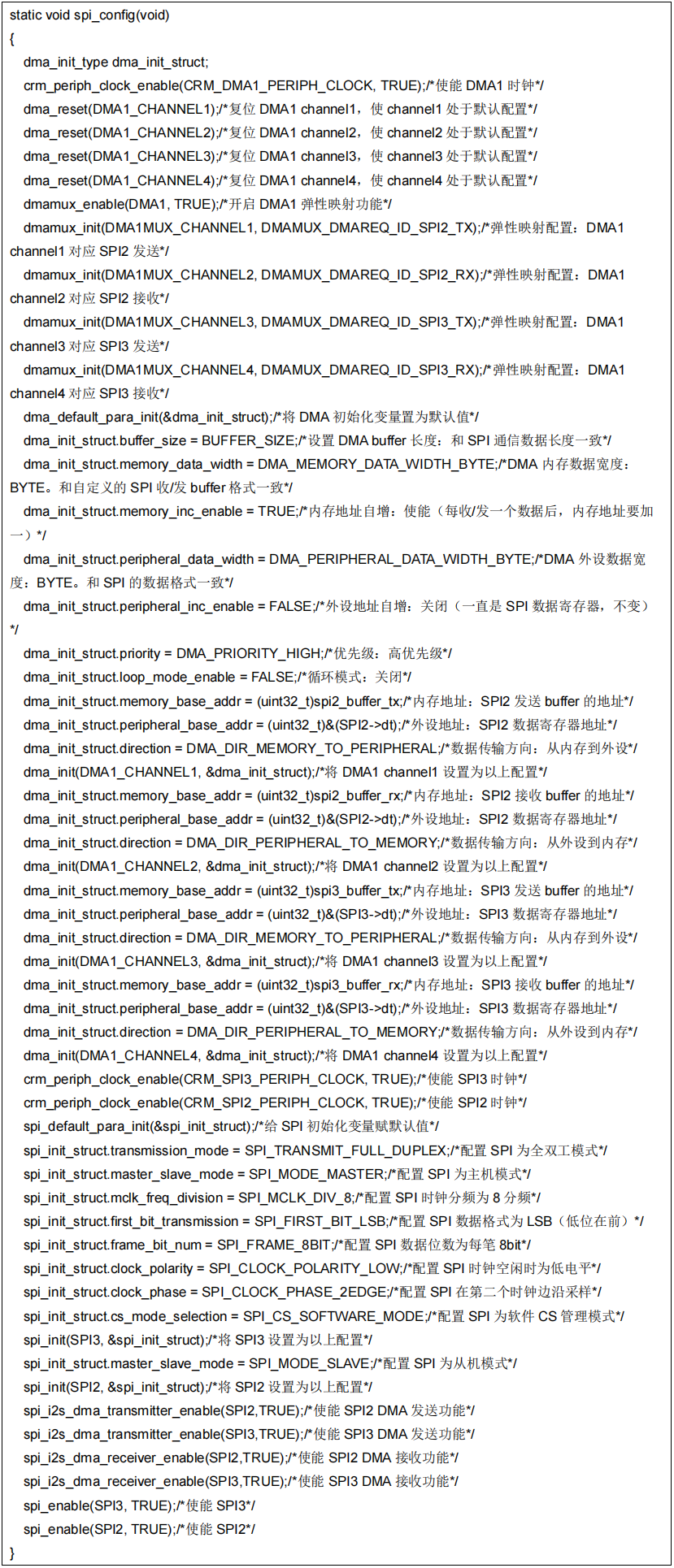

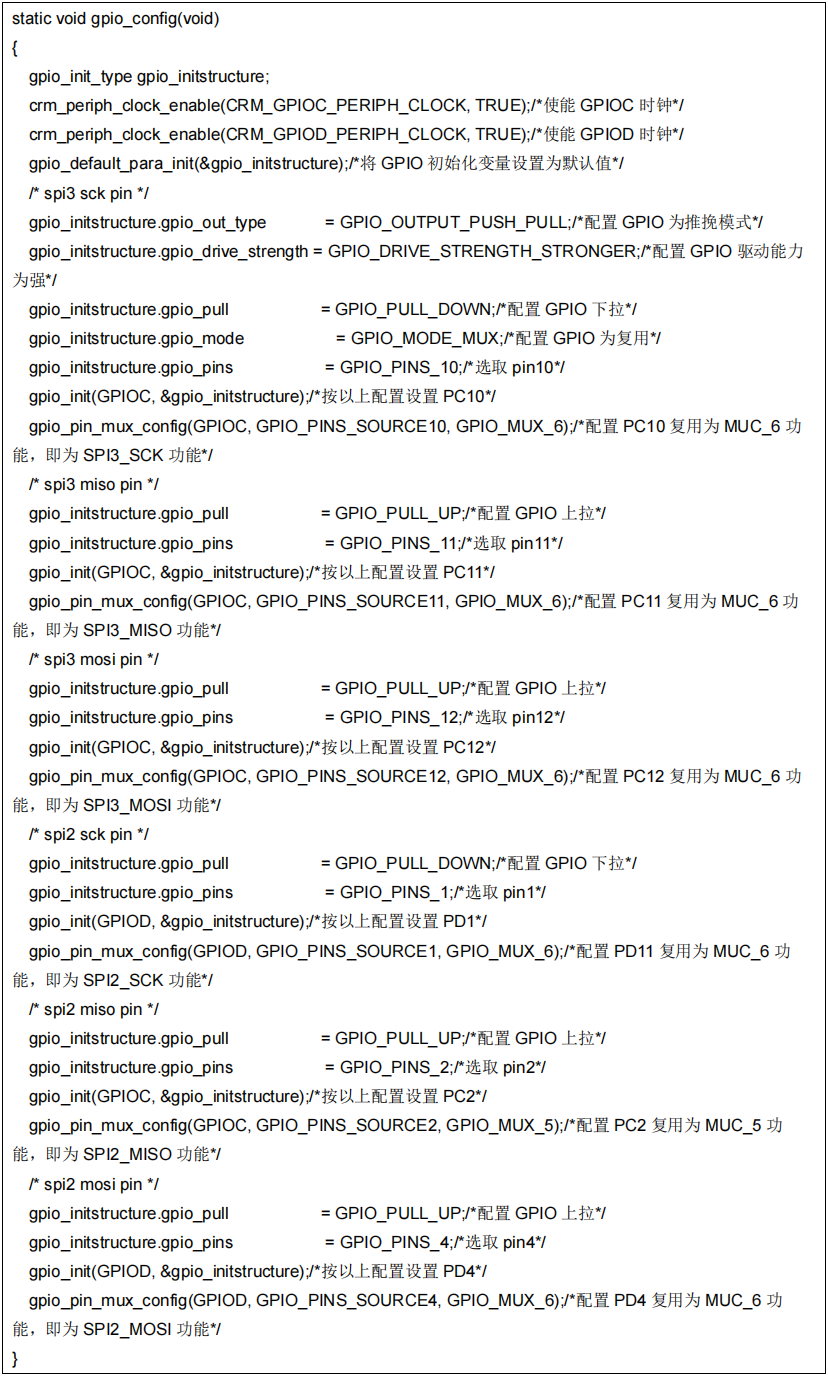

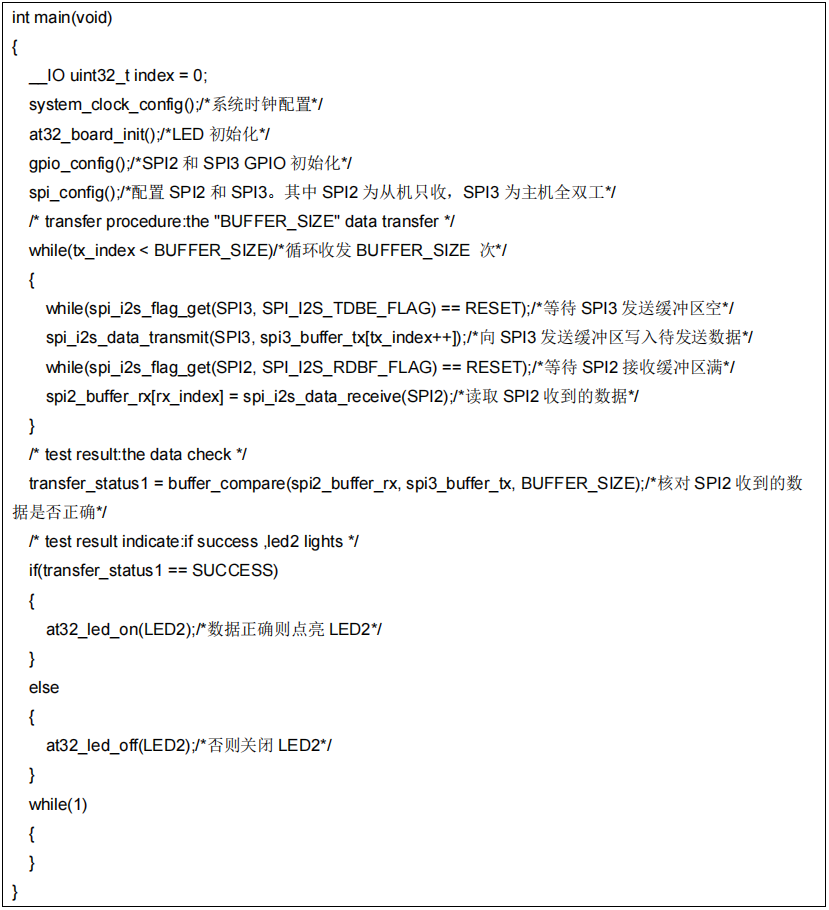

案例2-SPI全双工DMA方式通信

功能简介

实现SPI2和SPI3之间的全双工DMA通信。 接线如下:

SPI2 SPI3

PD1(短短板)<--->PC10(短单)

PC2(味噌)<--->PC11(味噌)

PD4(莫西)<--->PC12(莫西)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesspimotorola_fullduplex_dma

软件设计

1)配置流程

配置SPI2和SPI3对应的GPIO;

配置SPI2和SPI3的通信配置和DMA配置;

开始DMA通信。

2)代码介绍

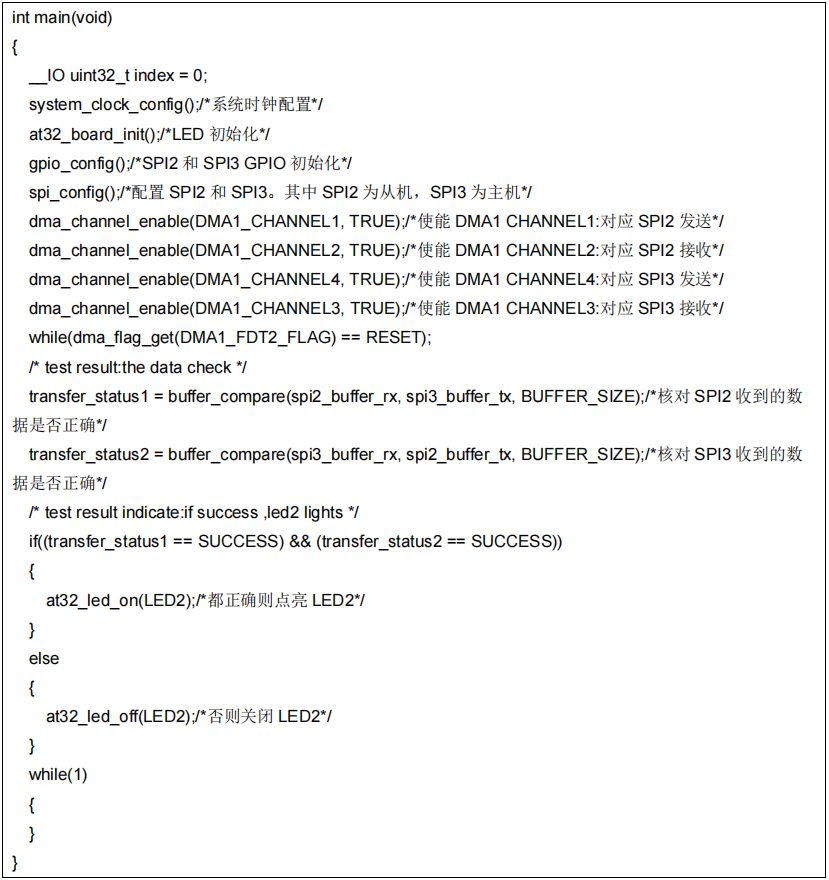

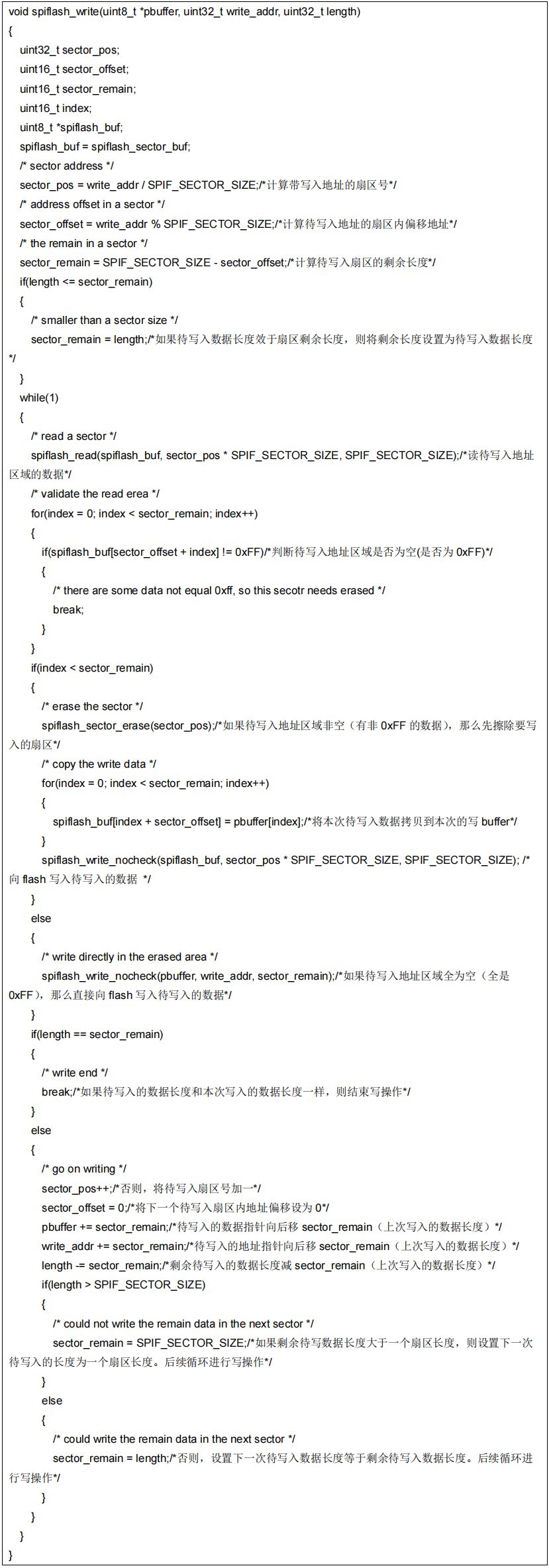

main函数代码描述

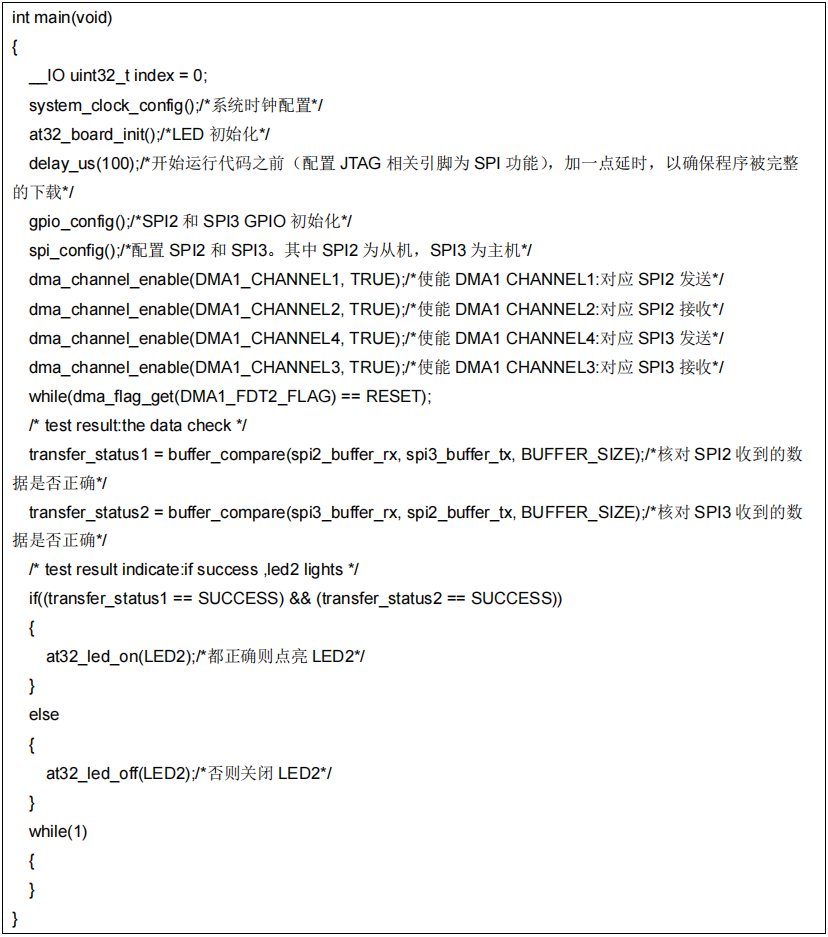

SPI通信配置及DMA配置函数代码描述

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

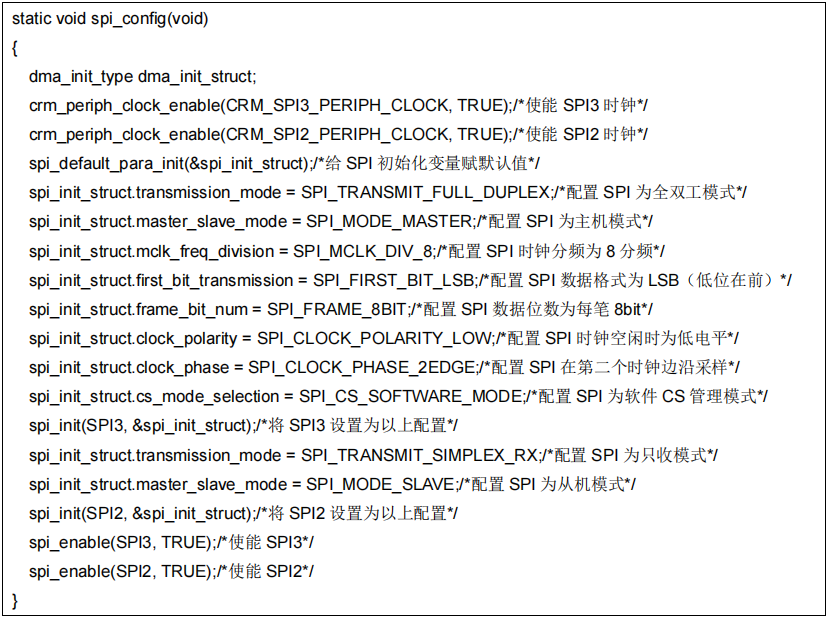

案例3-SPI只收通信

功能简介

实现SPI2和SPI3之间的单向只收通信。 接线如下:

SPI2 SPI3

PD1(短短板)<--->PC10(短单)

PD4(莫西)<--->PC12(莫西)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesspionly_receive_mode_polling

软件设计

1)配置流程

配置SPI2和SPI3对应的GPIO;

配置SPI2和SPI3的通信配置;

开始轮询通信。

2)代码介绍

main函数代码描述

SPI通信配置代码描述

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

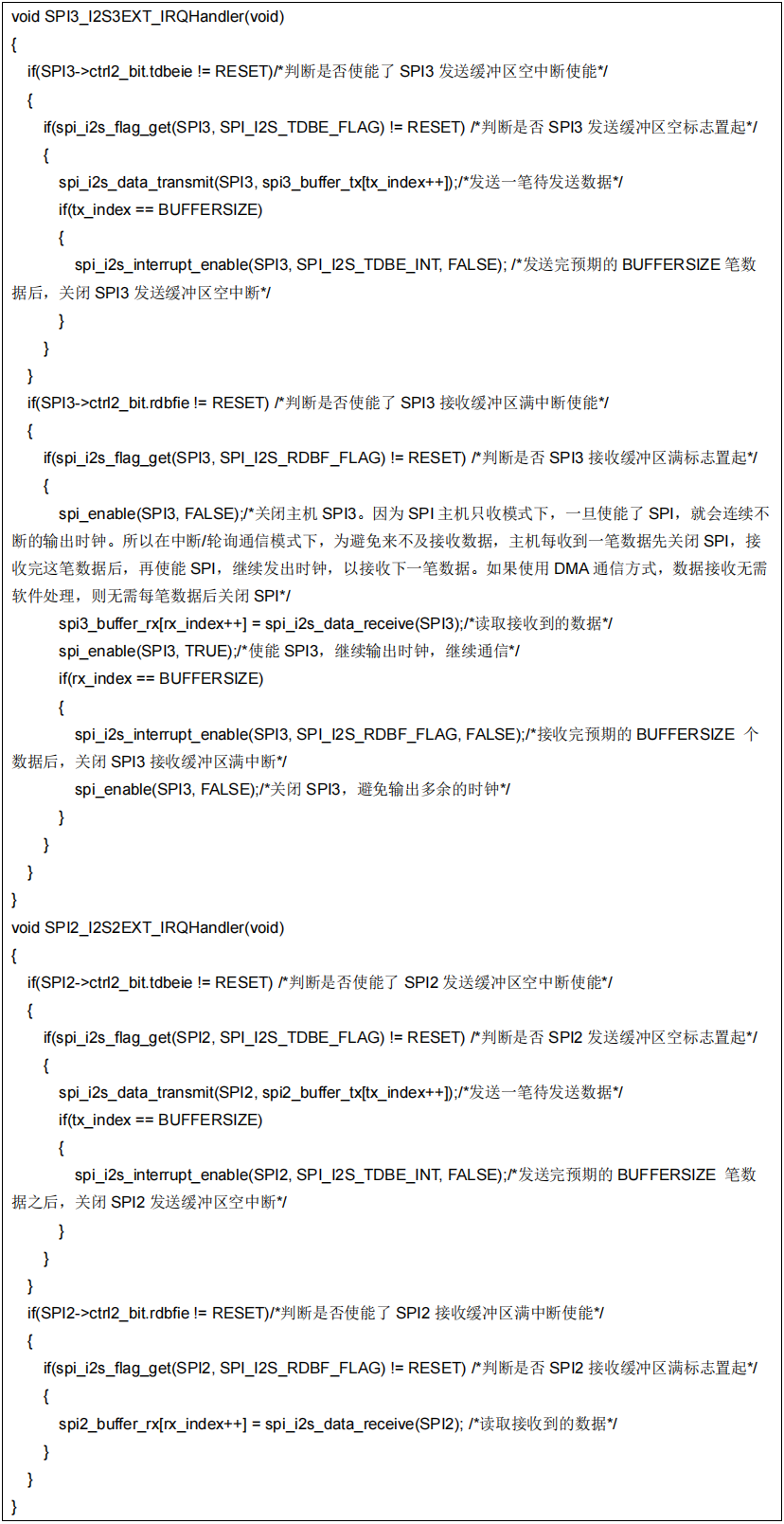

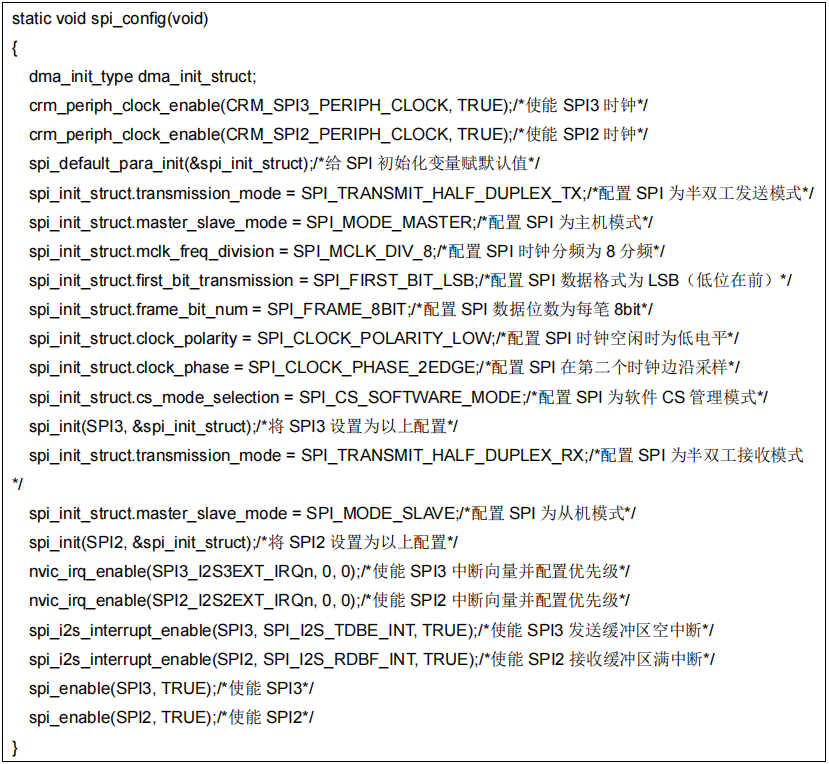

案例4-SPI半双工中断方式通信

功能简介

实现SPI2和SPI3之间的半双工通信。 接线如下:

SPI2 SPI3

PD1(短短板)<--->PC10(短单)

PC2(味噌)<--->PC12(莫西)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_xxxxexamplesspihalfduplex_interrupt

软件设计

1)配置流程

配置SPI2和SPI3对应的GPIO;

设置SPI2和SPI3的中断处理函数;

配置SPI2和SPI3的通信配置;

开始中断通信。

2)代码介绍

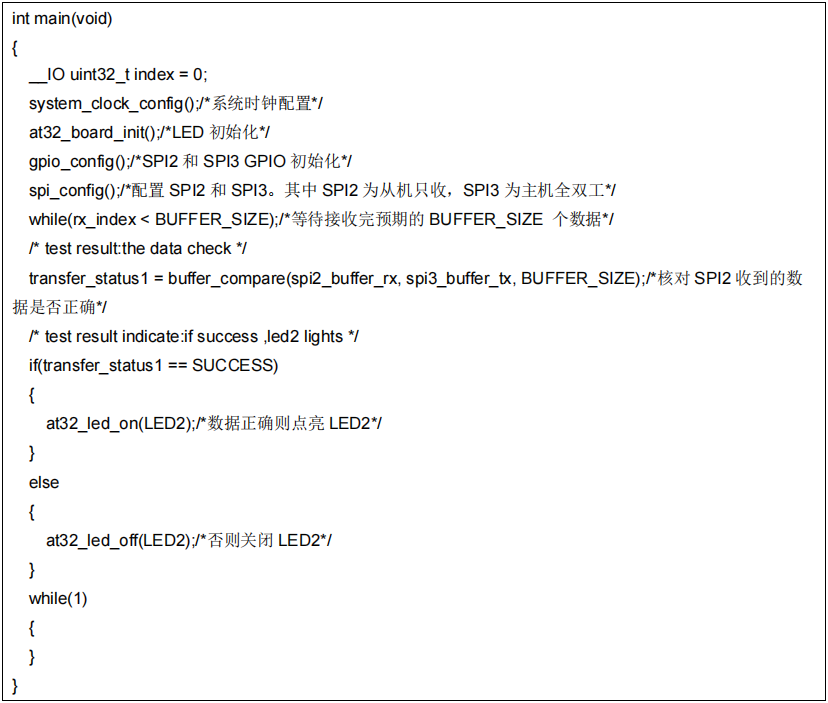

main函数代码描述

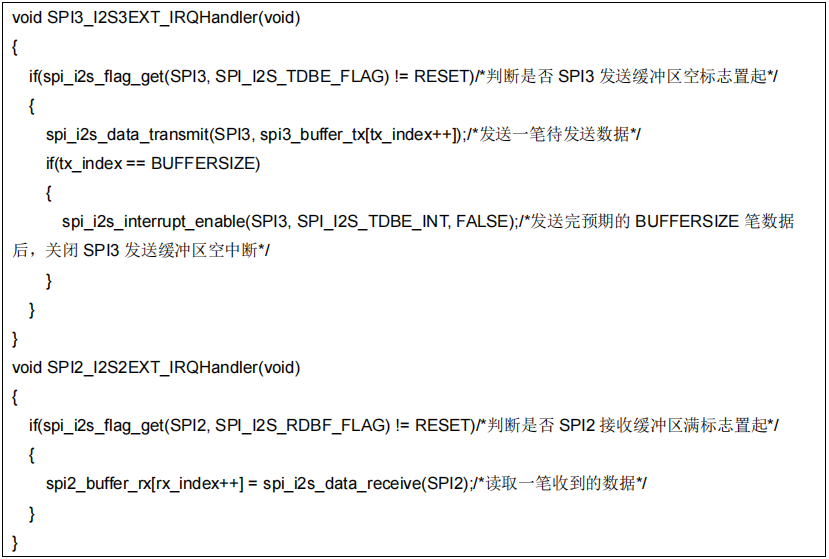

中断处理函数代码描述

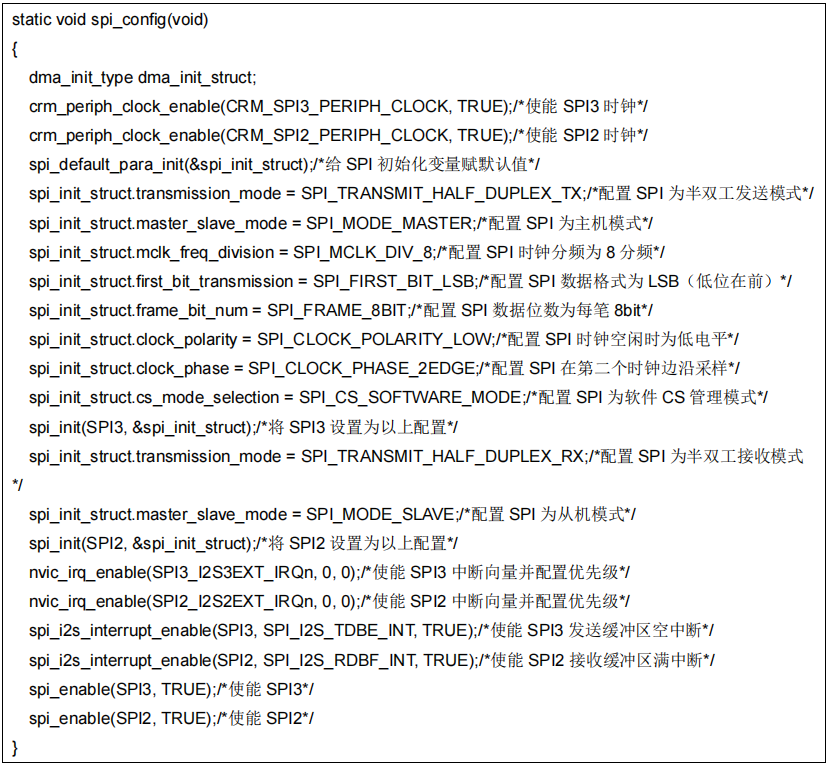

SPI通信配置函数代码描述

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

案例5-SPI半双工中断方式通信-加收发切换

功能简介

实现SPI2和SPI3之间的半双工收发切换通信。 接线如下:

SPI2 SPI3

PD1(短短板)<--->PC10(短单)

PC2(味噌)<--->PC12(莫西)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesspihalfduplex_transceiver_switch

软件设计

1)配置流程

配置SPI2和SPI3对应的GPIO;

设置SPI2和SPI3的中断处理函数;

配置SPI2和SPI3的通信配置;

开始中断通信。

2)代码介绍

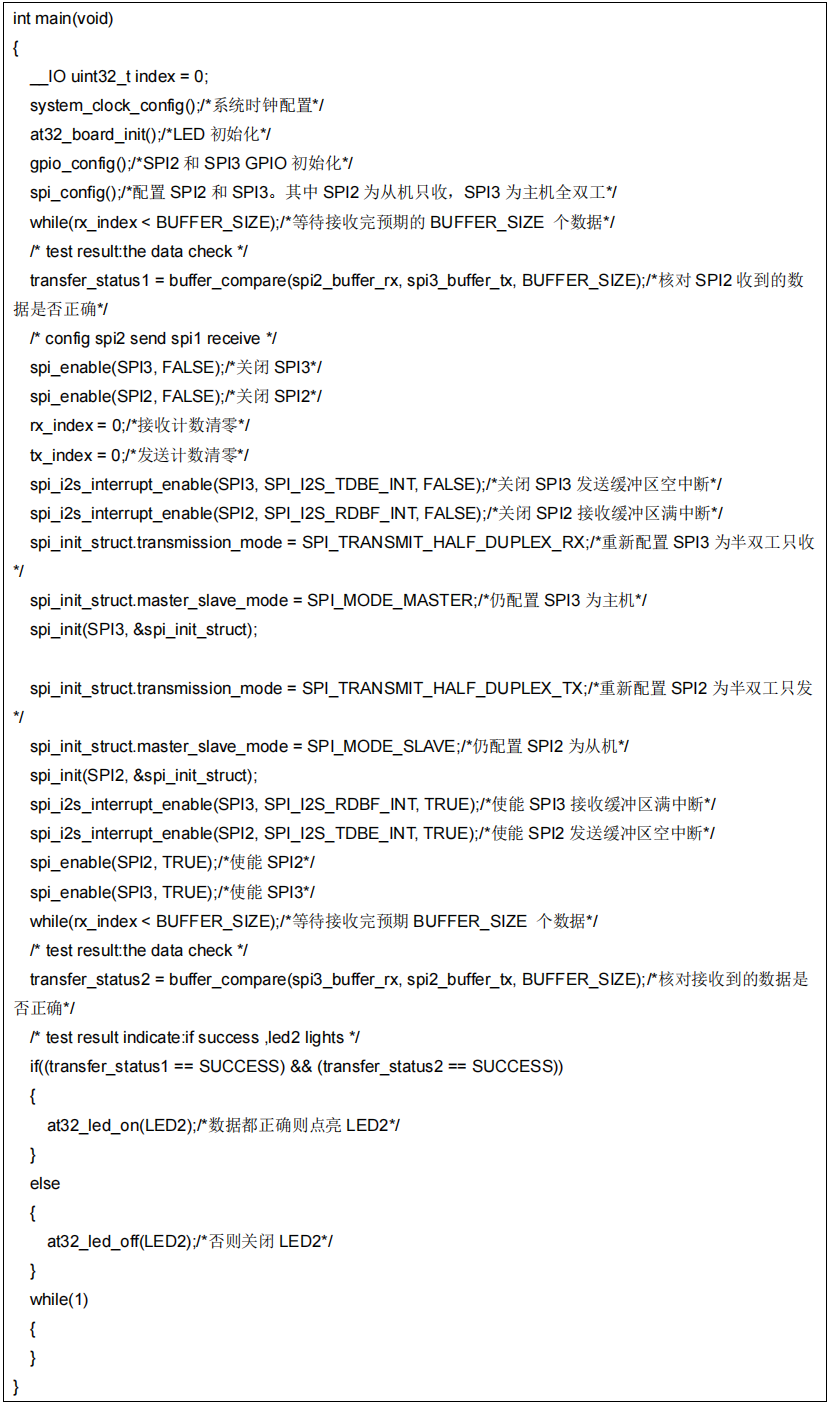

main函数代码描述

中断处理函数代码描述

SPI通信配置函数代码描述

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

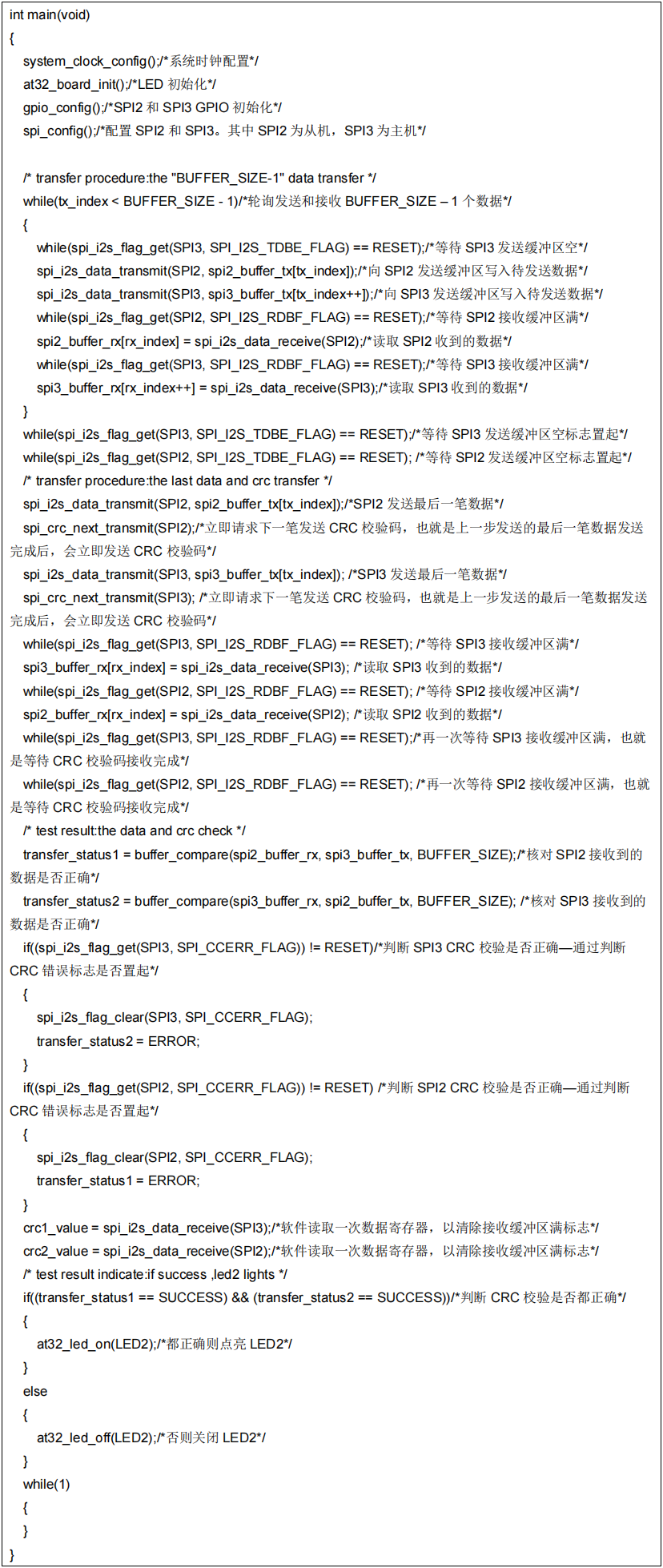

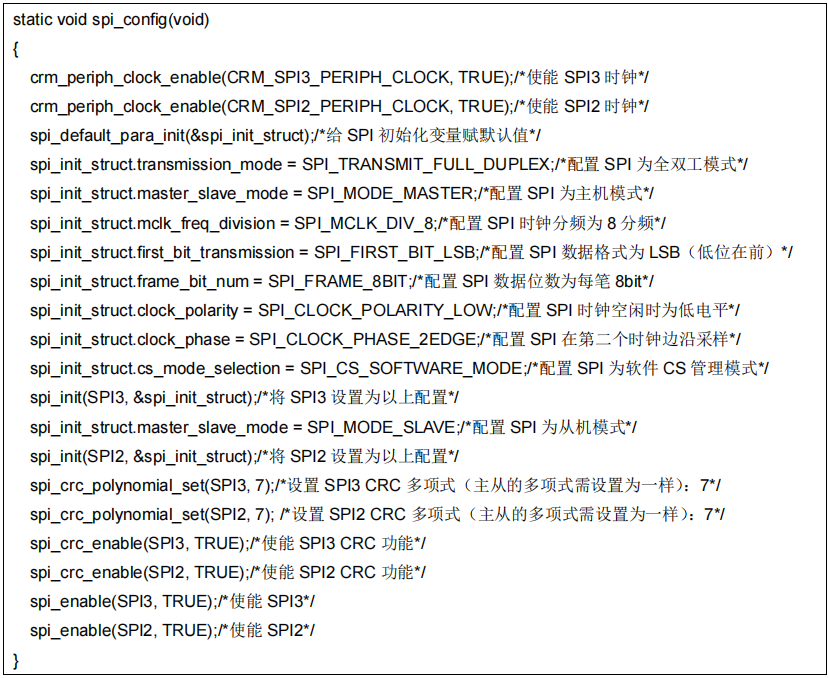

案例6-SPI CRC功能使用

功能简介

实现SPI2和SPI3之间的全双工通信和CRC校验。 接线如下:

SPI2 SPI3

PD1(短短板)<--->PC10(短单)

PC2(味噌)<--->PC11(味噌)

PD4(莫西)<--->PC12(莫西)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesspicrc_transfer_polling

软件设计

1)配置流程

配置SPI2和SPI3对应的GPIO;

配置SPI2和SPI3通信配置;

开始轮询通信和CRC校验。

2)代码介绍

main函数代码描述

SPI通信配置函数代码描述

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

案例7-SPI TI模式使用(TI SSP协议)

功能简介

实现SPI2和SPI3之间的TI模式DMA通信。 接线如下:

SPI2 SPI3

PD0(CS)<--->PA4(CS)

PD1(短短板)<--->PC10(短单)

PC2(味噌)<--->PC11(味噌)

PD4(莫西)<--->PC12(莫西)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesspi i_fullduplex_dma

软件设计

1)配置流程

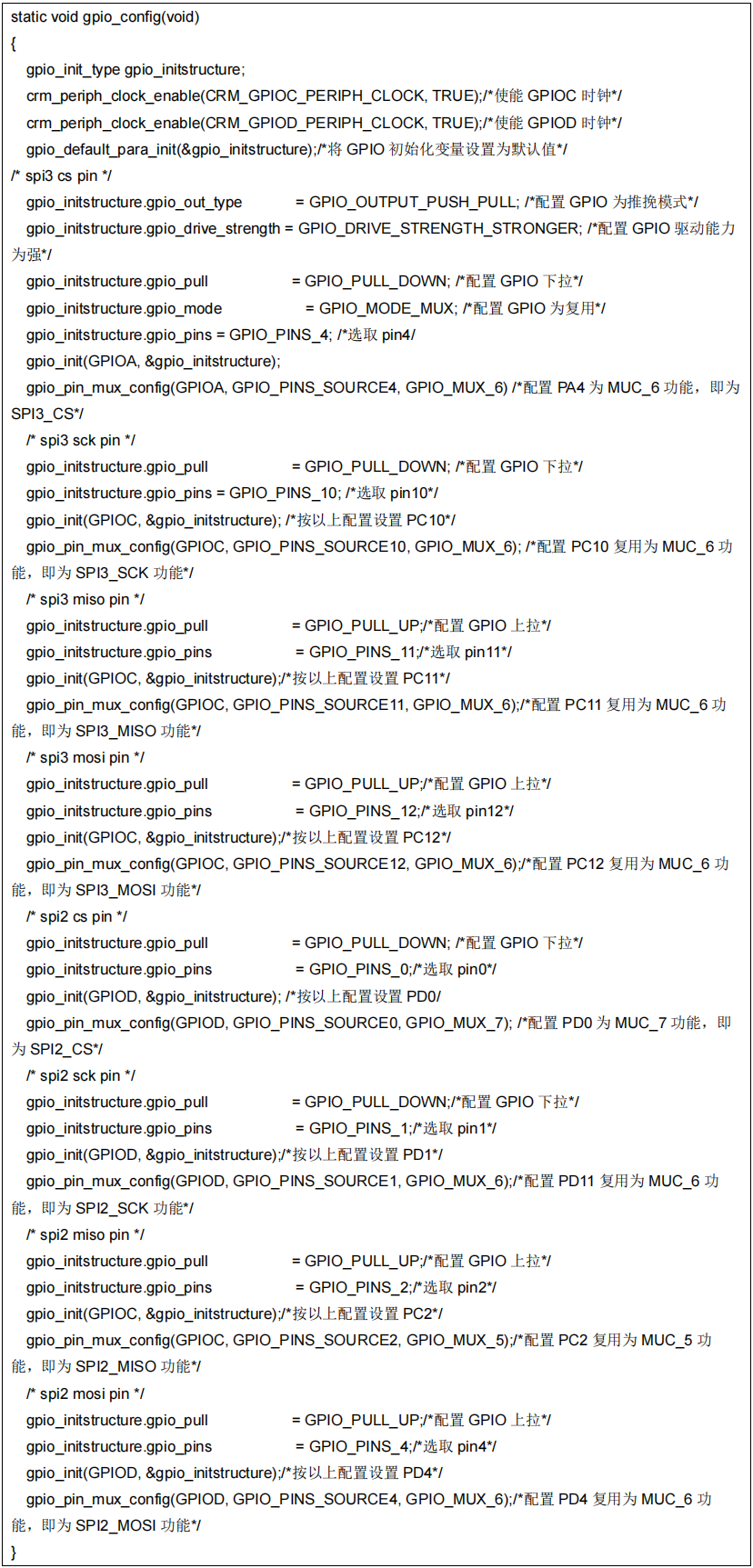

配置SPI2和SPI3对应的GPIO;

配置SPI2和SPI3的通信配置和DMA配置;

开始DMA通信。

2)代码介绍

main函数代码描述

SPI通信配置及DMA配置函数代码描述

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

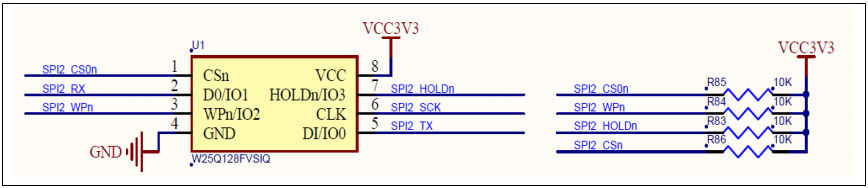

案例8-SPI读写FLASH(W25Q128)

功能简介

实现SPI2读/写flash(w25q128)。 接线如下:

SPI2 W25Q128

PD0(CS)<--->CS 引脚

PD1(单片)<--->CLK引脚

PC2(味噌)<--->引脚

PD4(MOSI)<--->DO引脚

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD和w25q128电路板

w25q128建议电路如下图26:

图26 w25q128建议电路

2)软件环境:

projectat_start_f437examplesspiw25q_flash

软件设计

1)配置流程

配置SPI2和对应GPIO;

读取flash ID;

擦除flash扇区;

向flash写入数据;

读取上一步flash写入数据的区域。

2)代码介绍

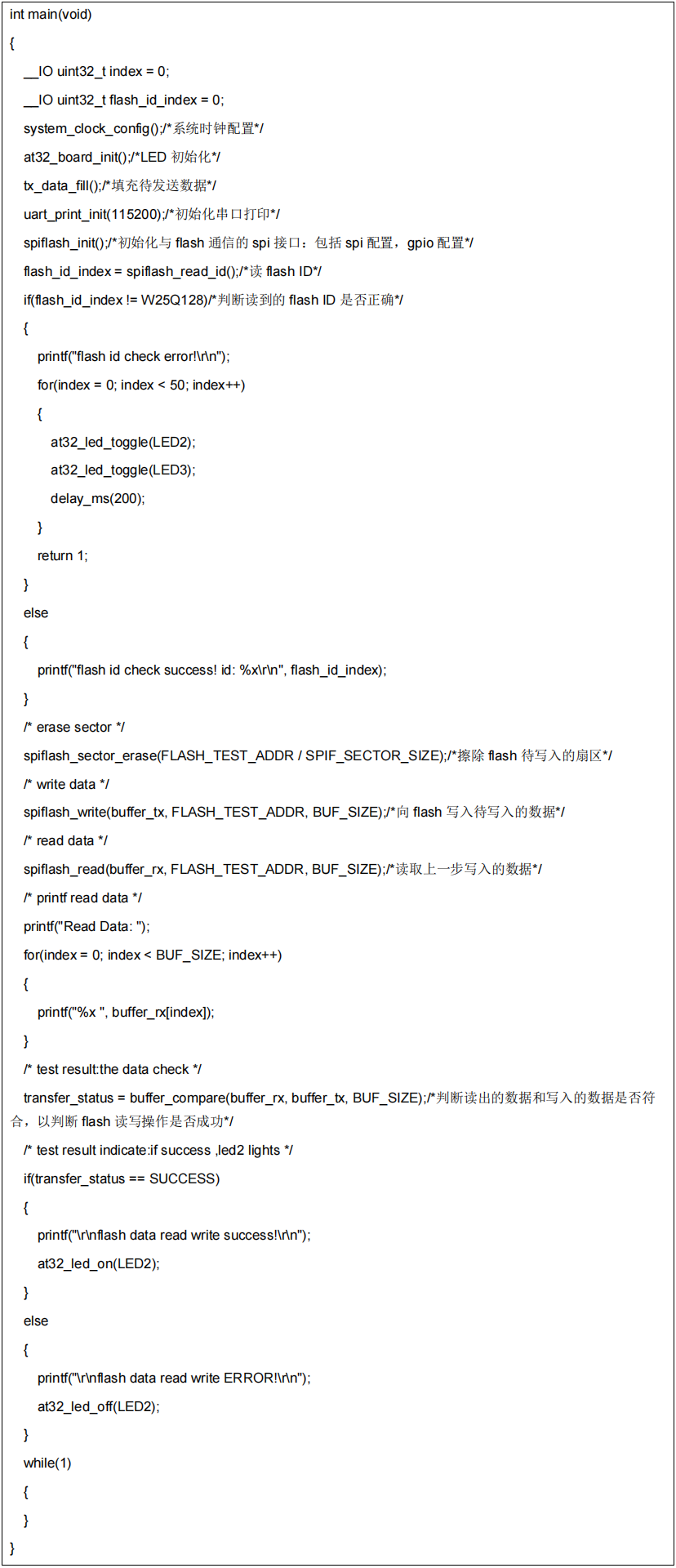

main函数代码描述

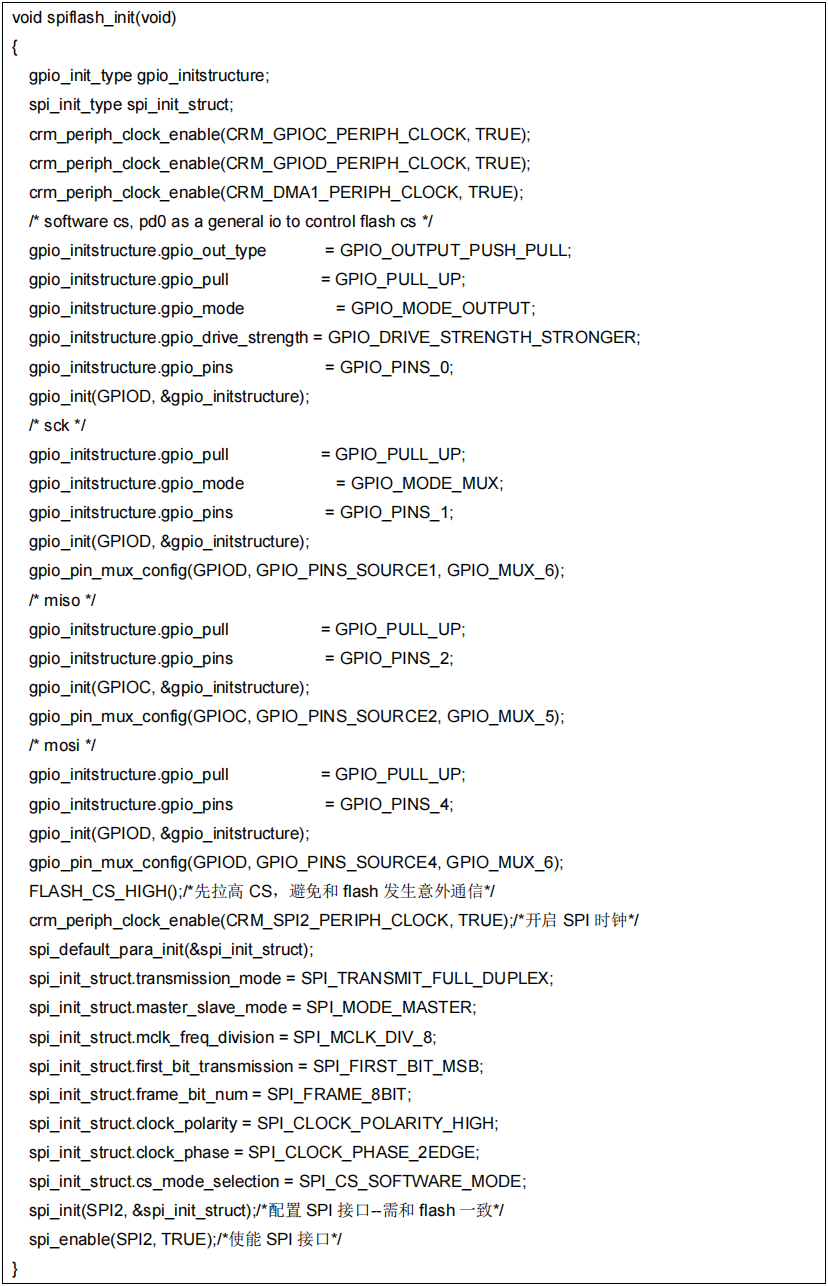

spi接口配置函数和gpio配置函数代码描述

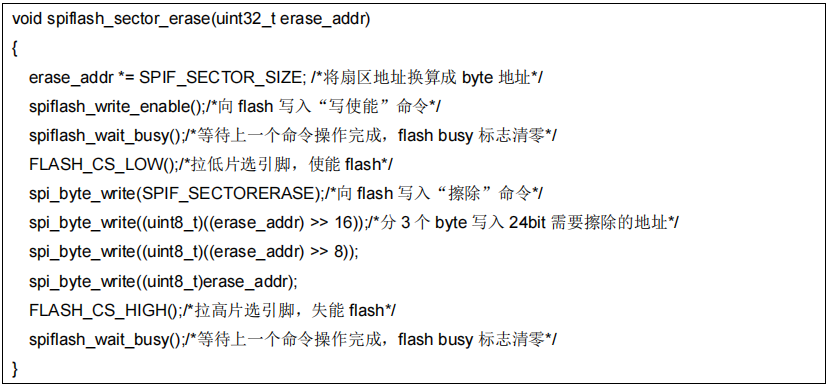

flash擦除函数代码描述

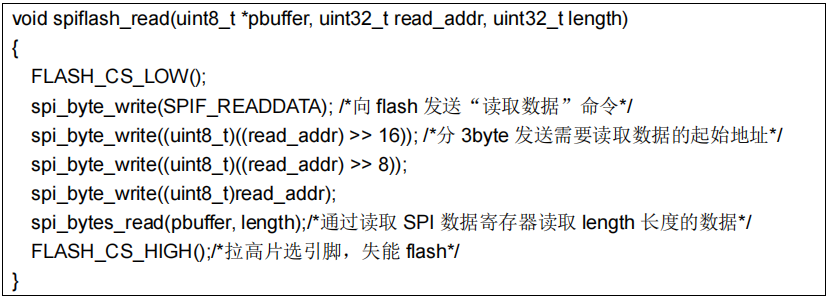

flash读数据函数代码描述

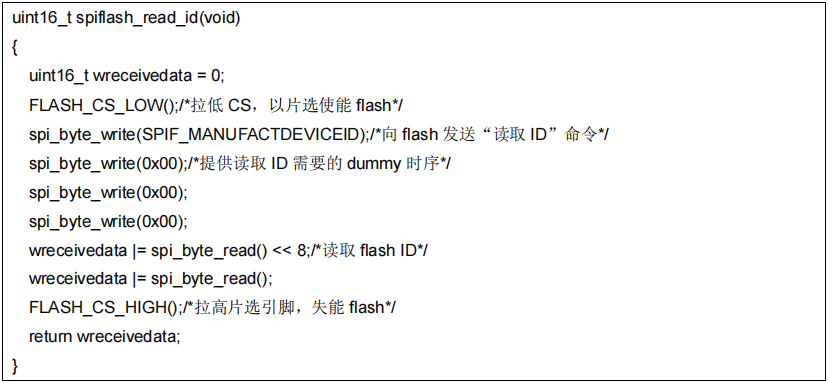

flash读ID函数代码描述

flash写函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和FLASH通信正常。

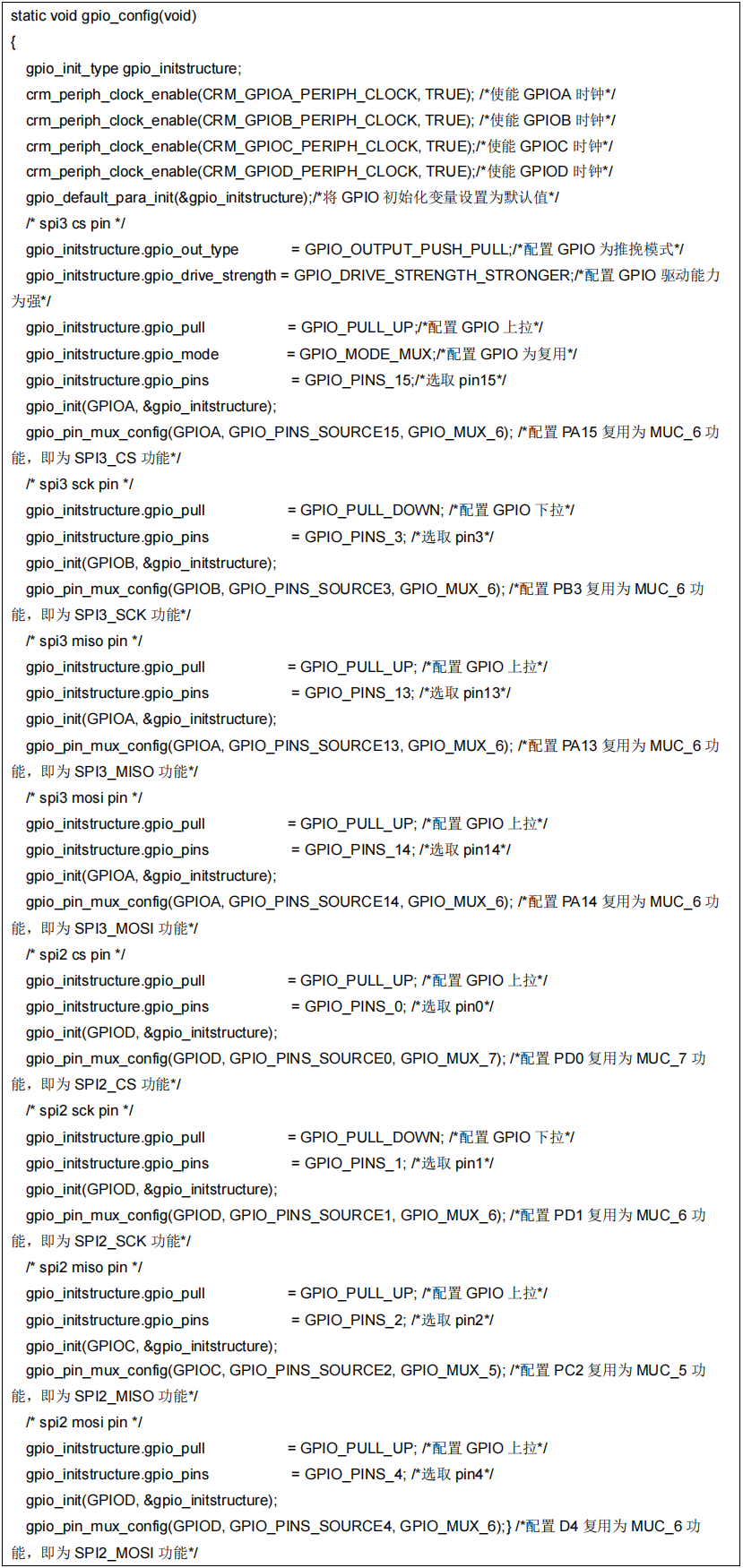

案例9-SPI使用jtag引脚的配置

功能简介

实现SPI2和SPI3之间,使用特殊的jtag引脚的全双工轮询通信。 接线如下:

SPI2 SPI3

PD0(CS)<--->PA15(CS)

PD1(sck)<--->pb3(sck)

PC2(味噌)<--->PA13(味噌)

PD4(运动)<--->PA14(运动)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesuse_jtagpin_hardwarecs_dma

软件设计

注意:本文仅介绍了AT32F435/F437的SPI使用jtag引脚的配置,其他型号的使用配置稍有不同,请参照对应型号的BSP使用。

1)配置流程

配置SPI2和SPI3对应的GPIO;

配置SPI2和SPI3通信配置;

开始轮询通信。

2)代码介绍

main函数代码描述

SPI通信配置函数代码描述

SPI GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明SPI2和SPI3通信正常。

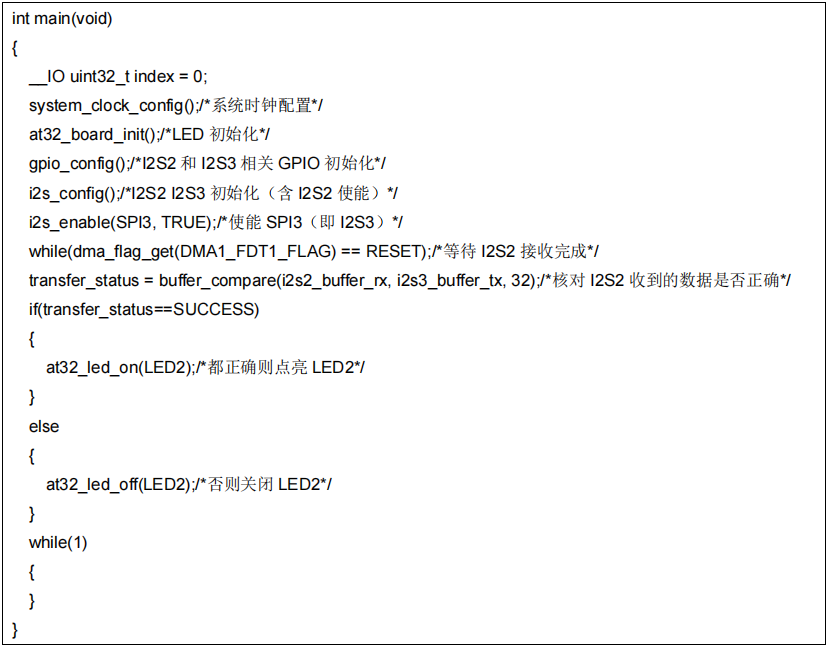

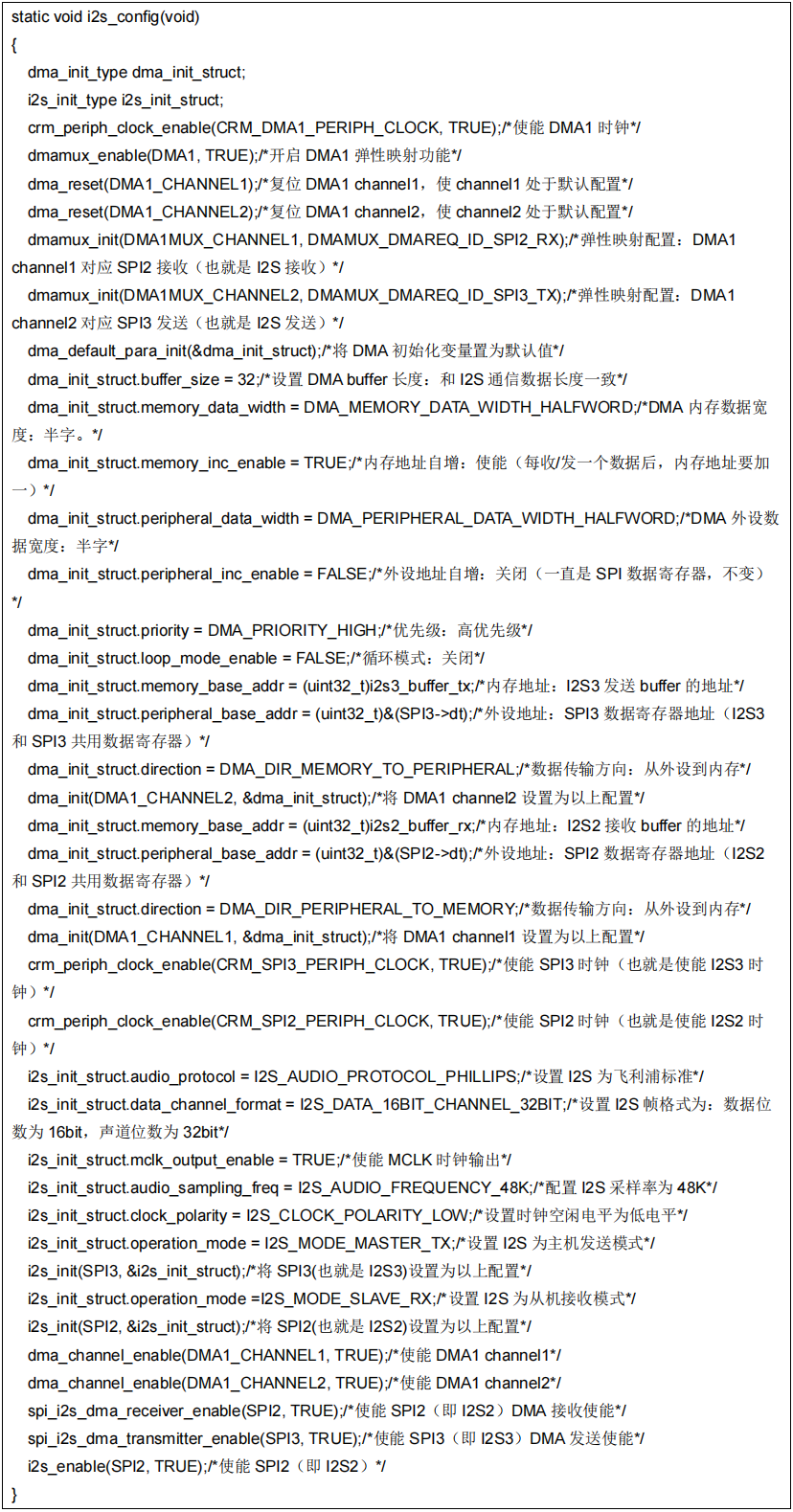

I2S案例

案例1-I2S半双工DMA方式通信

功能简介

实现I2S2和I2S3之间的半双工DMA通信。 接线如下:

I2S2 I2S3

PD0(WS)<--->PA4(WS)

PD1(CK)<--->PC10(CK)

PD4(标清)<--->PC12(标清)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesi2shalfduplex_dma

软件设计

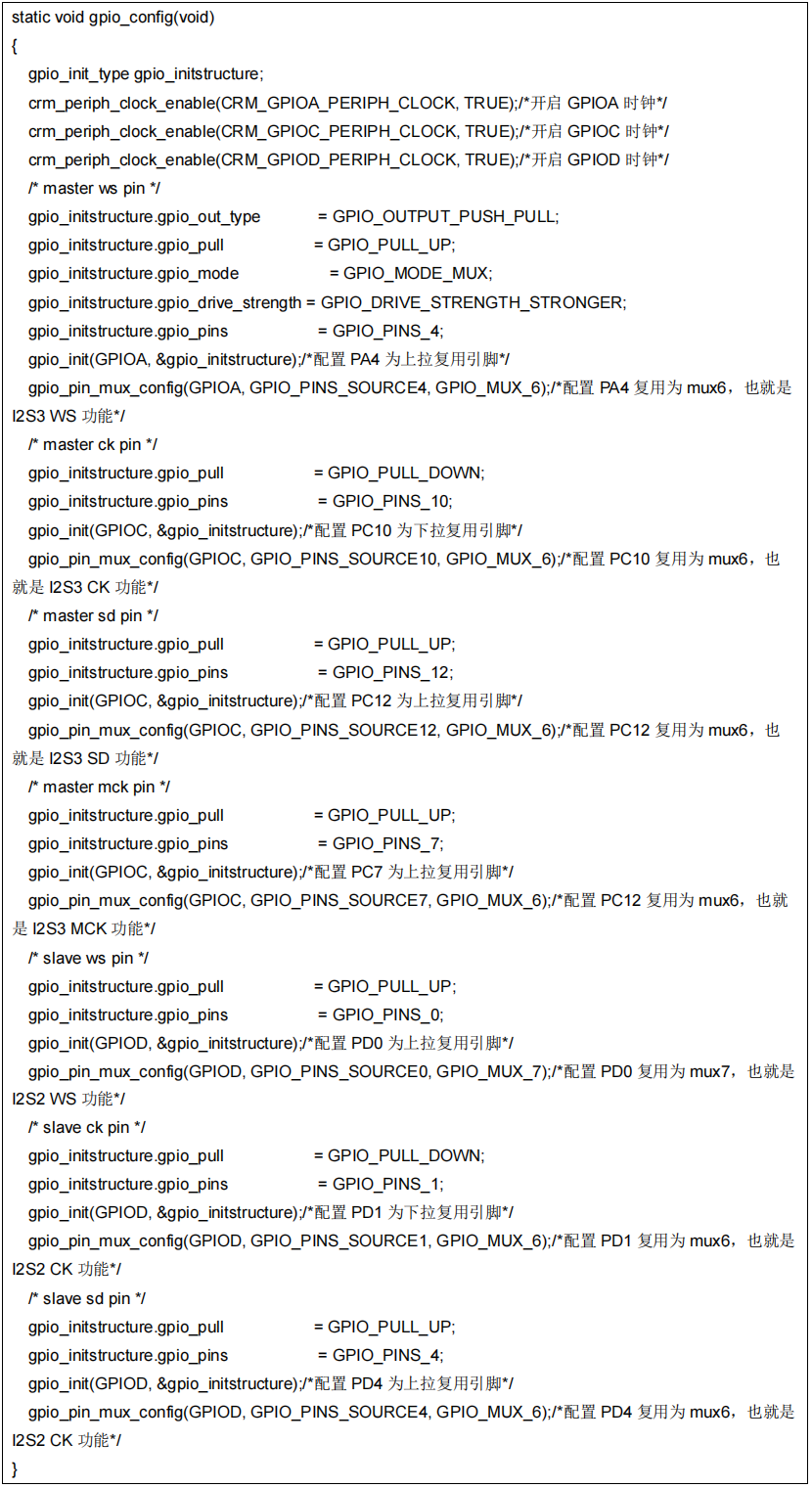

1)配置流程

配置I2S2和I2S3对应的GPIO;

配置I2S2和I2S3的通信配置和DMA配置;

开始DMA通信。

2)代码介绍

main函数代码描述

I2S配置及DMA配置函数代码描述

GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明I2S2和I2S3通信正常。

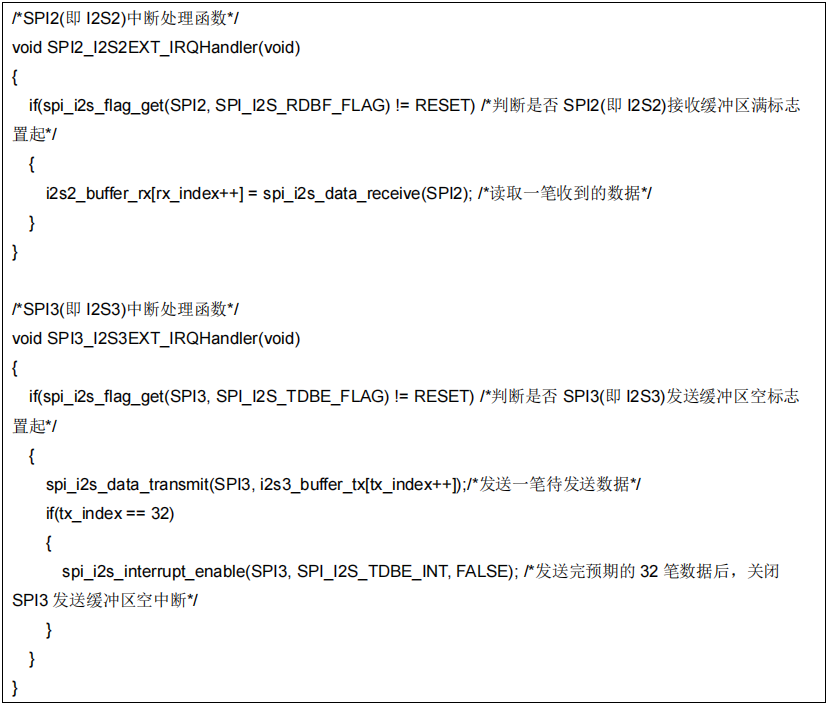

案例2-I2S半双工中断方式通信

功能简介

实现I2S2和I2S3之间的半双工中断方式通信。 接线如下:

I2S2 I2S3

PD0(WS)<--->PA4(WS)

PD1(CK)<--->PC10(CK)

PD4(标清)<--->PC12(标清)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesi2shalfduplex_interrupt

软件设计

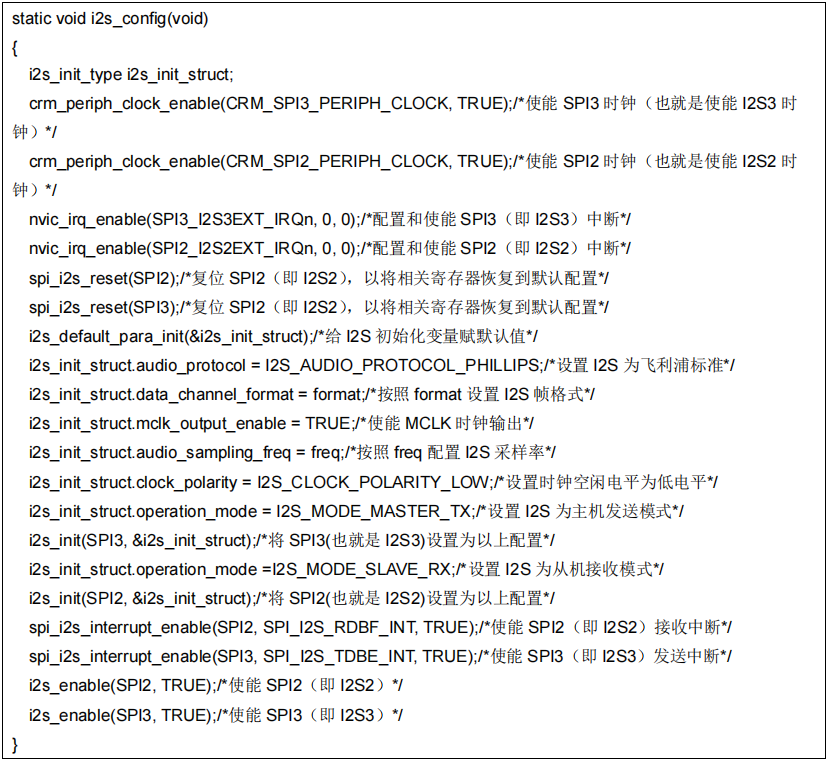

1)配置流程

配置I2S2和I2S3对应的GPIO;

配置I2S2和I2S3的通信配置;

安排中断功能;

开始中断通信。

2)代码介绍

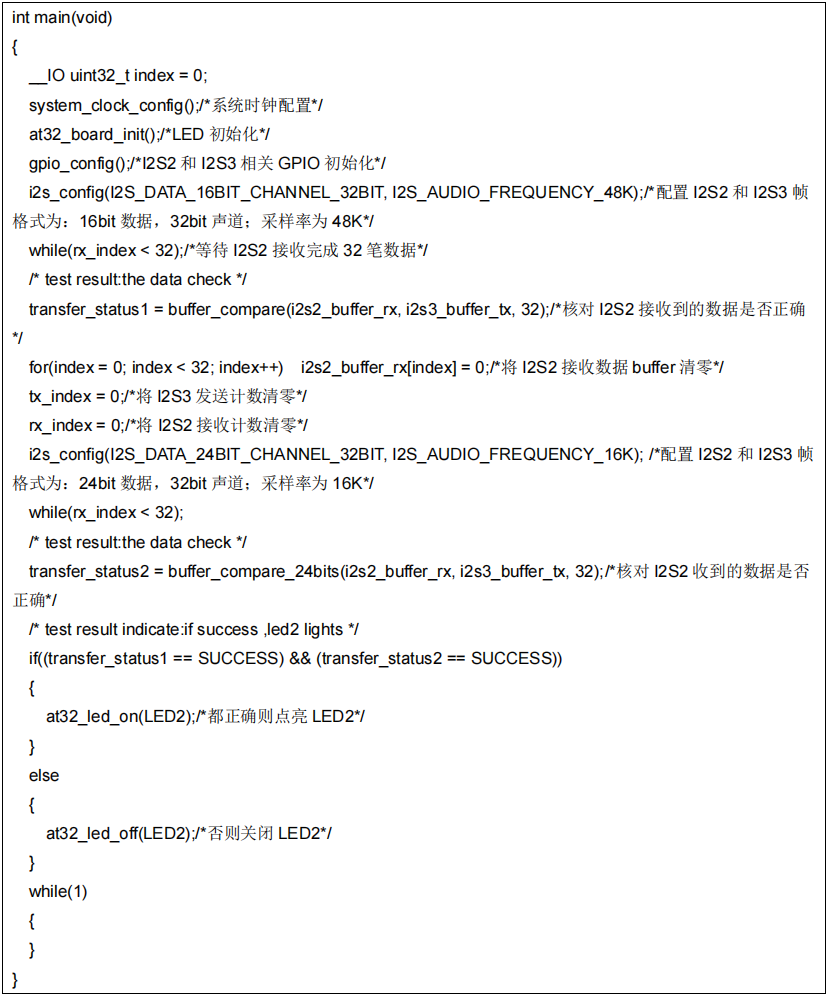

main函数代码描述

I2S配置函数代码描述

I2S中断配置函数代码描述

GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明I2S2和I2S3通信正常。

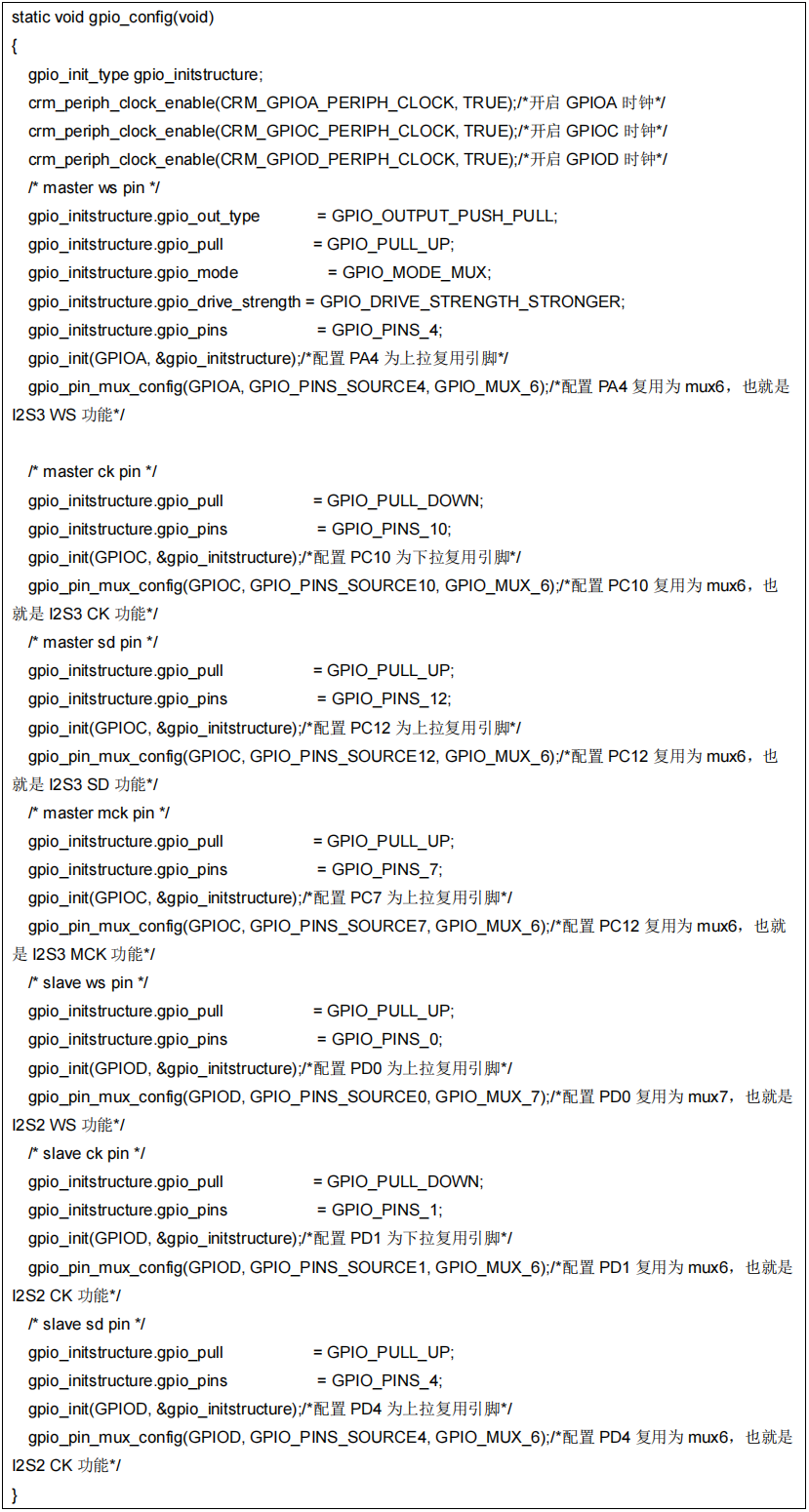

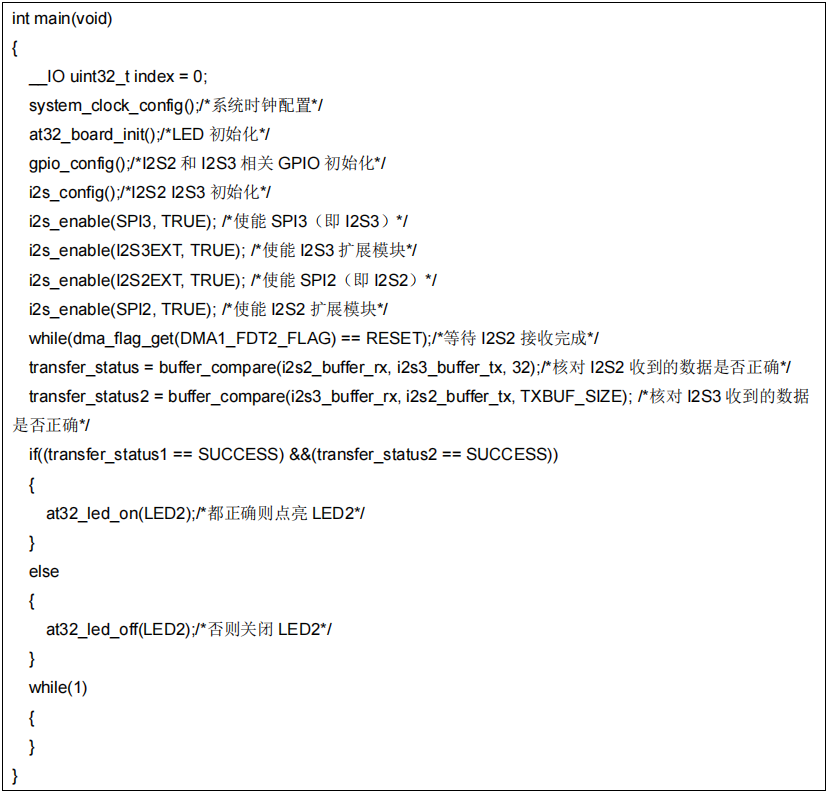

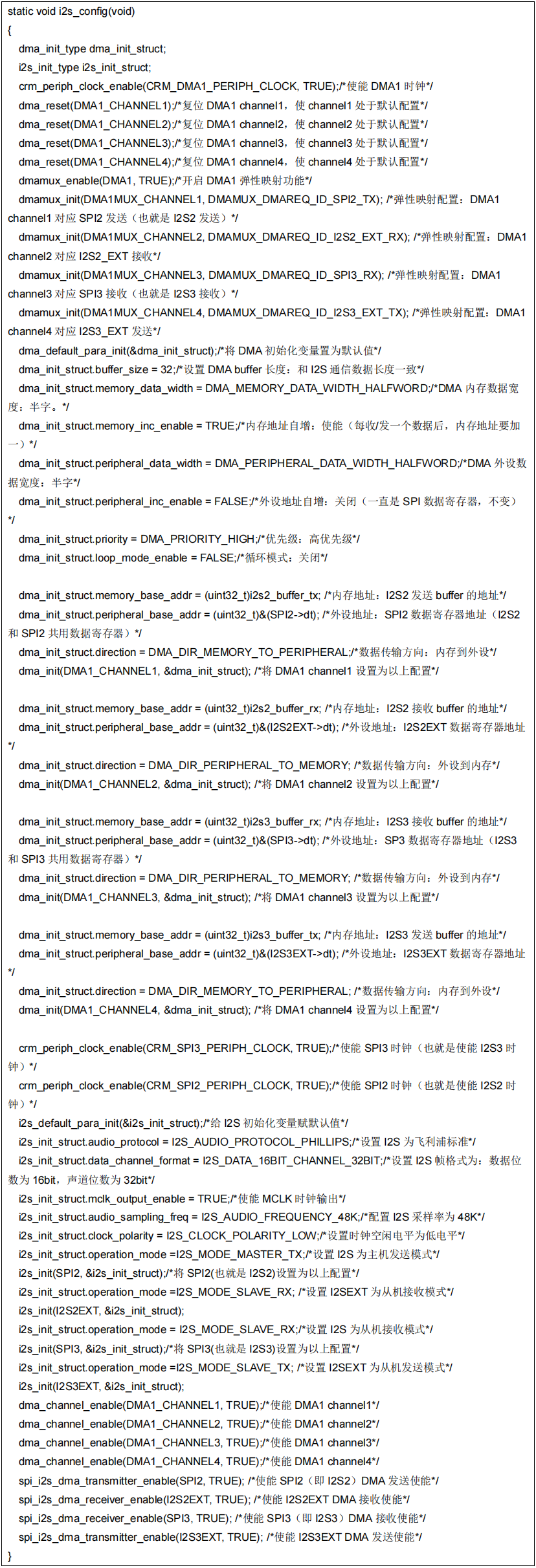

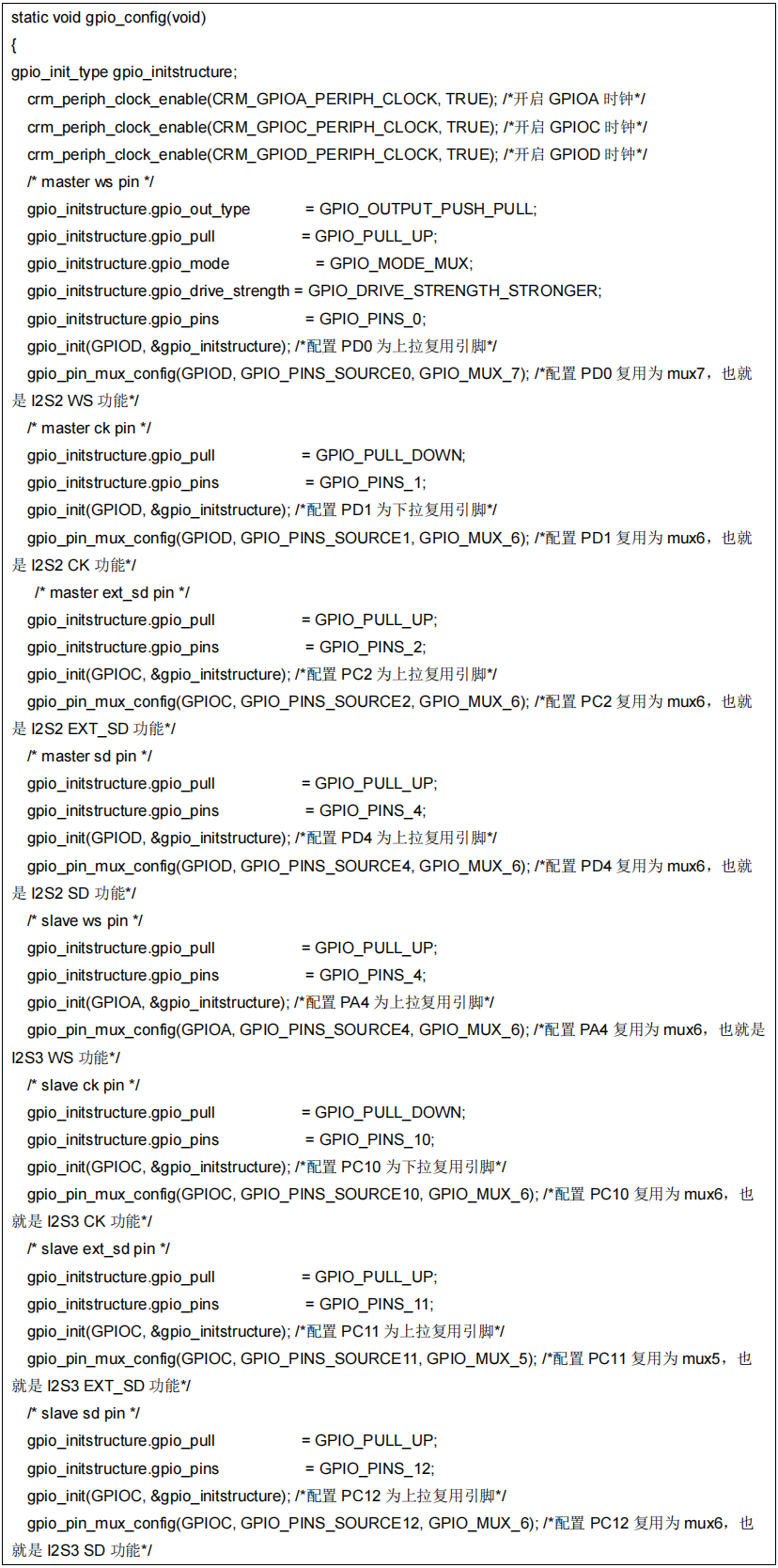

案例3-AT32F403A/F407/F435/F437 I2S全双工DMA方式通信

功能简介

实现I2S2和I2S3之间的全双工DMA通信。 接线如下:

I2S2 I2S3

PD0(WS)<--->PA4(WS)

PD1(短短板)<--->PC10(短单)

PC2(ext_sd)Rx<--->pc11(ext_sd)TX

PD4(SD)TX<--->PC12(SD)RX

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_xxxxexamplesi2sfullduplex_dma

软件设计

1)配置流程

配置I2S2和I2S3对应的GPIO;

配置I2S2和I2S3的通信配置和DMA配置;

开始DMA通信。

2)代码介绍

main函数代码描述

I2S配置及DMA配置函数代码描述

GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明I2S2和I2S3全双工通信正常。

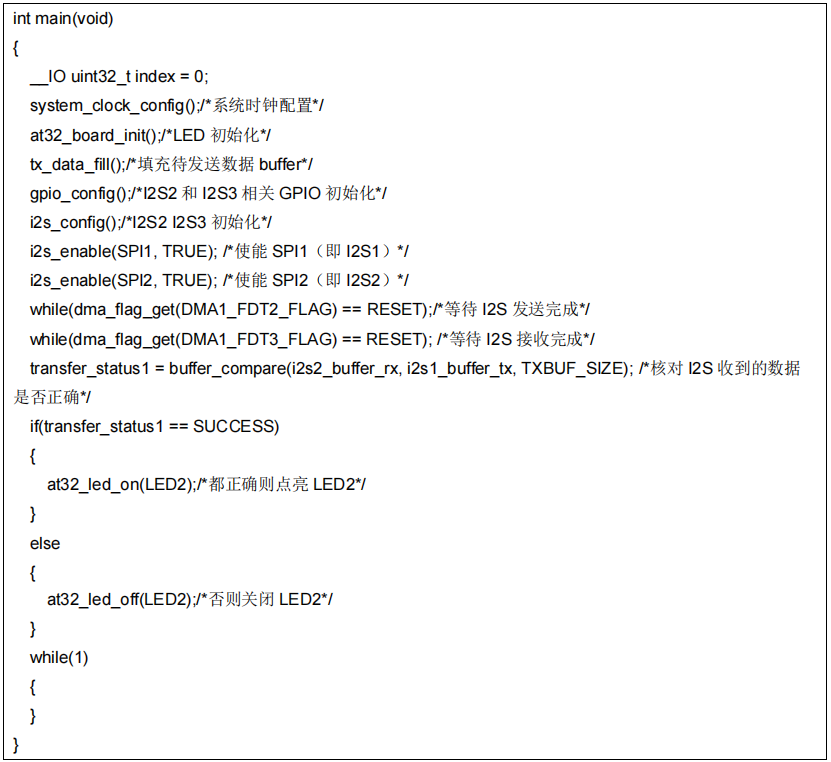

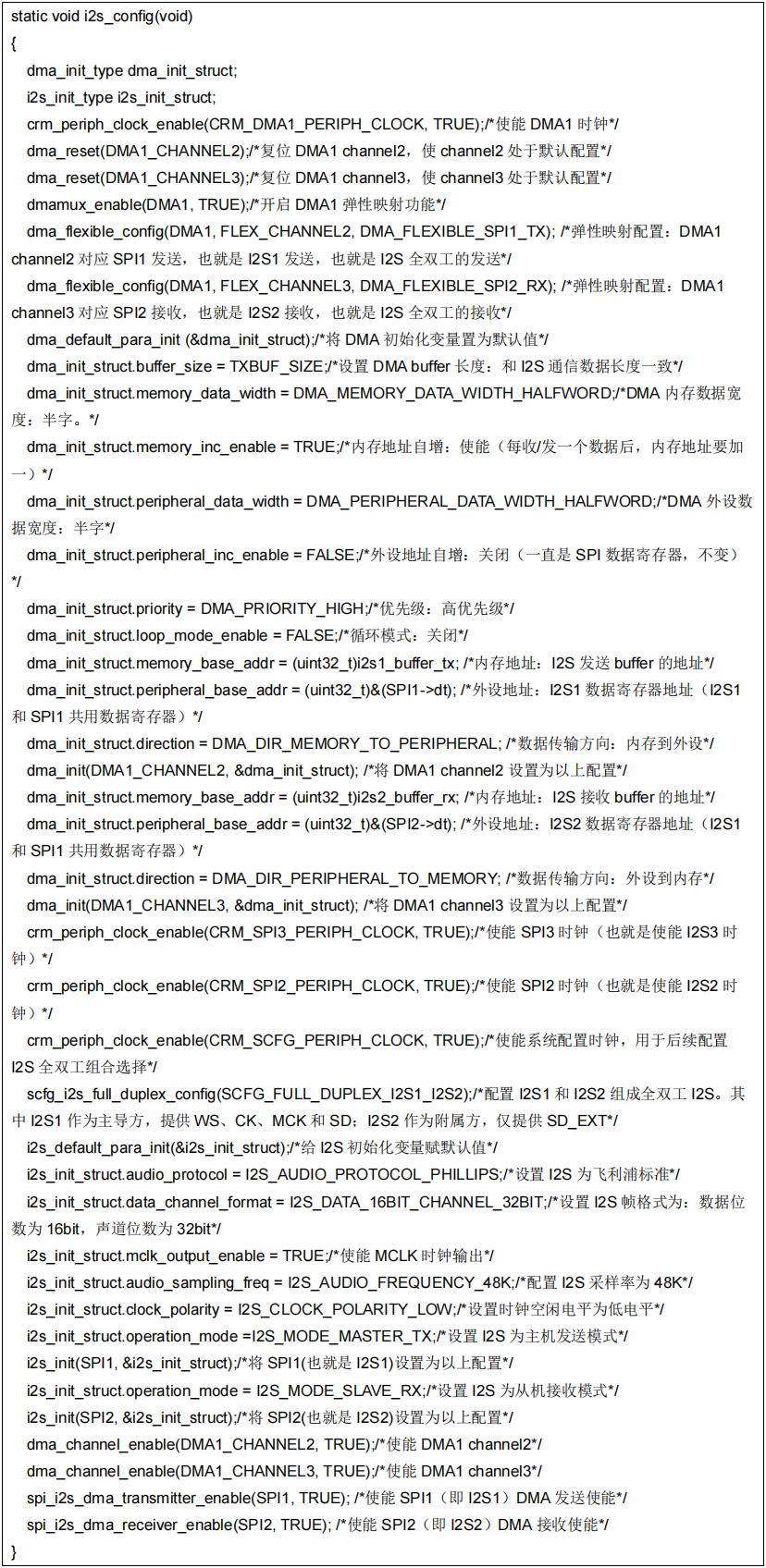

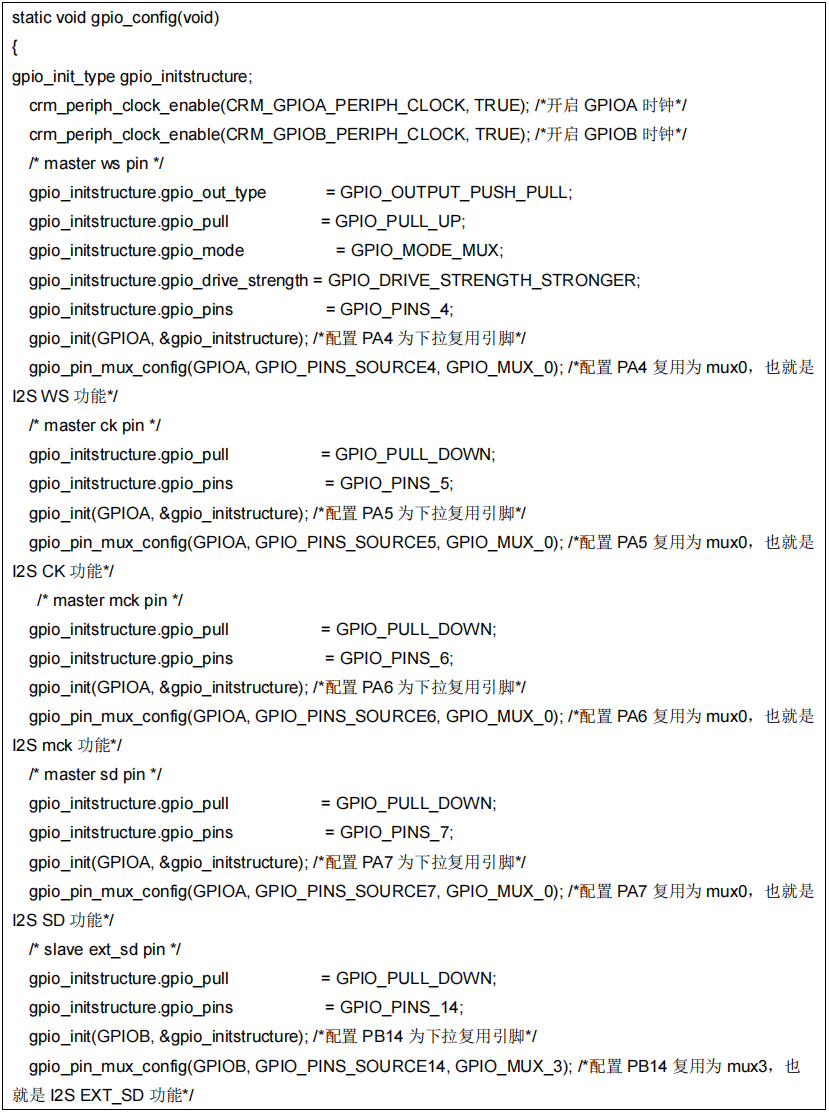

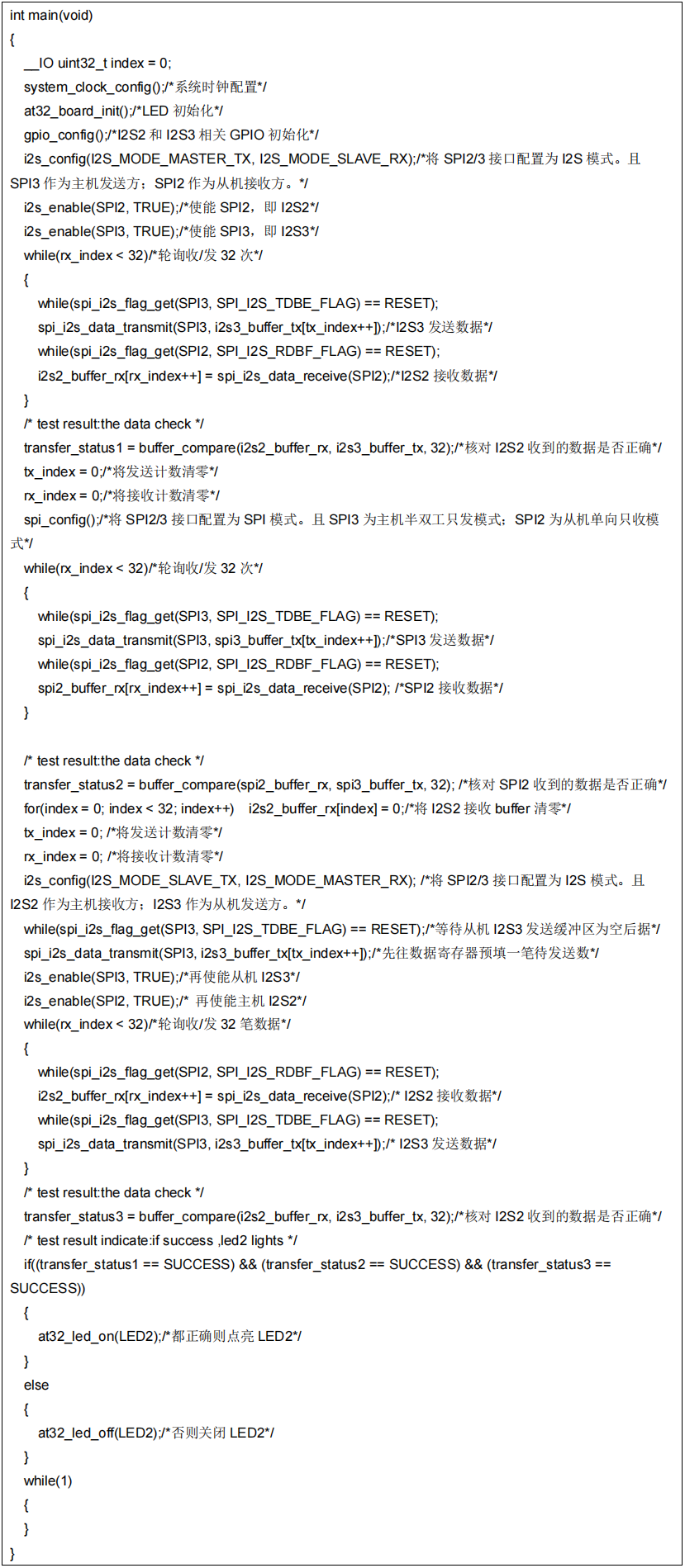

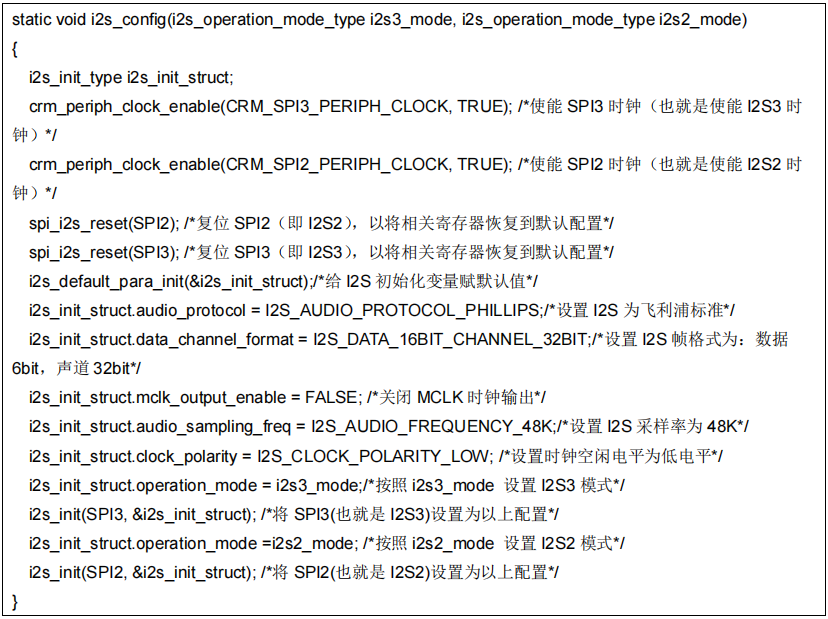

案例4-AT32F425 I2S全双工DMA方式通信

功能简介

实现I2S1和I2S2组成一个全双工I2S,组成的全双工I2S接口定义如下:

PA4(ws)

PA5(CK)

PA6(MCK)

PA7(SD TX)

PB14(ext_sd 接收)

由于AT32F425只有3个spi(I2S),只能组成一个全双工I2S,所以不能在同一块AT-START上用两个全双工I2S进行通信。 所以本案例使用一个全双工I2S进行自收自发通信,接线如下:

PA4(ws)<--->NC

PA5(ck)<--->NC

PA6(MCK)<--->NC

PA7(标清)<--->PB14(ext_sd)

用户也可以准备两块AT-START板子对测。 使用两块板子时,需要注意一块AT-START配置为主机,一块AT-START配置为从机。 本案例中的代码仅展示配置为主机,在一块AT-START上进行自发自收的配置。

资源准备

1)硬件环境:

一块AT32F425的AT-START BOARD

2)软件环境:

projectat_start_f425examplesi2sfullduplex_dma

软件设计

1)配置流程

配置I2S1和I2S2对应的GPIO;

配置I2S1和I2S2的通信配置和DMA配置;

开始DMA通信。

2)代码介绍

main函数代码描述

I2S配置及DMA配置函数代码描述

GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明I2S全双工通信正常。

案例5-I2S和SPI功能切换通信

功能简介

实现SPI2和SPI3之间通信切换到I2S2和I2S3之间通信。 接线如下:

SPI2/I2S2 SPI3/I2S3

PD0(CS/WS)<--->PA15(CS/WS)

PD1(sck/ck)<--->pb3(sck/ck)

PD4(莫西/标清)<--->PB5(莫西/标清)

资源准备

1)硬件环境:

一块AT32F437的AT-START BOARD

2)软件环境:

projectat_start_f437examplesi2sspii2s_switch_halfduplex_polling

软件设计

1)配置流程

配置SPI2/I2S2和SPI3/I2S3对应的GPIO;

配置I2S2和I2S3的通信配置(主发从收);

开始I2S2和I2S3的轮询通信,并核对数据;

配置SPI2和SPI3的通信配置(SPI3为主机半双工只发; SPI2为从机单向只收);

开始SPI2和SPI3的轮询通信,并核对数据;

配置I2S2和I2S3的通信配置(主收从发);

开始I2S2和I2S3的轮询通信,并核对数据。

2)代码介绍

main函数代码描述

I2S配置函数代码描述

SPI配置函数代码描述

GPIO配置函数代码描述

实验效果

AT-START BOARD的LED2亮起,说明I2S2和I2S3通信正常,SPI2和SPI3也通信正常。

审核编辑:汤梓红

-

mcu

+关注

关注

146文章

17123浏览量

350973 -

接口

+关注

关注

33文章

8575浏览量

151014 -

SPI

+关注

关注

17文章

1706浏览量

91498 -

I2S

+关注

关注

1文章

64浏览量

41902 -

AT32

+关注

关注

1文章

113浏览量

2090

原文标题:AT32讲堂048 | 雅特力AT32 MCU SPI/I2S入门指南

文章出处:【微信号:AT32 MCU 雅特力科技,微信公众号:AT32 MCU 雅特力科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AT32 MCU SPI/I2S入门指南

AT32 MCU SPI/I2S入门指南

雅特力AT32 MCU SPI/I2S入门指南

雅特力AT32 MCU SPI/I2S入门指南

评论