信号的时序设计

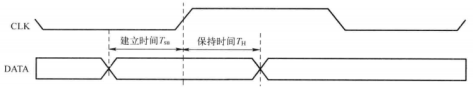

信号的时序要求就是数据信号与其对应的时钟信号保持某种同步关系。数据的采样同样依赖于某特定的时钟,由于信号边沿频谱高最容易受干扰,因此在采样时钟对数据信号进行采样时,应尽可能远离信号变化的边沿。如下图所示:

时钟CLK采样数据DATA的示意图

数据DATA发生变化后,需要等待Tsu的建立时间才能被采样,采样之后,相对于采样点,数据需要保持TH时间,这样才能实现对数据的有效接收。也就是说,为了使信号具有较好的时序设计余量,需要尽可能加大信号采样需要的信号建立时间和保持时间。

时序系统

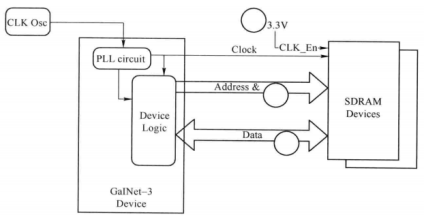

高速电路设计中所涉及的时序系统主要分为两类:源同步系统和共同时钟系统。源同步系统的同步时钟由发送数据或接受数据的芯片提供;而共同时钟系统的时钟是由另外的时钟芯片提供。如下图所示:

源同步系统示例

共同时钟系统示例

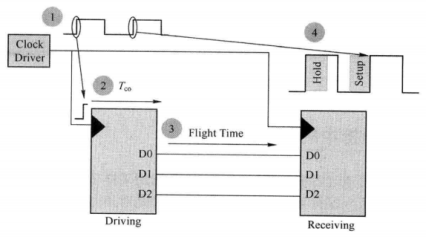

作者举了一个例子,一个基本的源同步时钟系统的结构示意如下图所示:

源同步时钟系统的结构示意图

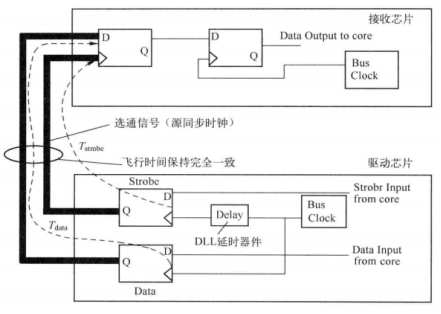

驱动芯片在发送数据信号的同时也产生了选通信号,而对于接收端的触发器,接收该选通信号脉冲数据,这个选通信号也可以称为源同步时钟信号。

在源同步时钟系统中,数据和源同步时钟信号是同步传输的,在设计中要保证这两个信号的飞行时间完全一致,说白了就是信号怎么发送的,就要怎么接收到。例如在进行DDR类存储的电路设计时所进行的PCB蛇形走线,都是为了满足信号之间的时序要求。

S参数模型、IBIS参数模型

作者对信号完整性分析中的S参数模型、IBIS参数模型的概念做了介绍。S参数是一种描述线性无源互连结构的行为模型,S参数模型把互连结构看成一个黑盒子,仅通过端口处的能量就可以描述互连结构的行为特征。

IBIS是用来描述IC器件的输入、输出和I/O Buffer行为特性的文件,也是一个行为模型,可以反映器件开关速度和驱动能力等特性,并且可以用来模拟Buffer和板上电路系统的相互作用,工程人员可以利用这个模型对PCB上的电路系统进行SI、串扰、EMC及时序的分析。

审核编辑:刘清

-

PCB设计

+关注

关注

394文章

4669浏览量

85168 -

emc

+关注

关注

169文章

3856浏览量

182772 -

高速电路

+关注

关注

8文章

157浏览量

24217 -

数据信号

+关注

关注

0文章

57浏览量

11961 -

时钟信号

+关注

关注

4文章

443浏览量

28498

发布评论请先 登录

相关推荐

信号完整性分析中的时序设计需要考虑什么?

信号完整性分析中的时序设计需要考虑什么?

评论