LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于1994年提出的一种信号传输模式的电平标准,它采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等优点,已经被广泛应用于串行高速数据通讯场合当中。

LVDS技术规范有两个标准,即TIA(电讯工业联盟)/EIA(电子工业联盟)的ANSI/TIA/EIA-644标准(LVDS接口也因此称为RS-644接口)与IEEE 1596.3标准。

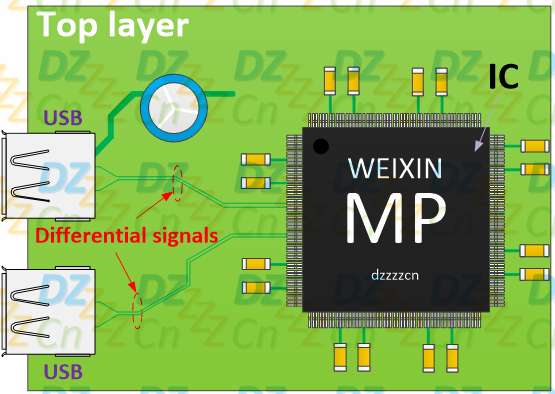

LVDS电平标准采用一对(两根)差分信号线传输数据。我们最常见的差分信号线就是USB(Universal Serial Bus, 通用串行总线),现如今,任何一台PC电脑上都会有USB接口,它可以用来连接U盘、键盘、鼠标、打印机、移动硬盘等等,如下图所示:

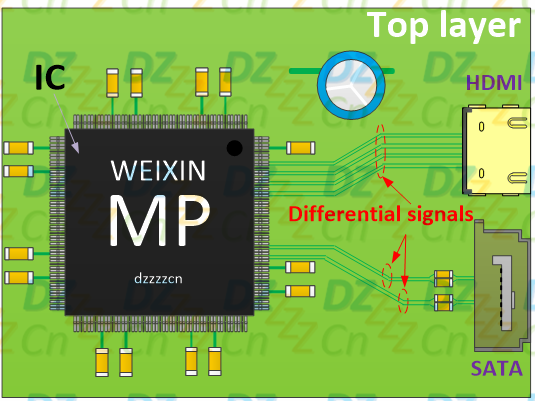

HDMI(High Definition Multimedia Interface, 高清晰度多媒体接口)是一种数字化音视频接口技术,适合影像传输的专用型数字化接口,它由4对差分线组成。我们使用的SATA(Serial Advanced Technology Attachment,串行ATA接口规范)硬盘也包含接收与发送两对差分信号线,如下图所示:

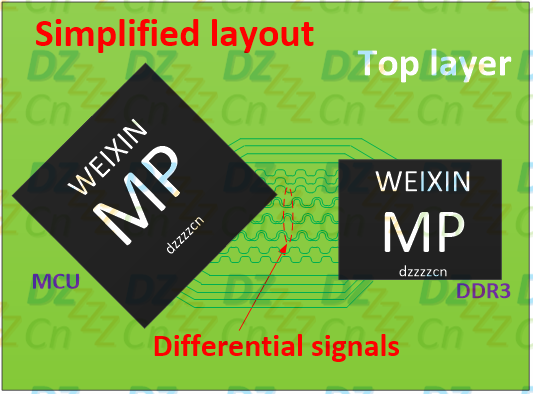

有过DDR3 SDRAM应用经验的读者也会发现有几对差分线,如下图所示:

很遗憾地告诉大家,以上几种接口的差分信号线使用的都不是严格意义上的LVDS电平标准(但很多基础概念都是相通的),换言之,不是所有的差分信号线都是LVDS电平标准,使用差分信号线进行数据传输的具体电平有很多种,LVDS只是其中之一。

比如,HDMI使用TMDS(Time Minimized Differential Signal, 最小化传输差分信号),DDR3使用SSTL(Stub series terminated logic,短截线串联端接逻辑)。HDMI(TMDS)、USB与SATA使用的电平标准与LVDS很相似,但从其规范来看并不是标准的LVDS(它们也是“低电压差分信号”,但不是我们这里所说的LVDS),不能认为是同一种电平标准(就如同我们不能认为5V TTL电平标准与5V CMOS电平标准是相同的,尽管看起来参数差别不大),而SSTL(包括SSTL_3、SSTL_2、SSTL_18、SSTL_15)与LVDS就完全不是一个东西了。

当然,只要是使用差分信号线进行数据的传输应用,它们对于PCB布线的要求都是大同小异的,这一点我们将在《高速PCB设计》专栏文章中详述。

尽管如此(上面都不是LVDS电平标准),LVDS电平标准接口的应用场合还是非常广泛,LVDS接口的液晶显示屏就是其中之一,它是LCD Panel的通用接口标准。那么到底是什么原因使得LVDS这么受青睐呢?我们从最基本的LVDS硬件收发器来谈谈起。

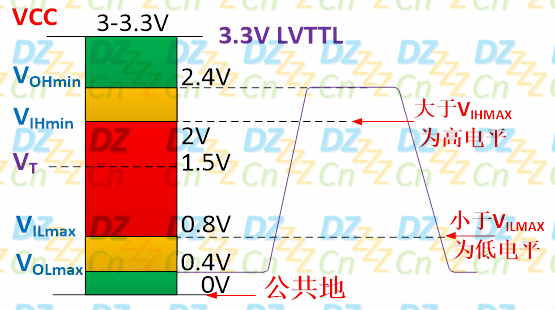

通常大多数低速数字逻辑电平(如TTL、CMOS)是以电压对参考地的幅值来判断是高电平还是低电平,如下图所示:

而LVDS却完全不一样,它是通过数据接收器同相端与反相端的电压相对大小判断高低电平的,而不是通过同相端或反相端对公共地(GND)。

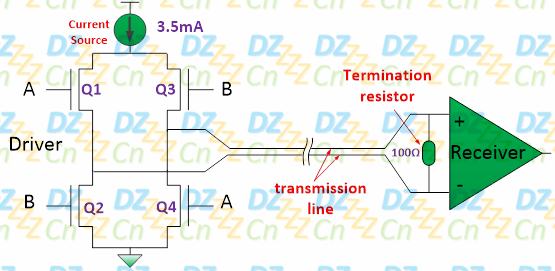

LVDS的发送器与接收器的基本结构如下图所示。它使用两根线(即差分信号线)来传输一个信号,并且使用恒流源(Current Source)驱动,即电流驱动型(而TTL、CMOS之类电平标准为电压驱动型)。

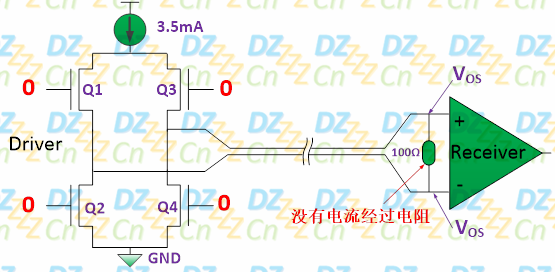

其中,驱动器(Driver)中的场效应管Q1、Q2、Q3、Q4(不一定是场效应管,因为LVDS技术规范主要侧重于LVDS接口的电气我、互连与线路端接,对于生产工艺、传输介质及供电电压无明确要求,也就是说,可以采用CMOS、GaAs或其它工艺实现,能抓到老鼠的黑猫白猫都是好猫)组成一个全桥开关电路,用来控制3.5mA恒流源的电流流动方向,接收器(Receiver)的同相与反相端之间并联了一个100欧姆的端接电阻,这样电流经过电阻即可产生电压,再经过接收器判断就形成了高低电平。

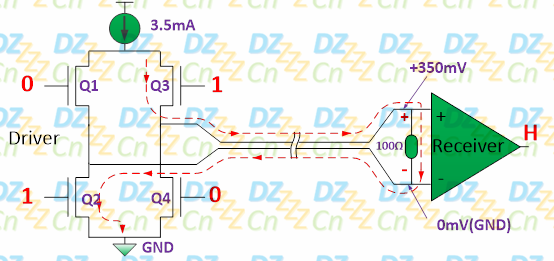

当Q2、Q3导通而Q1、Q4截止时,恒流源电流经Q3流向接收器,并向下穿过100欧姆端接电阻再返回至驱动端,最后经Q2到地(GND),3.5mA的电流在100欧姆电阻上产生350mV的压降,此时同相端电压高于反相端电压,输出为高电平“H”,如下图所示:

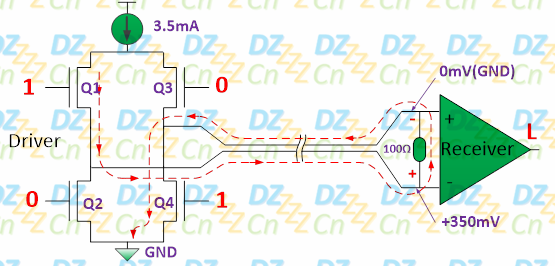

而当Q2、Q3截止而Q1、Q4导通时,恒流源电流经Q1向右流向接收器,并向上穿过100欧姆端接电阻再返回至驱动端,最后经Q4到地(GND),3.5mA的电流在100欧姆电阻上也产生350mV的压降,但此时同相端电压低于反相端电压,输出为高电平“L”,如下图所示:

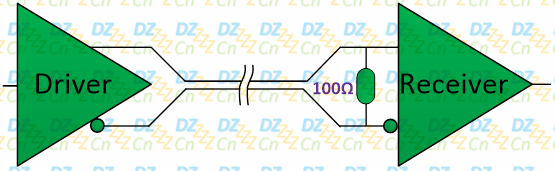

通常我们将LVDS接收器与发送器简化成类似下图所示:

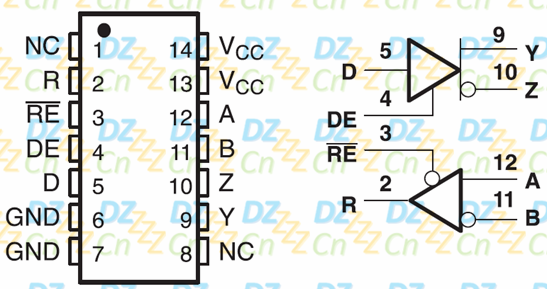

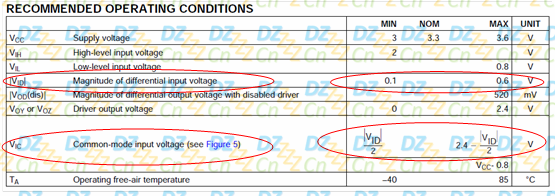

如下图所示(来自TI公司LVDS收发芯片SN65LVDS180数据手册)

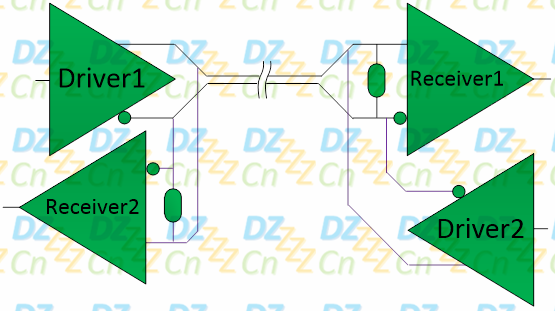

从LVDS结构原理可以看出,一对差分信号线只能够进行一个方向的数据传输,即单工通信(也称为点对点传输,point-to-point),但是我们常见的USB接口也只是使用一对差分信号线,为什么却可以双向传输呢?原因很简单,它是使用两对驱动器与接收器组合而成的,如下图所示:

这是一种半双工(half duplex)的配置结构,也就是说,在任意时刻差分信号线仍然只能是往一个方向传输数据,但可以分时进行双向数据传输,当驱动器1向接收器1发送数据时,驱动器2与接收器2相当于无效的,反之亦然。

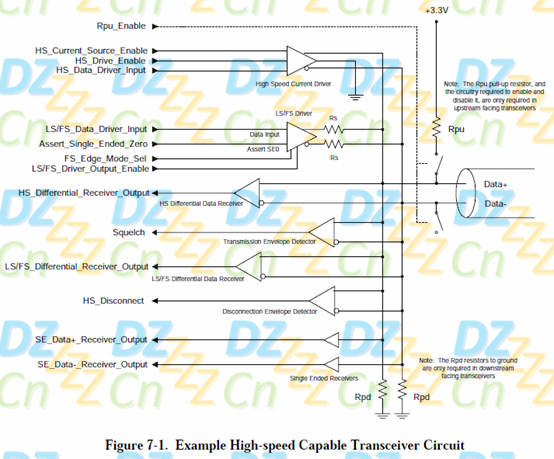

当然,USB总线的实际结构要复杂得多,如下图所示(来自USB2.0规范,扯远了)

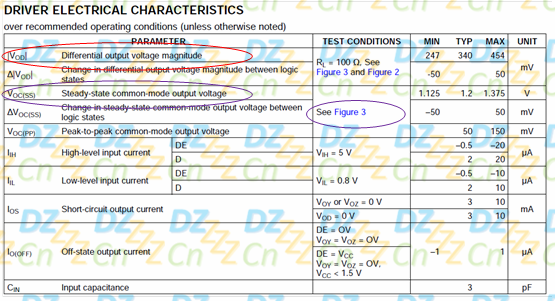

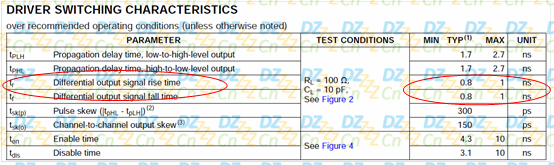

我们来看看如下图所示的LVDS驱动器电气参数(来自TI公司LVDS收发芯片SN65LVDS180数据手册)

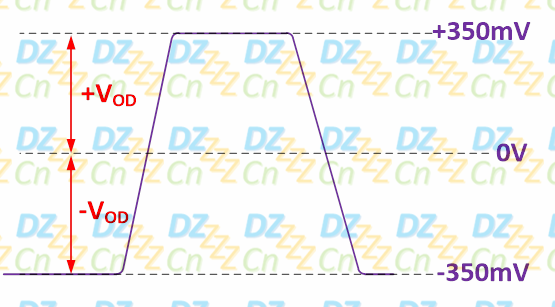

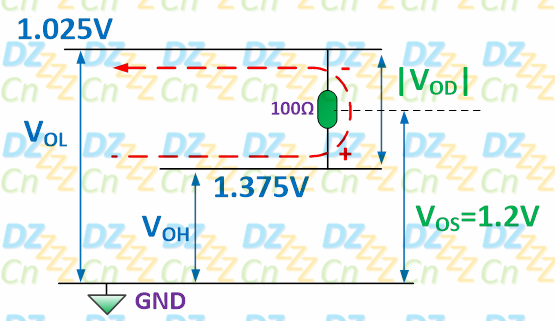

上表中的VOD(Differential output voltage magnitude)即驱动器的差分输出电压幅度,也就是前述在端接电阻上产生的350mV压降,我们可以用下图所示(注意:是差模信号):

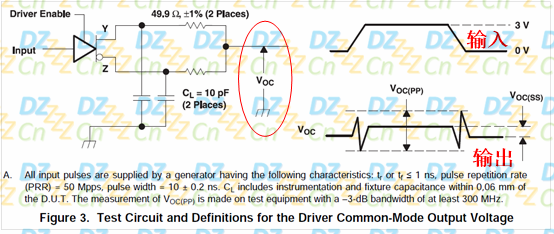

表中还有一个VOC(SS)(Steady-state common-mode output voltage)即稳态共模输出电压是个什么东西呢?我也不是很明白!咱们按图索骥找到数据手册中的Figure 3,如下图所示:

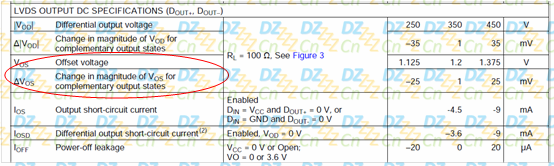

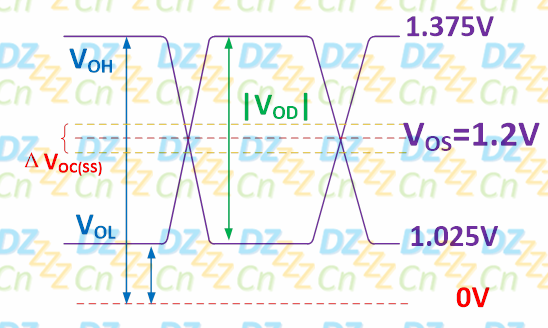

哦,原来是当驱动器输入数字信号(未转换成LVDS信号前)时,转换出来的LVDS信号电压对公共地的平均值,也称为VOS(Offset Voltage,),TI公司的其它数据手册有使用VOS如下图所示:(来自TI公司的LVDS收发芯片型号SN65LVDS049数据手册)

我们之前讲过,当使用LVDS电平标准传输高低电平时,接收端收到了+350mV或-350mV的压降只是差模信号,实际上还有一定的共模信号,它不影响接收器进行数据的判断。

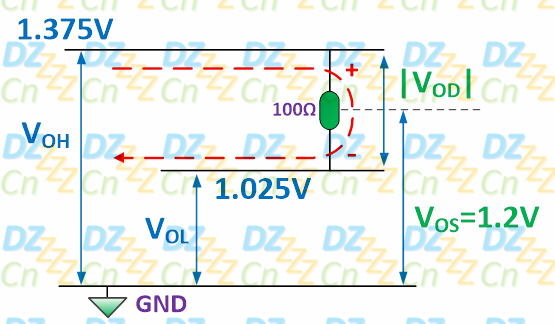

当驱动器向接收器发送高电平“H”时,其等效图如下所示(注意:这个等效图仅适合传输线非常短的条件下):

当驱动器向接收器发送低电平“L”时,其等效图如下图所示

综合以上两种等效电路,我们有如下图所示的电平波形图:

换言之,当LVDS进行高低电平切换时,电流源的电流在换向的瞬间,端接电阻流过的电流为零,因此端接电阻两端的电压就是VOS(电阻两端电压相同,因此没有压降,也没有电流),如下图所示:

当然,这个电流换向转换瞬间非常短,通常只有几百皮秒,如下图所示:

接收器的输入电气参数如下图所示:

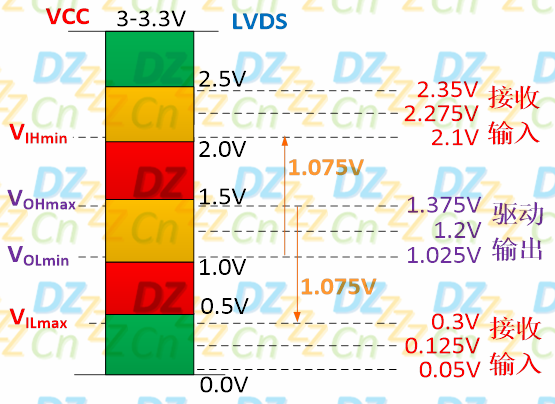

因此我们也可以用下图表示LVDS电平标准的噪声容限(关于噪声容限请参考《逻辑门2》)

从图中可以看到,LVDS电平标准的噪声容限约为1.075V(一般认为其噪声容限为 1V)这里我们只是根据TI数据手册画出电平标准图,没有做任何修改,不同厂家的信息可能略有不同。

导演,讲了半天还没提到为什么LVDS信号速度快、抗干扰能力强呀?为什么有些差分线串联了电容?为什么不同差分线的阻抗会不一样?了解了这些基础知识,我们下节再来讨论一下LVDS电平标准的这些特点。

-

CMOS

+关注

关注

58文章

5750浏览量

236266 -

HDMI

+关注

关注

32文章

1748浏览量

152560 -

接口

+关注

关注

33文章

8728浏览量

152102 -

lvds

+关注

关注

2文章

1049浏览量

66104 -

差分信号

+关注

关注

3文章

378浏览量

27791

发布评论请先 登录

相关推荐

如何利用低电压差分信号接口器件实现数据远距离传输的设计

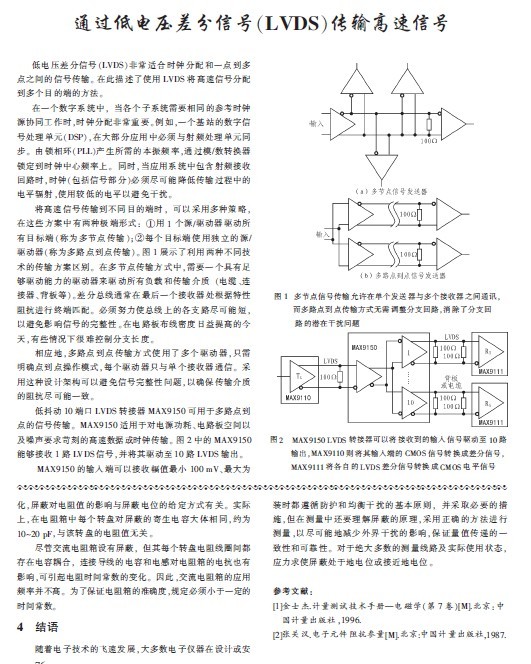

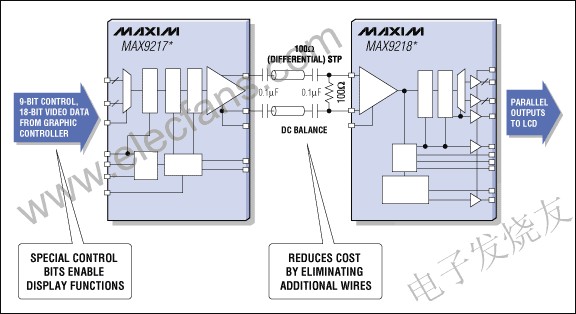

通过低电压差分信号(LVDS)传输高速信号

通过低电压差分信号(LVDS)传输高速信号

ADI推出多点低电压差分信号收发器ADN469xE

LVDS振幅差分信号技术的优势和劣势

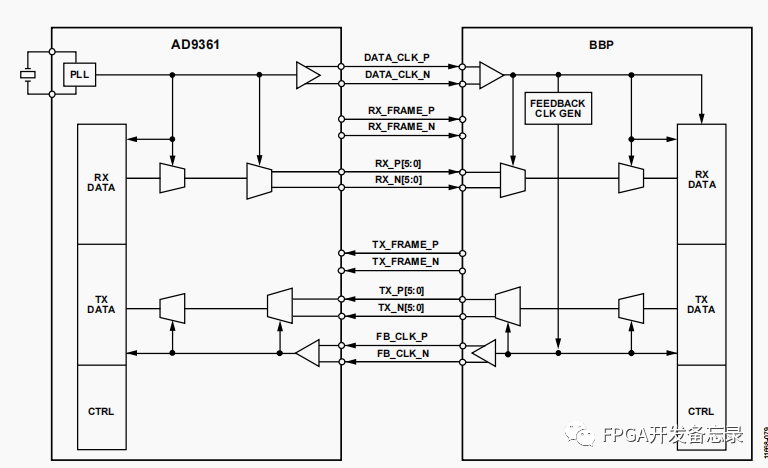

AD9361数据路径在低电压差分信号(LVDS)模式下运行

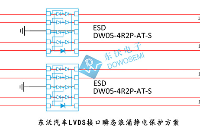

低电压差分信号(LVDS)接口浪涌静电放电防护电路图

一文详解LVDS低电压差分信号

一文详解LVDS低电压差分信号

评论