锁相环(PLL)频率生成电路广泛用于多个行业和应用中,包括基本的 FM 广播频段接收器、数字通信、航空航天、仪器仪表、雷达和电子战。锁相环用于生成从小于 1MHz 到数十 GHz 及以上的射频(RF)和中频(IF)信号。应用要求变化很大,锁相环设计和优化需要权衡考量功耗、相位噪声、频率调谐范围、频率分辨率和锁定时间等参数。

设计过程中必须权衡考量频率范围与相位噪声性能,这一点很重要,如果处理不当,常常会导致性能下降。宽带压控振荡器(VCO)以牺牲出色的相位噪声性能为代价,提供较宽的频率范围。相比之下,窄带VCO 以牺牲可达到的调谐范围为代价,提供更好的相位噪声。可以将多个窄带 VCO 多路复用,以实现更宽的调谐范围,但这通常不切实际——需要复杂的外部电路将电源切换给单个 VCO,并选择适当的 RF输出。

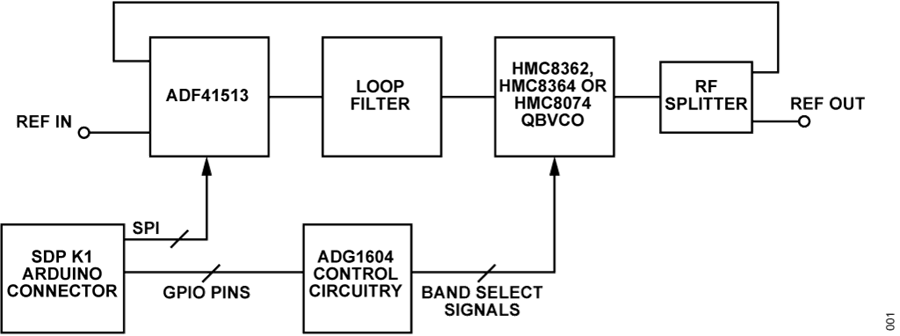

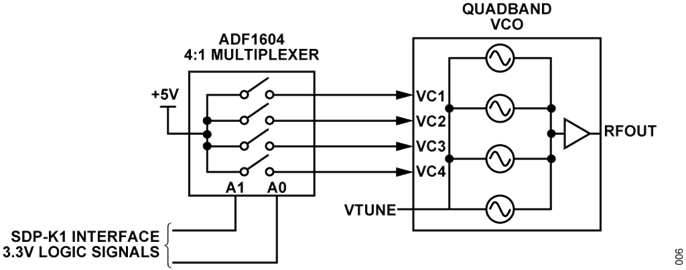

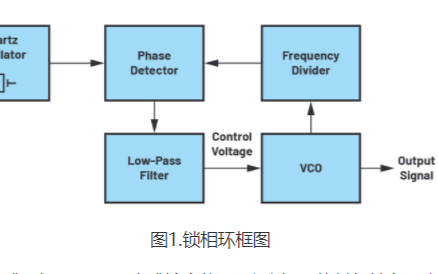

图 1 所示的电路包含一个集成式四频 VCO,由四个集成在单个封装中的窄带 VCO 组成(下文简称该电路为CN0568)。这种设计的优势在于:它保留了窄带 VCO 出色的相位噪声,同时还提供较宽的工作频率范围。VCO 频段通过板载多路复用器电路进行切换,该电路根据主机编程设置的频率从四个 VCO 中选择。

图 1. CN0568 功能框图

这种切换电路经过优化,可以提供快速 VCO 频段切换,减少了从最低频段到最高频段的总锁定时间。对于需要在宽频率范围内保持快速切换时间的应用,例如快速跳频,这是有利的。

对于需要高精度的相位再现的波束成形等应用,PLL内置的相位再同步和相位调整功能都非常有用。该电路兼容 Arduino 尺寸平台板,可以堆叠多个板,共用同一个数字接口。

电路描述

PLL 合成器

本电路选择 ADF41513 用作 PLL 频率合成器,它具有 1GHz 至 26.5GHz 宽工作频率范围,涵盖 3 种四频 VCO 的整个频率范围。在小数模式下,∑-Δ 调制器提供 sub-Hz 频率分辨率。ADF41513 还具有超低本底噪声性能,在整数模式下为-235 dBc/Hz,在小数模式下为-231 dBc/Hz,以实现出色的相位噪声性能。

基准输入

EVAL-CN0568-ARDxZ 可以进行配置,支持来自REFIN SMA 连接器的外部基准频率,或用于板载超低相位噪声 100MHz 晶体振荡器。具有 82fs 低抖动和-90 dBC/Hz 近载波相位噪声。默认情况下,该板配置采用板载晶体振荡器选项;通过移除 R8,并在 R28 中插入一个 0 Ω 电阻来选择外部输入。对于需要 100MHz 基准电压源的用例,推荐使用板载基准电压源。

环路滤波器

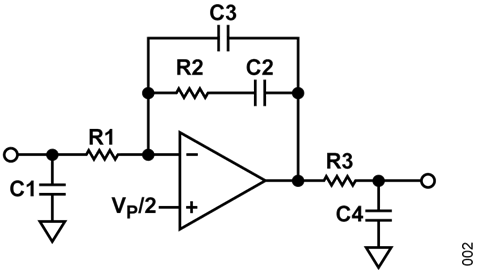

由于 ADF41513 PLL 的电荷泵的工作电压为 0 至3.3v,这 3 种四频 VCO 需要 1.0V 至 13.5V 调谐电压,因此需要具有增益的有源环路滤波器电路。环路滤波器的设计目标是在每个 VCO 频段的频率范围内尽可能提高稳定性,环路带宽约为 100kHz,相位裕量为 50°。当所选的 VCO 频段内的调谐灵敏度(频率与调谐电压斜率)发生变化时,环路滤波器带宽根据工作频率也会略微变化。环路滤波器设计用于使用 100 MHz 基准频率,如果需要使用其他基准频率,则需要重新设计。ADISimPLL 工具可用于确定合适的环路滤波器拓扑结构,并使用仿真模型计算所需带宽和相位裕量等必要的元件值。

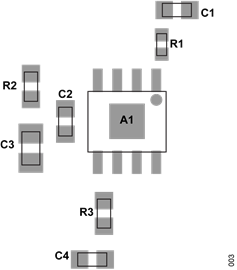

采用五阶环路滤波器拓扑,是因为它具有更高的带外滚降,以及更出色的 Σ-Δ 调制器噪声和杂散衰减性能。环路滤波器中选择使用的运算放大器是 ADA4625 ,它具有低噪声性能,可以使用轨到轨电源。图 2 显示使用的环路滤波器配置的示意图。图3 显示板载环路滤波器的尺寸。

图 2. 环路滤波器原理图

图 3. 环路滤波器尺寸

电压控制振荡器

HMC8074/HMC8362/HMC8364 四频 VCO 每个都由 4 个独立的窄带 VCO 内核组成,这些内核集成在单个 LFCSP 封装中。为对应的内核提供 5v 电源电压,如此可以选择每个内核。在任何给定时间内,只能启用一个内核,以确保输出缓冲放大器不被过驱动。因为每个内部 VCO 内核的窄带性能,这些四频 VCO 具有宽带 VCO 的频率范围,同时保持了出色的相位噪声性能。

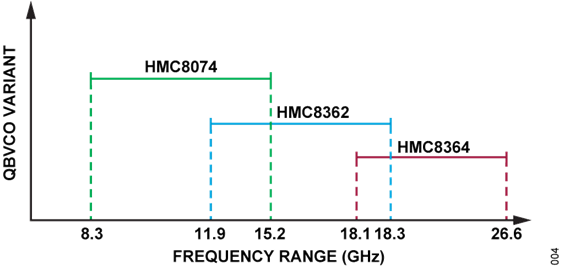

在给定器件版本的所有 4 个频段内,VCO 调谐曲线保持一致,因此可以使用单个环路滤波器来调节所有频段。这些四频 VCO还为功率敏感型应用提供 75mA 的低电流消耗(典型值),包括缓冲放大器。这三种四频 VCO 版本覆盖 8.3GHz 至 26.6GHz 的频率范围。每个四频VCO 的频率范围如下:

HMC8074:8.3 GHz至15.2 GHz

HMC8362:11.9 GHz至18.3 GHz

HMC8364:18.1 GHz至26.6 GHz

图 4. 四频 VCO 版本的频率范围

虽然 HMC8364 能够使用 ADF41513 的最大频率26.5GHz,但 EVAL-CN0568-ARDxZ 的工作频率范围限制在 24GHz。详细说明参见 频率灵敏度 部分。

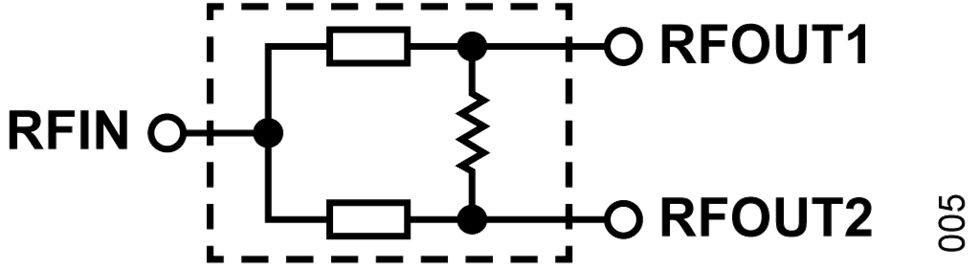

RF 分路器

宽带宽(1.8-28GHz)、1:2 RF 分路器将 VCO 输出拆分,分别输出到 CN0568 RF 输出端口和 PLL RF 反馈路径。选择这种分路器的主要原因在于,它具有2GHz 至 26.5GHz 宽工作带宽范围。这意味着,分频器可以在所有三种四频 VCO 的频率范围内使用。EP2K1+还具有 2.5W 高功率处理能力,尺寸小巧,为 4x4mm。

图 5. RF 分路器简化原理图

插入损耗在分路器的频率范围内变化,从 2GHz 时的 0.8dB(典型值)到 26.5GHz 时的 2.4dB。这个插入损耗必须加入到分路器的 3dB 损耗中,以提供在某个频率下,信号通过分路器遭受的总损耗。在HMC8364 版本电路板更高的工作频率下,因为ADF41513 的 RF 输入灵敏度随着频率的增加而增加,插入损耗会影响锁定。详细说明参见频率灵敏度部分。

相位再同步

当锁定到所需频率时,相位可以建立至相对于基准频率的任何一个相位偏移。ADF41513 具有相位再同步功能,对于给定的 RFOUT 频率,从基准电压源产生一个稳定的相位偏移。在相位关键型应用中,例如波束成形,这是一个重要功能。

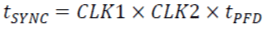

在第一次使能相位再同步后,用户在操作频率上选择相位偏移。如果改变频率,然后又变回原来的频率,则保持原来的相位偏移。当相位再同步使能时,内部定时器以下式所给出的间隔 tSYNC产生同步信号:

CLK1 和 CLK2 是 ADF41513 寄存器位域,在应用软件中编程设置。在编程设置时,必须使 tSYNC大于PLL 最坏情况下的锁定时间,以确保在 PLL 建立瞬态的最后一个周跳发生相位再同步。注意,如果使用相位再同步,即使在整数模式下运行,也必须使能Σ-Δ调制器。

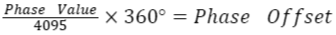

相位调整

可以使用相位值位域(在 CN-0568 应用软件中编程设置),按任何给定频率手动增加相位。可以使用以下公式生成相位偏移:

然后,相位会在每次向 ADF41513 的寄存器0写入时,按相位偏移量增加。在相位再同步模式下也是一样,必须使能∑-∆调制器来执行相位调整,即使是在整数模式下运行。

频率灵敏度

ADF41513 的最大输入频率为 26.5 GHz, HMC8364 四频 VCO 版本稍高一些,为 26.6 GHz。但是,当频率接近 24GHz 时,有许多因素(如本节所述)会影响性能并导致环路不能锁定。因此,指定该电路的最大工作频率为仅 24 GHz。在室温下使用时,指定工作频率为 24GHz。但是,如果温度升高,最大工作频率可能会降低。

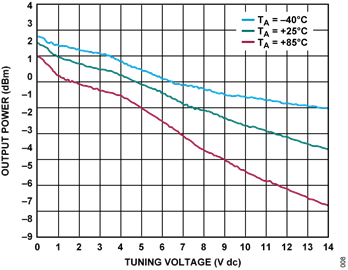

影响锁定的第一个因素是,HMC8364 VCO 输出功率会在频段 4 的频率增加时降低。具体参见图6 所示。

图 6. HMC8364 输出功率与频段 4 中整个温度范围下的调谐电压的关系

这种输出功率降低对电路的整体功率损耗有很大影响。在 23.9 GHz 到 26.6 GHz 范围内,输出功率下降了 6 dB。

RF功率分路器插入损耗也随着频率的增加而增加。在更高的工作频率下,这可以产生高达 1dB 的额外损耗,导致反馈环路的总损耗增加。

此外,ADF41513 的 RFIN 频率灵敏度随着工作频率的增加而增加。工作频率高于 24 GHz 时,这种灵敏度变得更加重要,因为受之前提到的会导致损耗的其他因素影响,会更难以达到所需的输出功率。RF 反馈路线可以重新设计,以便在较窄的频率范围内,在较高的频率下实现更低的插入损耗。但是,该电路的目标之一是演示所有三种四频 VCO 在最宽频率范围内的性能。另一种增加反馈信号功率的技术是:在反馈环路中添加一个放大器。请参见常见变化章节了解详细信息。

使用控制电路,根据应用软件中所选的频率来选择不同的 VCO 频段。GPIO 信号从 SDP-K1 Arduino连接器路由,以根据所需频率选择频段。对自定义固件执行写入,以传输这些 GPIO 控制逻辑信号,具体参见 CN0568 产品页面。参见 Circuit 电路评估和测试章节,了解有关加载自定义固件的详细信息。

压控振荡器频段选择电路的主要组件之一是 ADG1604 4:1 多路复用器。这将来自 LT3045 稳压器的+5v 电源电压通过多路复用器的 4 个开关中的一个馈送至对应的 VCO 频段电源。在控制电路中使用多路复用器可以确保一次只启用一个 VCO 内核,避免对 VCO 器件造成损坏。所有控制信号都包括滤波电感和电容,以衰减可能发生的噪声和干扰。图 7 所示为控制电路的简化框图,用于进行说明。(包含控制电路的电路板完整原理图在 CN0568 设计支持包中。)

图 7. VCO 频段选择,包含多路复用器

VCO 集成式输出缓冲器通过单刀双掷(SPDT)开关进行开关,该开关通过另一个 SDP-K1 GPIO 信号进行管控。默认情况下,该信号在应用软件建立连接后保持高电平。

频率更新序列

ADF41513 上的频率控制寄存器受到双重缓冲。这意味着,要改变 RF 输出频率,必须执行两个事件。首先,必须根据所需的新频率更新频率控制字寄存器。然后,对寄存器 0 执行写操作,以开始频率变化。每次在应用软件前面板上更新频率,会对总共4 个寄存器进行写入,包括寄存器 0 写入。这些寄存器必须按以下顺序写入:寄存器 6,寄存器 3,寄存器 1,然后是寄存器 0。

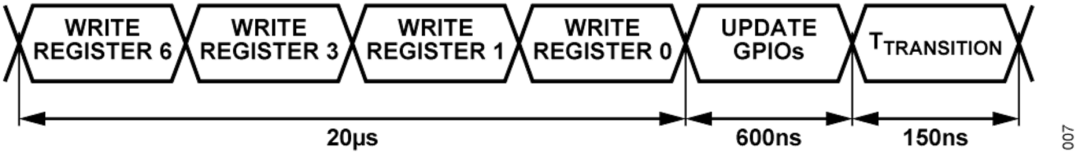

当使用不同 VCO 频段的频率更新到当前频率时,GPIO控制信号在寄存器写入后更新,如图8所示。

图 8. 频率更新序列

在寄存器 0 更新约 600ns 后,GPIO 更新。转换时间是变化的 GPIO 地址位和进行多路复用的对应输出开关之间的延迟时间。ADG1604 4:1 多路复用器的典型转换时间为 150ns。

电源调节

EVAL-CN0568-ARDxZ 由两个外部电源供电,它们连接至板载 SMA 连接器。+25v 提供给 V+SMA,6v 提供给 J1。ADF41513 电源根据 EV-ADF41513SDxZ 评估板上的默认电源分组进行分组。通过组合更多电源引脚来减少稳压器的数量,可能会在输出频谱中产生不必要的杂散。

提供给 J1 的+6v 电源为四个板载 LT3045 LDO 稳压器提供输入电压。选择 LT3045 稳压器的原因在于它具有出色的低噪声性能和 500mA 输出电流能力。这些稳压器为所有的+3.3V ADF41513 电源,以及四频 VCO 和晶体振荡器基准电压源的+5v 电源供电。通过在 SET 引脚上相应设置 RSET电阻,以配置每个稳压器的输出电压。参见 LT3045 数据手册获取更多详细信息。

通过 V+SMA,从外部电源将+25v 电源直接提供给有源环路滤波器电源。在供电路径中包括解耦电容,以减少干扰供电的外部噪声。

常见变化

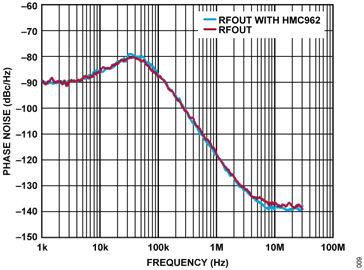

为了补偿 HMC8364 四频 VCO 版本在高于 24GHz时的输出功率降低,可以在 RFOUT 信号之后增加一个放大器。放大后的信号可以作为 ADF41513 RFIN 端口的反馈信号,以增大工作频率范围,最大频率为 26.5GHz。在图 9 中,相位噪声结果汇聚起来,将 HMC962 LNA 连接至 RFOUT 端口。为了比较,然后将其与不带LNA 的默认配置进行重叠。

图 9. RFOUT 上连接和不连接 HMC962 时的相位噪声比较

如图 9 所示,输出中包含 HMC962 时,相位噪声不会降低。在 24 GHz 时,放大器的增益约为 12.5 dB。在这种情况下,放大器的输入功率电平为-7.4 dBm。在输出端,测量到的功率电平为 5.23 dBm。这是一个非常合适的功率电平,因为它在 ADF41513 的24GHz 频率下的最大和最小灵敏度范围内。有关ADF41513灵敏度水平的更多信息,请参见数据手册。

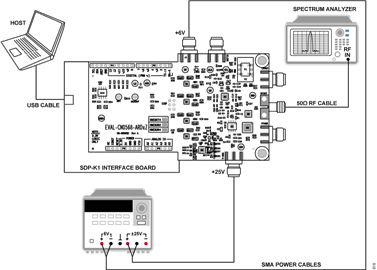

电路评估与测试

EVAL-CN0568-ARDxZ 板通过运行 CN0568 特定固件的 SDP-K1 控制板连接至主机。也可使用其他兼容 Arduino 的 3.3v 逻辑接口板,但需要进行固件开发。在首次连接时,演示软件装置中的自定义固件文件会加载到 SDP-K1 控制器板中。这通过将软件包中包含的十六进制文件复制到 SDP-K1 驱动器位置来实现。

设备要求

EVAL-CN0568-ARDxZ 评估板

EVAL-SDP-CK1Z 控制器板

运行 windows 7 或更高版本的 PC/笔记本电脑

频谱分析仪或相位噪声分析仪,具有合适的测量频率范围

2 × 香蕉插头,连接至 SMA 电源线

1 × 50 Ω RF/微波电缆,带 2.92mm 连接器

双电源,提供+25v 和+6v 输出电压

步骤

本节介绍设置 EVAL-CN0568-ARDxZ 任意版本,以在 RFOUT 端口上输出频率的一般步骤。关于详细说明,请参见 EVAL-CN0568-ARDxZ 用户指南。

将 EVAL-CN0568-ARDxZ 安装到 SDP-K1控制器板上。

通过 USB 电缆,将主机 PC/笔记本电脑连接至 SDP-K1 接口板。

将+6v(限流值 = 200mA)连接至 J1,+25v(限流值= 20mA)连接至 V+SMA。

将 50 Ω RF 电缆连接至频谱/相位噪声分析仪。

确保电源已关闭。如图 10 所示设置评估板。

接通两个电源

打开 CN0568 软件,选择正确的版本。然后按“连接”按钮,启动该器件。

选择工作频率范围内的频率,然后选择“更新频率”。

所选的频率将在频谱分析仪上显示。

图 10. 测试设置

结果

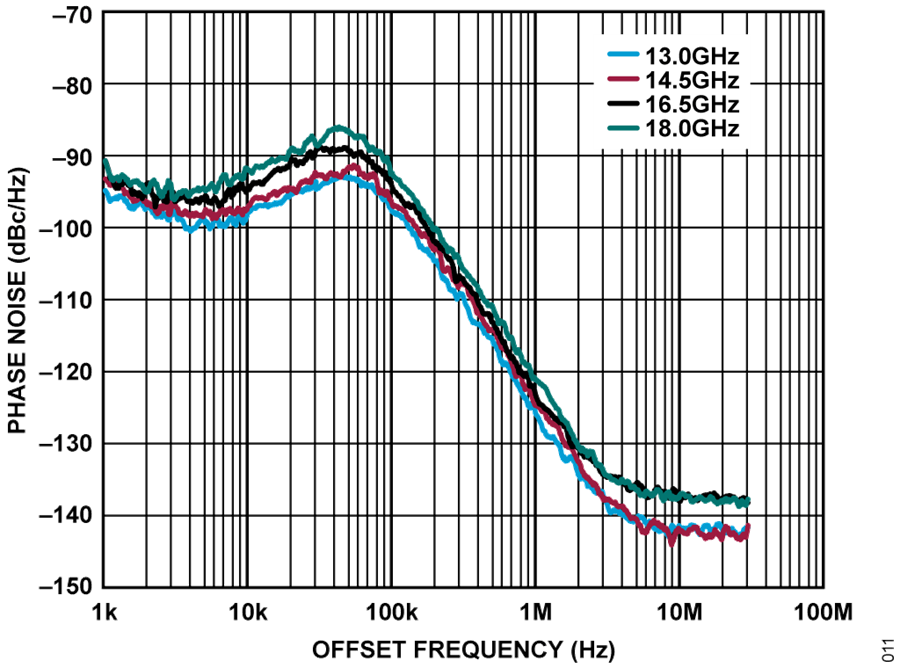

使用 HMC8362 四个频段的中心频率获取相位噪声结果图。图 11 显示重叠后的相位噪声图。

图 11. EVAL-CN0568-ARD2Z 相位噪声

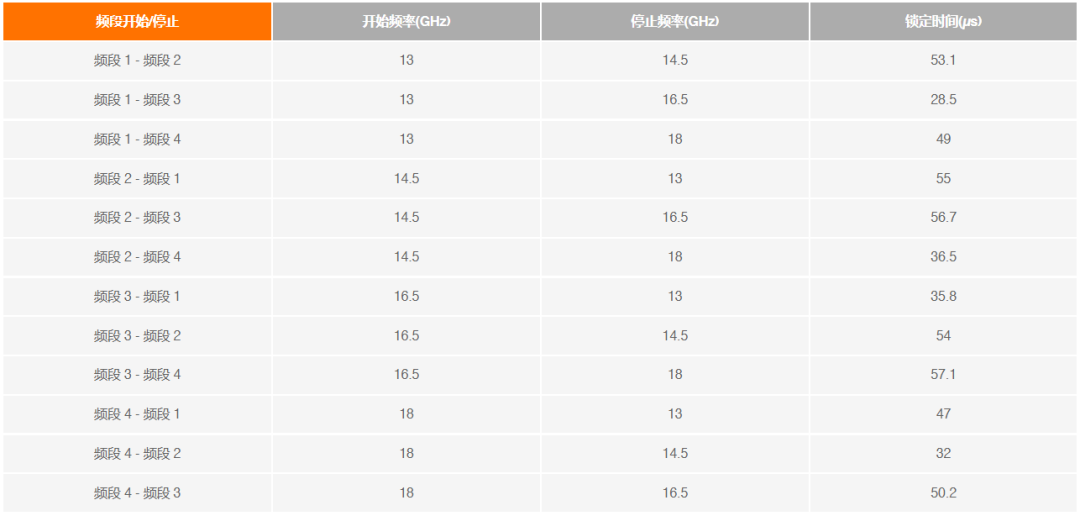

测试结果是使用默认的板载环路滤波器配置(100kHz 环路带宽)在室温下获得的。表 1 中还显示 EVAL-CN0568-ARD2Z 的电路的测量锁定时间。

表 1. EVAL-CN0568-ARD2Z 测量锁定时间

对于这些测量的锁定时间,锁定标准是频率已达到+/- 10kHz 停止频率,且随后没有偏离该阈值。ADISimPLL 用于验证预期得到的模拟锁定时间,该时间与这些测量值非常接近。

审核编辑:刘清

-

锁相环

+关注

关注

35文章

586浏览量

87803 -

振荡器

+关注

关注

28文章

3833浏览量

139153 -

接收器

+关注

关注

14文章

2473浏览量

71963 -

pll

+关注

关注

6文章

777浏览量

135199 -

VCO

+关注

关注

13文章

190浏览量

69220

原文标题:集快速开关、高性能PLL和四频VCO于一体的锁相环频率生成电路

文章出处:【微信号:ADI智库,微信公众号:ADI智库】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

锁相环常见问题解答

一文读懂锁相环(PLL)那些事

基于高压VCO的高性能PLL设计

【模拟对话】锁相环(PLL)基本原理

驱动高压锁相环频率合成器电路中的VCO详细分析

集快速开关高性能PLL和四频VCO于一体的锁相环频率生成电路介绍

集快速开关高性能PLL和四频VCO于一体的锁相环频率生成电路介绍

评论