01导语:

晶振在布局时,一般是不能放置在PCB边缘的,今天以一个实际案例来进行讲解。

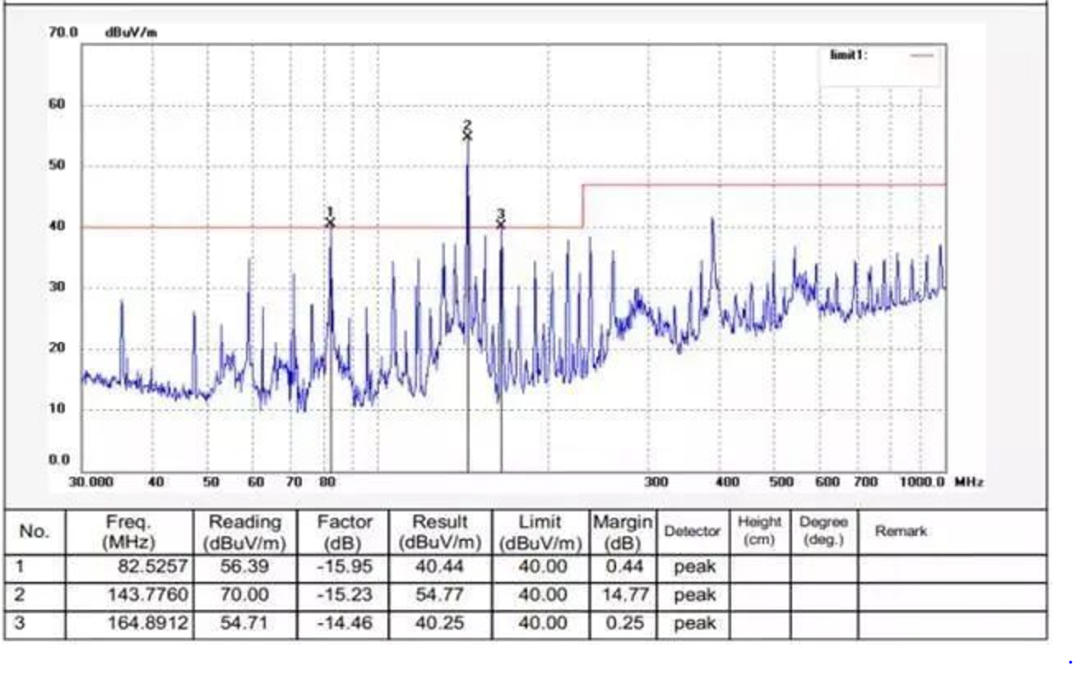

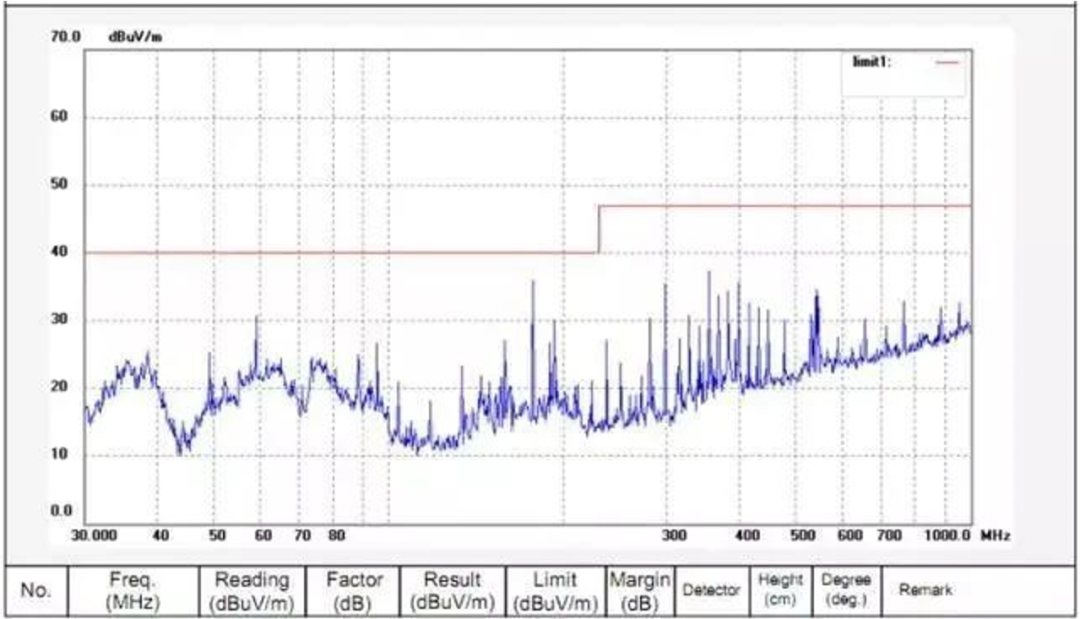

某行车记录仪,测试的时候要加一个外接适配器,在机器上电运行测试时发现超标,具体频点是84MHz、144MHz、168MHz,需要分析其辐射超标产生的原因,并给出相应的对策,辐射测试数据如下:

图1:辐射测试数据

一.辐射源头分析

该产品只有一块PCB,板子上有一个12MHz的晶体。其中超标频点恰好都是12MHz的倍频,而分析该机器容易EMI辐射超标的屏和摄像头,发现LCD-CLK是33MHz,而摄像头MCLK是24MHz。

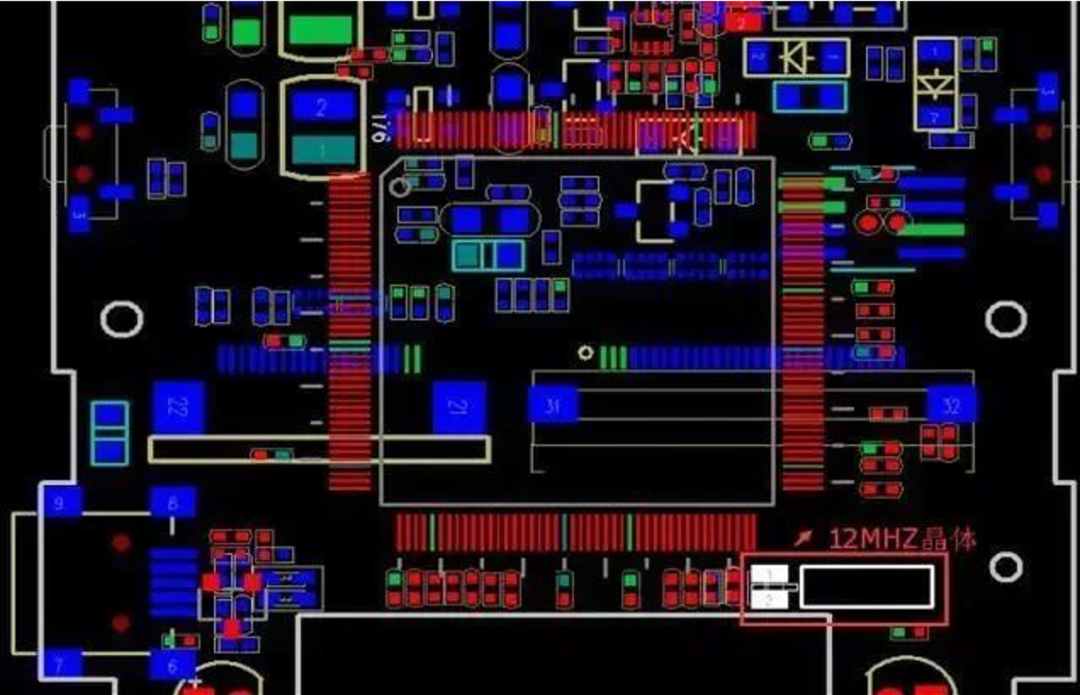

通过排除法,发现去掉摄像头后,超标点依然存在,而通过屏蔽12MHz晶体,超标点有降低,由此判断144MHz超标点与晶体有关,PCB布局如下:

图2:PCB布局图

二. 辐射产生原理

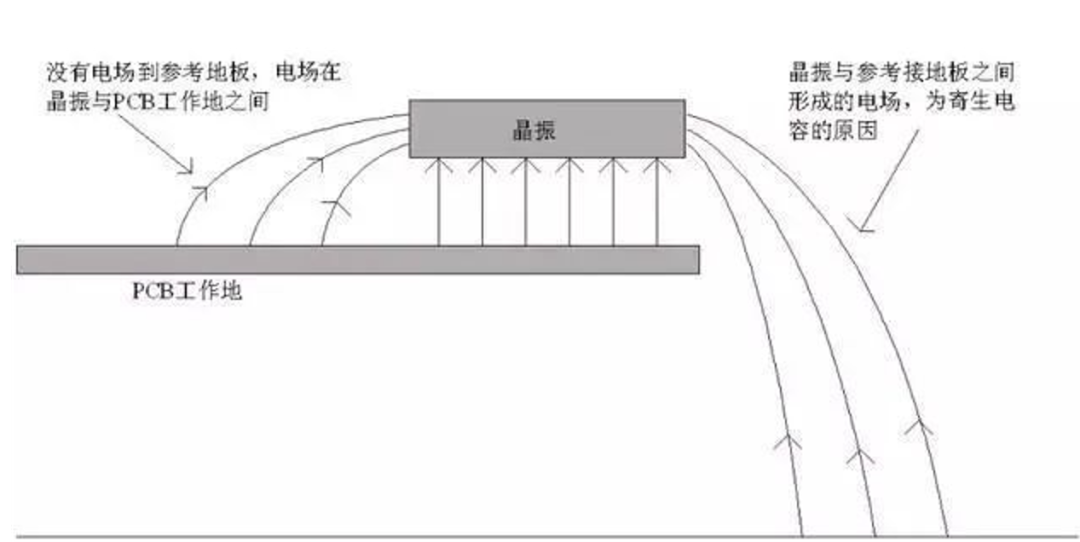

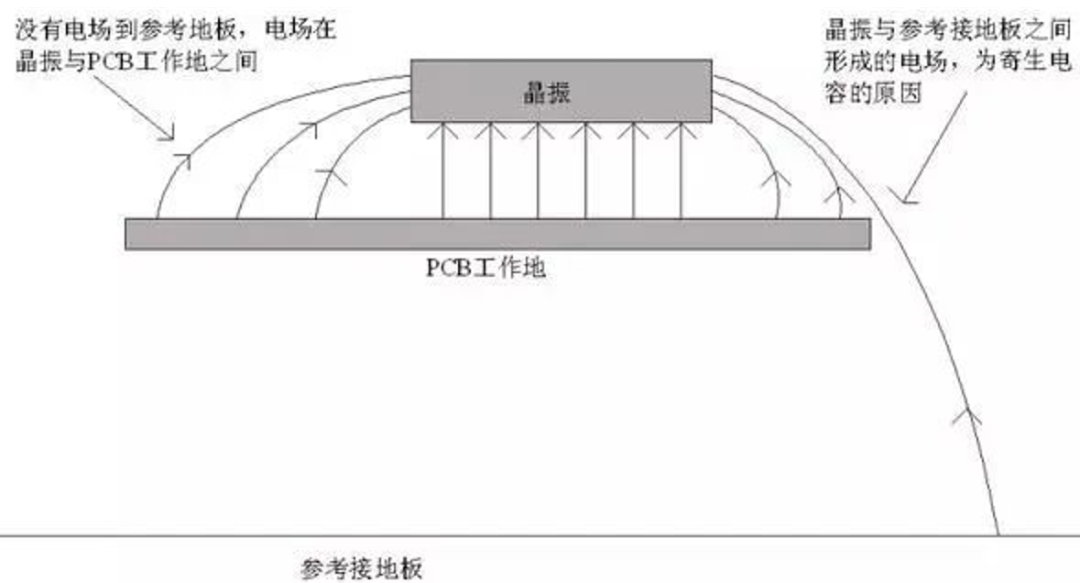

从PCB布局可以看出,12MHz的晶体正好布置在了PCB边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与实验室中参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶体与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越大,晶体在PCB边缘与在PCB中间时电场分布如下:

图3:PCB边缘的晶振与参考接地板之间的电场分布示意图

图4:PCB中间的晶振与参考接地板之间的电场分布示意图

从图中可以看出,当晶振布置在PCB中间,或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地之间,即在PCB内部,分布到参考接地板的电场大大减小,导致辐射发射就降低了。

三.处理措施

将晶振内移,使其离PCB边缘至少1cm以上的距离,并在PCB表层离晶振1cm的范围内敷铜,同时把表层的铜通过过孔与PCB地平面相连。经过修改后的测试结果频谱图如下,从图可以看出,辐射发射有了明显改善。

四.思考与启示

高速的印制线或器件与参考接地板之间的容性耦合,会产生EMI问题,敏感印制线或器件布置在PCB边缘会产生抗扰度问题。

如果设计中由于其他一些原因一定要布置在PCB边缘,那么可以在印制线边上再布一根工作地线,并多增加过孔将此工作地线与工作地平面相连。

-

pcb

+关注

关注

4319文章

23099浏览量

397855 -

晶体

+关注

关注

2文章

1354浏览量

35426 -

晶振

+关注

关注

34文章

2866浏览量

68033 -

辐射

+关注

关注

1文章

598浏览量

36340 -

布局

+关注

关注

5文章

269浏览量

25013

原文标题:【案例分析】晶振摆放位置是有讲究的!

文章出处:【微信号:创易栈,微信公众号:创易栈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶振知识入门

晶振选型都有哪些讲究?

测量晶振要注意,探头也有讲究,不然会导致晶振不起振!

晶振摆放位置是有讲究的!

晶振摆放位置是有讲究的!

评论