1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64;win7/32;win10/64

软件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

3.2.1主要功能

1)产生基带原始数据

2)位同步信号提取

3.2.2主要性能指标

1) 发送端

系统时钟:50MHz

基带数据码率:1.5625Mbps

数据内容:“11111010”循环码

2) 接收端

系统时钟:50MHz

同步方式:超前-滞后型锁相环位同步

同步精度:1/8 码元宽度

3 程序结构框图说明

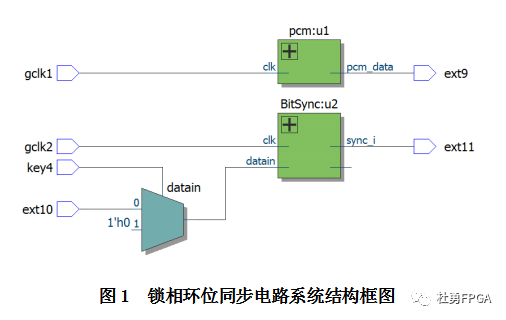

锁相环位同步电路系统主要由基带数据生成模块(pcm.v)、位同步模块(BitSync.v)组成。

基带数据生成模块生成的原始数据(1.5625Mbps)送至开发板上扩展口的第9脚,经短接线由第10脚送回FPGA芯片;位同步模块从接收到的原始数据中采用锁相环法提取位同步信号,提取出的位同步信号由扩展口的第11脚输出。为真实的验证位同步通信功能,发送端(pcm.v)的时钟由CRD500开发板上的X1晶振驱动,接收端(BitSync.v)的时钟由X2晶振驱动。

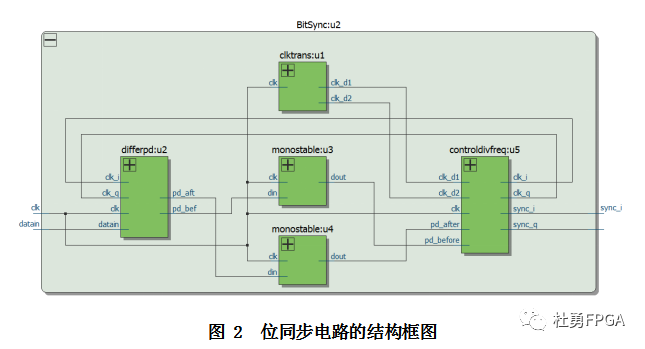

位同步电路的结构框图如图2所示。

实例采用超前-滞后型锁相环位同步电路实现位同步的提取功能,电路主要由鉴相模块(differpd.v)、双相时钟模块(clktrans.v)、单稳触发器模块(monostable.v)和控制分频模块(controldivfreq.v)组成。

审核编辑:刘清

-

锁相环

+关注

关注

35文章

588浏览量

87816 -

数字信号处理

+关注

关注

15文章

562浏览量

45911 -

同步电路

+关注

关注

1文章

60浏览量

13319 -

FPGA芯片

+关注

关注

3文章

246浏览量

39823

原文标题:锁相环位同步(Quartus/Verilog/CRD500)

文章出处:【微信号:杜勇FPGA,微信公众号:杜勇FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文详解锁相环位同步

一文详解锁相环位同步

评论