1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64;win7/32;win10/64

软件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

3.2.1主要功能

1)产生基带原始数据

2)帧同步信号提取

3.2.2主要性能指标

1) 发送端

系统时钟:50MHz

基带数据码率:195.3125kbps

数据内容:帧长16位,帧同步字长7位,同步字为1011000

2) 接收端

系统时钟:发送端送来的数据时或信号,195.3125kbps

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数可通过修改程序参数快速设置。

3 程序结构框图说明

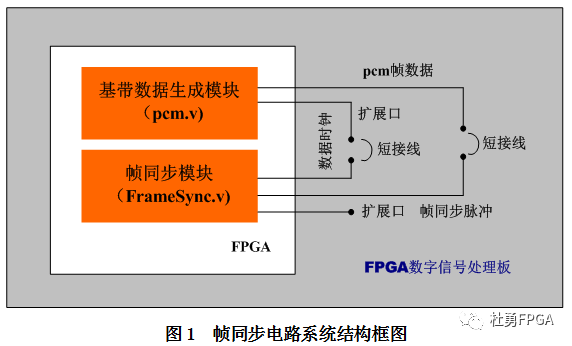

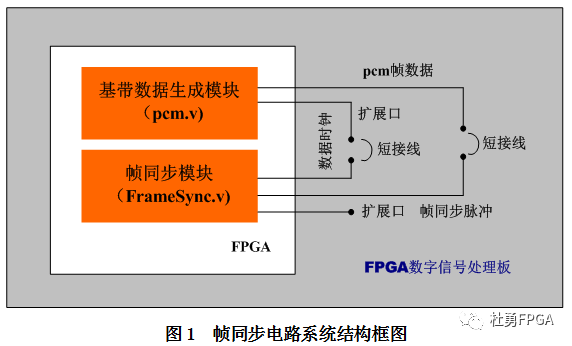

帧同步电路系统主要由基带数据生成模块(pcm.v)、帧同步模块(FrameSync.v)模块组成。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:插值法帧同步(Quartus/Verilog/CRD500)

文章出处:【微信号:杜勇FPGA,微信公众号:杜勇FPGA】欢迎添加关注!文章转载请注明出处。

相关推荐

本文介绍了集中式插入法帧同步系统的原理,分析了帧同步系统的工作流程。采用模块化的设计思想,利用VHDL设计了

发表于 11-11 13:36

•4894次阅读

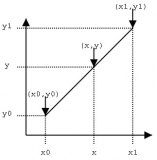

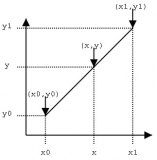

线性插值法(linear interpolation),是指使用连接两个已知量的直线来确定在这两个已知量之间的一个未知量的值的方法。

![的头像]() 发表于

发表于 12-24 10:44

•1w次阅读

如何用MATLAB拉格朗日插值法作图

发表于 11-03 16:27

{:23:}x,y,z为三组向量,散点图为一个半球型,怎么用插值法把它拟合成一个曲面,求助!!!

发表于 06-09 12:27

本身之间彼此不同的特性实现同步。这里采取第一种方法——连贯式插人法实现帧同步。所谓连贯式插入法就

发表于 08-11 16:22

本身之间彼此不同的特性实现同步。这里采取第一种方法——连贯式插人法实现帧同步。所谓连贯式插入法就

发表于 08-11 17:44

例如:我电脑上有一个表格表格51015300131622400252831500334149现在我有两个数分别是 7和350,怎么查这个表,通过插值法求出值?求大神指导

发表于 09-21 10:01

帧同步通常采用的方法有逐位调整法和置位调整法,对比分析哪个好?采用置位调整法设计帧

发表于 04-14 06:34

提出了一种数字接收机中符号同步的硬件设计方案。该方案属于异步采样恢复法,其插值滤波器的设计采用了理想插值

发表于 07-05 16:33

•17次下载

帧同步,帧同步是什么意思

在数字通信时,一般总是以一定数目的码元组成一个个的“字”或“句”,即组成一个个的“群”进行传输

发表于 03-17 17:30

•2.4w次阅读

针对传统的双线性插值法在对图像进行插值后会不可避免的产生边缘模糊的问题,提出了一种改进的线性插值法

发表于 08-20 12:01

•29次下载

为了在LabVIEW平台下更方便的处理非均匀采样的心电信号,文中研究了心电信号的时域和频域插值算法。首先采用了拉格朗日插值法、牛顿

发表于 03-15 17:10

•61次下载

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数

![的头像]() 发表于

发表于 02-08 11:48

•1368次阅读

基带数据生成模块生成的原始数据(1.5625Mbps)送至开发板上扩展口,经短接线由第35脚送回FPGA芯片;数据生成的同步时钟信号也经扩展口硬件环回至帧同步模块。为便于测试环路同步及

![的头像]() 发表于

发表于 02-08 11:50

•1089次阅读

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数

![的头像]() 发表于

发表于 02-10 14:00

•822次阅读

插值法帧同步解析

插值法帧同步解析

评论