1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64(推荐);win7/32;win10/64

软件:Quartus13.1/ModelSimSE 10.1c/Verilog HDL/Matlab2014a

2 主要功能及性能指标

2.1 主要功能

1)可产生ASK、FSK、PSK、单频信号、三角波、锯齿波、方波

2)载波频率、调制参数等波形参数可设置

3)可通过串口设置信号参数

2.2 主要性能指标

1)系统时钟:50MHz

2)串口协议:9600bps波特率、1位起始位、8位数据位、1位停止位、无校验位

3)载波频率范围:1MHz~4.75MHz可变,步进250kHz

4) 基带信号码速率范围:100kHz~475kHz,步进25kHz

5)三角波频率范围: 6kHz~98kHz,共16种频率可设置

6) 锯齿波频率范围: 12kHz~195kHz,共16种频率可设置

7)方波频率范围:50kHz~237.5kHz,步进12.5kHz

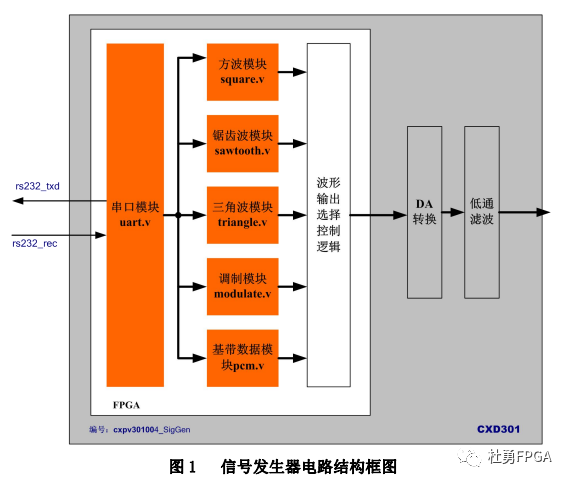

3 程序结构框图说明

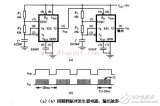

信号发生器电路程序主要串口通信模块(uart.v)、方波模块(square.v)、锯齿波模块(sawtooth.v)、三角波模块(triangle.v)、基带数据模块(pcm.v)和调制模块(modulate.v)组成。

uart.v模块完成与计算机之间的串口通信,接收串口发出的指令,并将接收到的指令回送至计算机,验证指令传输的正确性。串口接收的指令送至各信号波形产生模块,产生相应参数的信号波形。

方波模块(square.v)、锯齿波模块(sawtooth.v)、三角波模块(triangle.v)分别根据指令参数产生方波、锯齿波和三角波信号。基带数据模块产生8比特循环的基带数据11111010,并将基带数据送至调制模块modulate.v。modulate.v模块产生正弦波、ASK、PSK和FSK信号。

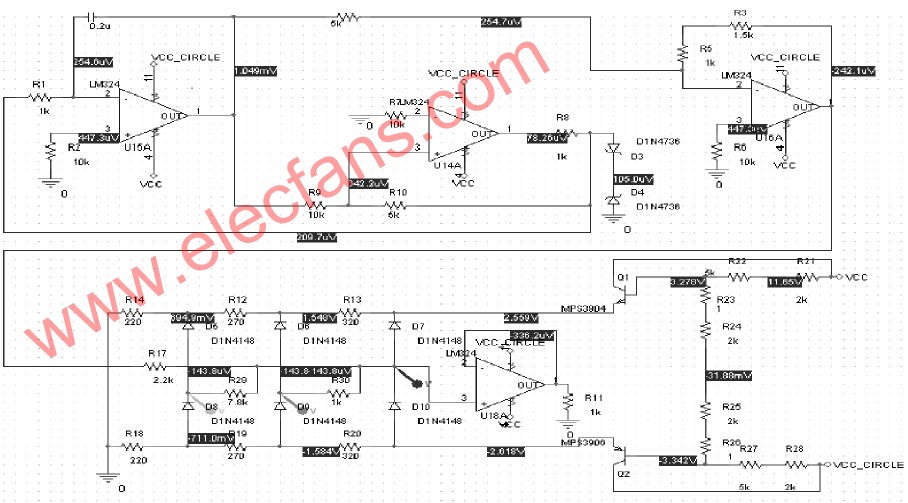

波形输出选择控制逻辑根据串口指令输出对应的波形信号,经信号处理板上的DA转换及滤波电路后,形成模拟波形输出。

审核编辑:刘清

-

滤波电路

+关注

关注

46文章

633浏览量

69605 -

FSK

+关注

关注

14文章

114浏览量

58353 -

信号发生器

+关注

关注

28文章

1460浏览量

108689 -

串口通信

+关注

关注

34文章

1620浏览量

55451 -

PSK

+关注

关注

1文章

27浏览量

20975

原文标题:信号发生器电路(Quartus/Verilog/CRD500)

文章出处:【微信号:杜勇FPGA,微信公众号:杜勇FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

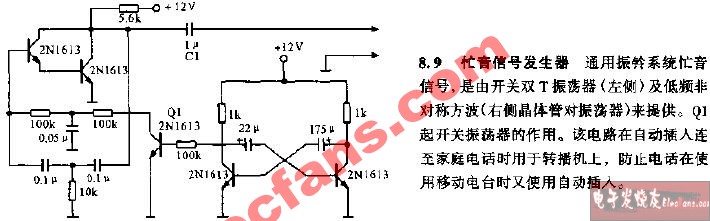

信号发生器电路简析

信号发生器电路简析

评论