ChatGPT在后端设计中有什么应用?ChatGPT懂后端EDA工具么?

本以为ChatGPT对于IC后端设计帮助应该不大,毕竟它非常依赖EDA工具,它对于EDA工具这种非常专业的、非常Custom的东西了解和训练的数据应该不多,所以可能帮不上什么忙。

所以我在基本后端知识、EDA工具的使用方面问了ChatGPT,我们看一下它的回复,整体的结果还是有点超出我的想象的。

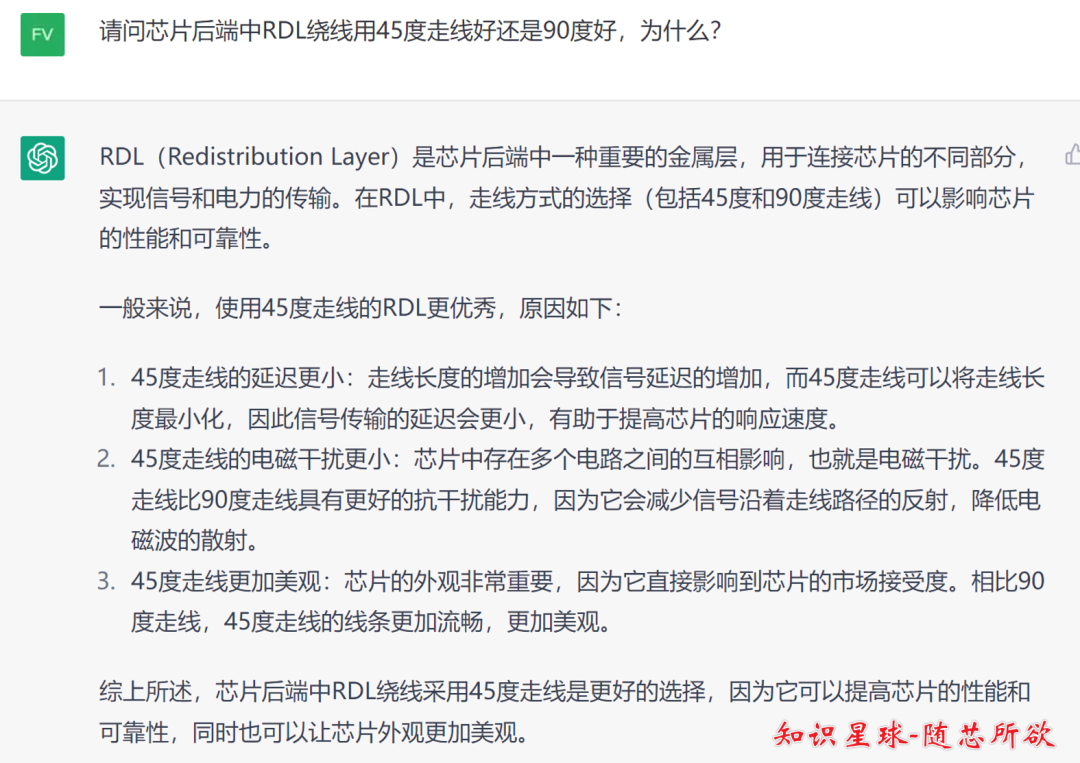

1、后端中的一些知识

从中可以看出工具给的回复还是有一些参考性的,从中我们能找到一些想要的结果。

2、ChatGPT对于EDA工具以及Flow的理解

从下面的回复中可以看出ChatGPT对于DC做综合的流程还是有一个大概的了解的,且说的内容也都是大体正确的,某些命令可能有些问题(比如读入时序约束文件一般用read_sdc而非read_file,设置周期也是在sdc里面创建clock或者generate clock,而非set_clock_period),其他的大问题基本上没啥。

问:麻烦写一个用Synopsys公司的design compiler软件做逻辑综合的教程

ChatGPT的回答:

好的,下面是一个使用Synopsys公司的Design Compiler软件进行逻辑综合的简单教程。

步骤1:准备设计文件和约束文件

在使用Design Compiler进行逻辑综合之前,必须准备好设计文件和约束文件。设计文件通常是Verilog或VHDL代码,而约束文件包含时序和其他综合约束。确保这些文件在同一个目录下,并且已经准备好进行综合。

步骤2:启动Design Compiler

打开终端窗口,输入dc_shell命令启动Design Compiler。dc_shell是Design Compiler的主要交互式控制台。在dc_shell控制台中,可以输入各种命令,例如编译、优化、综合等。

步骤3:设置工作目录和综合库

在Design Compiler中,必须指定工作目录和综合库。工作目录是当前正在使用的目录。使用cd命令更改工作目录。综合库包含所有必要的库文件,例如模拟模型、物理库和逻辑库。使用以下命令将综合库添加到Design Compiler中:

set target_library

其中,library_name是综合库名称。可以使用list_libraries命令列出所有可用的库。例如,使用以下命令列出所有库:

list_libraries

步骤4:读取设计文件和约束文件

使用以下命令在Design Compiler中读取设计文件和约束文件:

read_file

read_file

其中,design_file_name是设计文件的名称,constraint_file_name是约束文件的名称。如果文件位于当前工作目录中,则不需要输入完整路径。

步骤5:综合设计

使用以下命令对设计进行逻辑综合:

compile -map_effort high -area_effort high

其中,top_module_name是顶层模块的名称。map_effort和area_effort参数控制综合的时间和面积的优化程度。通常,将它们设置为“high”可以获得最佳的综合结果。

步骤6:分析综合结果

使用以下命令分析综合结果:

report_area

report_timing

report_power

这些命令将分别显示面积、时序和功耗报告。在综合完成后,应该始终检查这些报告,以确保综合结果符合要求。

步骤7:保存综合结果

使用以下命令将综合结果保存为Verilog网表文件:

write_verilog

其中,netlist_file_name是要保存的网表文件名。

这是一个简单的使用Synopsys公司的Design Compiler软件进行逻辑综合的教程。请注意,这只是一个基本的示例,并请注意,这只是一个基本的示例,并且Design Compiler拥有许多功能和选项,可以根据需要进行自定义和调整。在实际使用中,您可能需要更深入地了解Design Compiler的功能和选项,并调整综合设置以获得最佳结果。

以下是一些有用的Design Compiler命令和选项:

set_input_delay:设置输入延迟

set_output_delay:设置输出延迟

set_clock_period:设置时钟周期

set_max_area:设置最大面积限制

set_max_fanout:设置最大负载限制

set_max_delay:设置最大延迟限制

set_dont_touch:设置不综合的信号或模块

此外,Design Compiler还提供了许多优化选项,例如综合策略、综合限制和优化级别等。根据实际需求进行适当调整可以获得更好的综合结果。

最后,请注意Design Compiler是一款商业软件,需要购买许可证才能使用。此外,Design Compiler还有许多其他工具和插件,例如PrimeTime和Formality等,可以进行时序分析和形式验证等操作。如果需要使用这些工具,请参阅Synopsys公司的官方文档以获取更多信息。

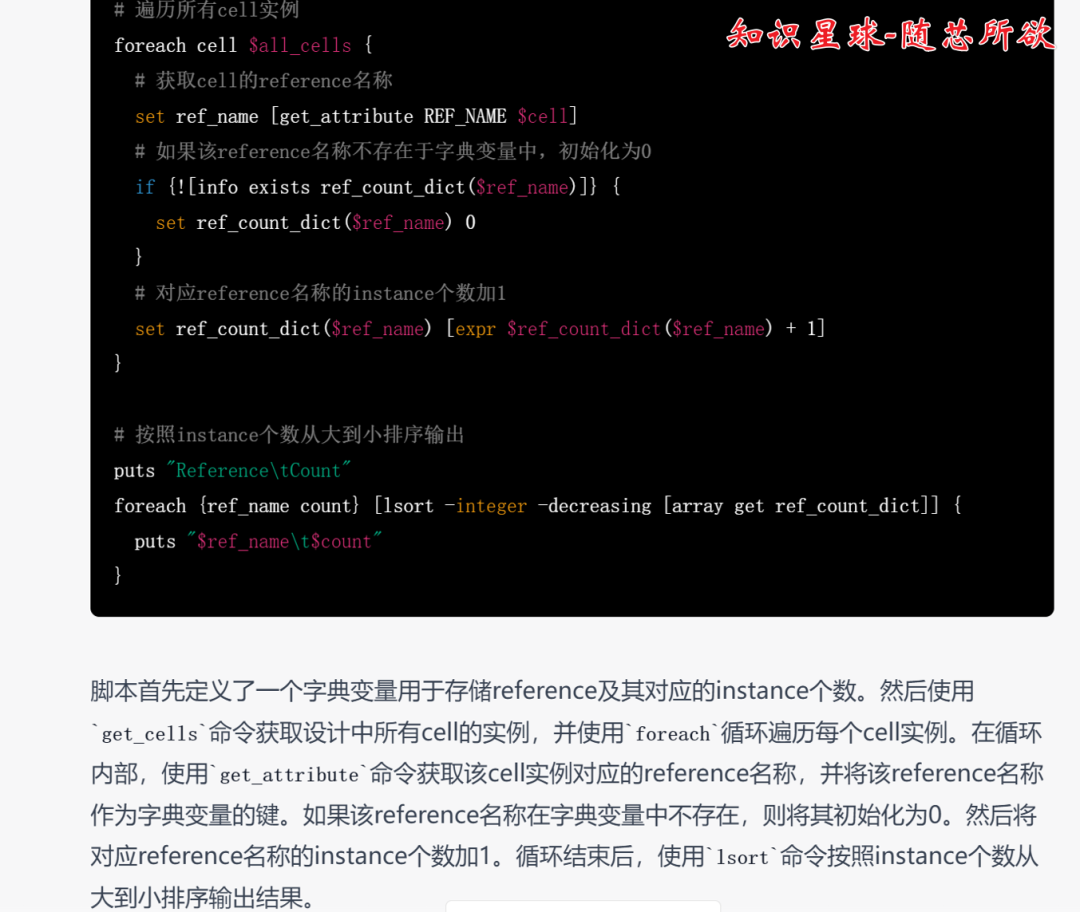

3、后端工具内的tcl脚本的编写

ChatGPT给出的脚本:

# 定义一个字典变量用于存储reference及其对应的instance个数

set ref_count_dict {}

# 获取设计中所有cell的实例

set all_cells [get_cells -hier *]

# 遍历所有cell实例

foreach cell $all_cells {

# 获取cell的reference名称

set ref_name [get_attribute REF_NAME $cell]

# 如果该reference名称不存在于字典变量中,初始化为0

if {![info exists ref_count_dict($ref_name)]} {

set ref_count_dict($ref_name) 0

}

# 对应reference名称的instance个数加1

set ref_count_dict($ref_name) [expr $ref_count_dict($ref_name) + 1]

}

# 按照instance个数从大到小排序输出

puts "Reference Count"

foreach {ref_name count} [lsort -integer -decreasing [array get ref_count_dict]] {

puts "$ref_name $count"

}

从中能看出几个问题:

1、ChatGPT混用了字典和array,下面用的是array get,前面却说的是字典dict。

2、另外在get_cells的时候需要把hier的Cell给滤掉,工具没有滤掉。

3、对于get_cells得到的结果,应该用foreach_in_collection去循环而非foreach。

4、对于工具native的命令,ChatGPT可能会用错,get_attr $cell ref_name才是正确的用法

5、在用lsort对ref list按照个数排序时,它没有指定-stride和-index

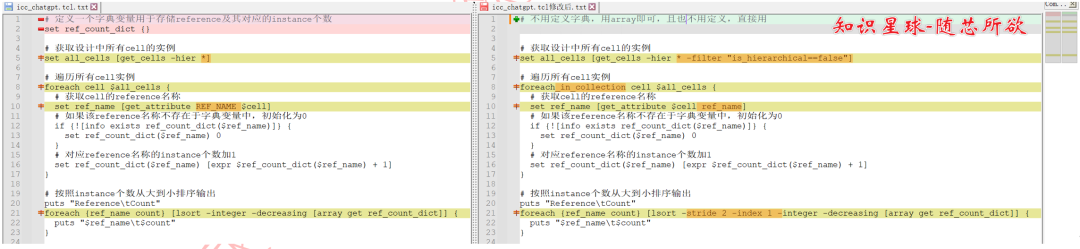

下面是ChatGPT给出的tcl脚本和我修改后的版本的对比:

下面是我修改后的脚本:

# 不用定义字典,用array即可,且也不用定义,直接用

# 获取设计中所有cell的实例

set all_cells [get_cells -hier * -filter "is_hierarchical==false"]

# 遍历所有cell实例

foreach_in_collection cell $all_cells {

# 获取cell的reference名称

set ref_name [get_attribute $cell ref_name]

# 如果该reference名称不存在于字典变量中,初始化为0

if {![info exists ref_count_dict($ref_name)]} {

set ref_count_dict($ref_name) 0

}

# 对应reference名称的instance个数加1

set ref_count_dict($ref_name) [expr $ref_count_dict($ref_name) + 1]

}

# 按照instance个数从大到小排序输出

puts "Reference Count"

foreach {ref_name count} [lsort -stride 2 -index 1 -integer -decreasing [array get ref_count_dict]] {

puts "$ref_name $count"

}

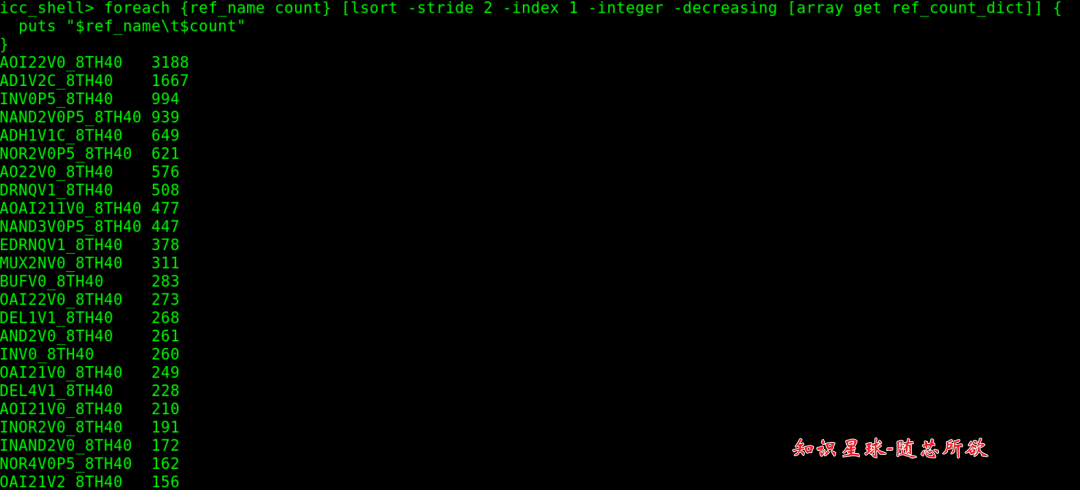

我修改之后的脚本的执行结果:

4、总结与展望

后边我又试了其他几个脚本编程的Case,ChatGPT给出的结果当然会有各种各样的问题,毕竟关于工具native的命令ChatGPT没有那么多Training的样本,但是它给出的结果还是有点出乎我的以外的,具有一定的参考性的,整体的思路还是比较正确的。

发散一下,再过几年,在用更多后端EDA工具的UG以及相关脚本对GPT训练的话,那么ChatGPT可以做的事情肯定会非常非常多,前途不可限量!!!!如果把ChatGPT嵌入到EDA工具中或者Solvnet/Cadence home上,那么对于Designer而言会有非常大的帮助。也许User只需要做一些简单的描述,工具就能很快给出参考的脚本或者对用户提出的问题给出参考的解决方案。

审核编辑:刘清

-

EDA工具

+关注

关注

4文章

268浏览量

31981 -

Verilog语言

+关注

关注

0文章

113浏览量

8312 -

VHDL源码

+关注

关注

0文章

2浏览量

1201 -

ChatGPT

+关注

关注

29文章

1574浏览量

8144

原文标题:ChatGPT在后端设计中有什么应用?ChatGPT懂后端EDA工具么?

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【国产FPGA+OMAPL138开发板体验】(原创)6.FPGA连接ChatGPT 4

在FPGA设计中是否可以应用ChatGPT生成想要的程序呢

OpenAI 深夜抛出王炸 “ChatGPT- 4o”, “她” 来了

科技大厂竞逐AIGC,中国的ChatGPT在哪?

TIA电路在后端加滤波器的时候看到方波变形的情况怎么解决?

前后端协同的时钟树设计方法

后端系统,后端系统是什么意思

数字后端基本概念介绍

virtIO中有两种方式控制前后端的notify

学后端的学前端有必要吗?

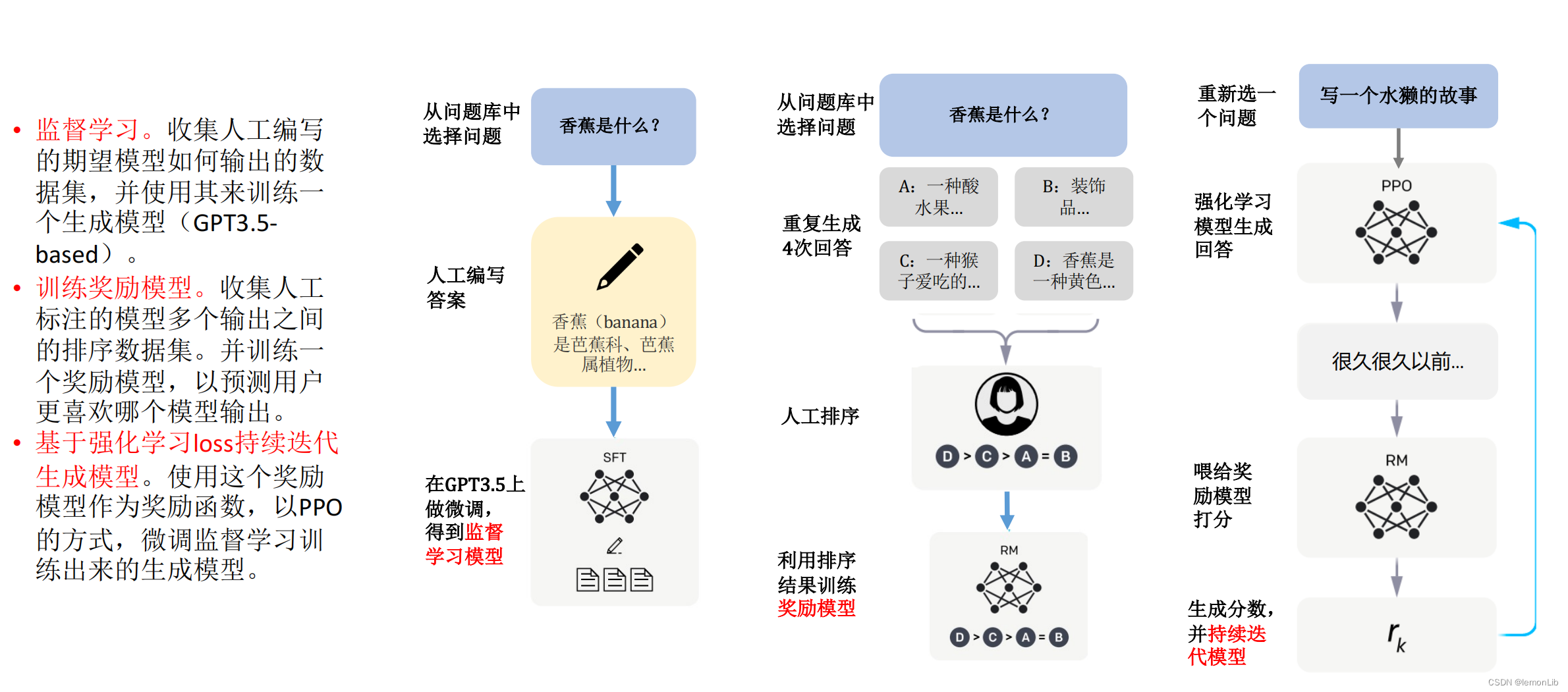

ChatGPT原理 ChatGPT模型训练 chatgpt注册流程相关简介

ChatGPT在后端设计中有什么应用?

ChatGPT在后端设计中有什么应用?

评论