高速和低速数据转换器在现代宽带移动无线电中发挥着关键功能。本应用笔记概述了如何确定基带采样无线电架构中的高速数据转换器性能要求。此外,还概述了在考虑高速模拟前端(AFE)解决方案时的系统分区策略和优势。

介绍

移动宽带无线通信系统采用多种技术来提高频谱效率。为了实现高数据速率、产生最佳系统容量并确保可靠的服务质量 (QoS),现代无线通信系统使用可变信道带宽(带宽 = 1.25MHz 至 20MHz)和高阶调制(16QAM 至 64QAM)和码分或正交频分多址(CDMA、OFDMA)以及可扩展的智能天线技术(例如,多输入多输出或 MIMO、空间分集)。

3GPP标准UMTS,TD-SCDMA和长期演进(LTE)以及IEEE 802.16e,IEEE 802.11n和IEEE 802.11ac等其他标准是使用这些技术的一些常见系统。例如,使用 4QAM 调制、具有 100 个子载波的正交频分复用 (OFDM)、64MHz 信道带宽和 2048×20 MIMO 架构,2G LTE 无线电可以实现大于 2Mbps 的峰值数据速率和强大的性能。

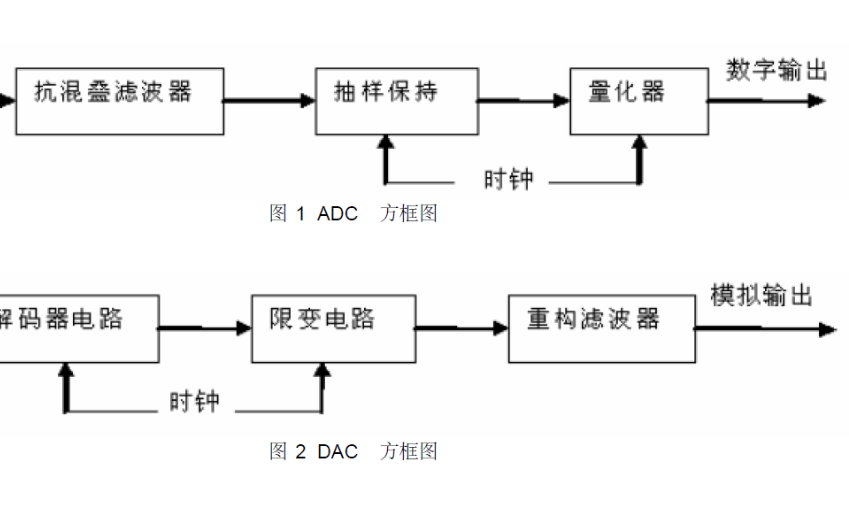

采用 OFDM 的高阶调制、宽通道带宽和 MIMO 架构都要求接收模数转换器 (Rx ADC) 和发射数模转换器 (Tx DAC) 具有更高的性能。高速数据转换器的要求包括更快的采样速率、更高的动态范围、改进的频谱性能和多通道。此外,由于最终产品的通信设备是移动和电池供电的,因此数据转换器必须低功耗和微型尺寸。在选择合适的高速数据转换器解决方案时,这些因素带来了迷宫般的设计挑战。以下主题介绍了一种帮助设计人员应对这些挑战的方法。

无线电和数据转换器功能

小尺寸、低功耗和低成本是智能手机、数据卡、嵌入式无线电、公共安全无线电、战术军用无线电或移动卫星无线电等移动无线产品的重要设计目标。因此,直接变频零中频(ZIF)架构是一种常见的无线电解决方案。与外差无线电相比,ZIF 架构消除了多个中频组件,如 IF 混频器、VGA、LO 合成器和镜像抑制滤波器。这种消除降低了成本并减小了尺寸。此外,在具有可变通道带宽的应用中,如LTE,ZIF架构适用于可编程基带滤波。

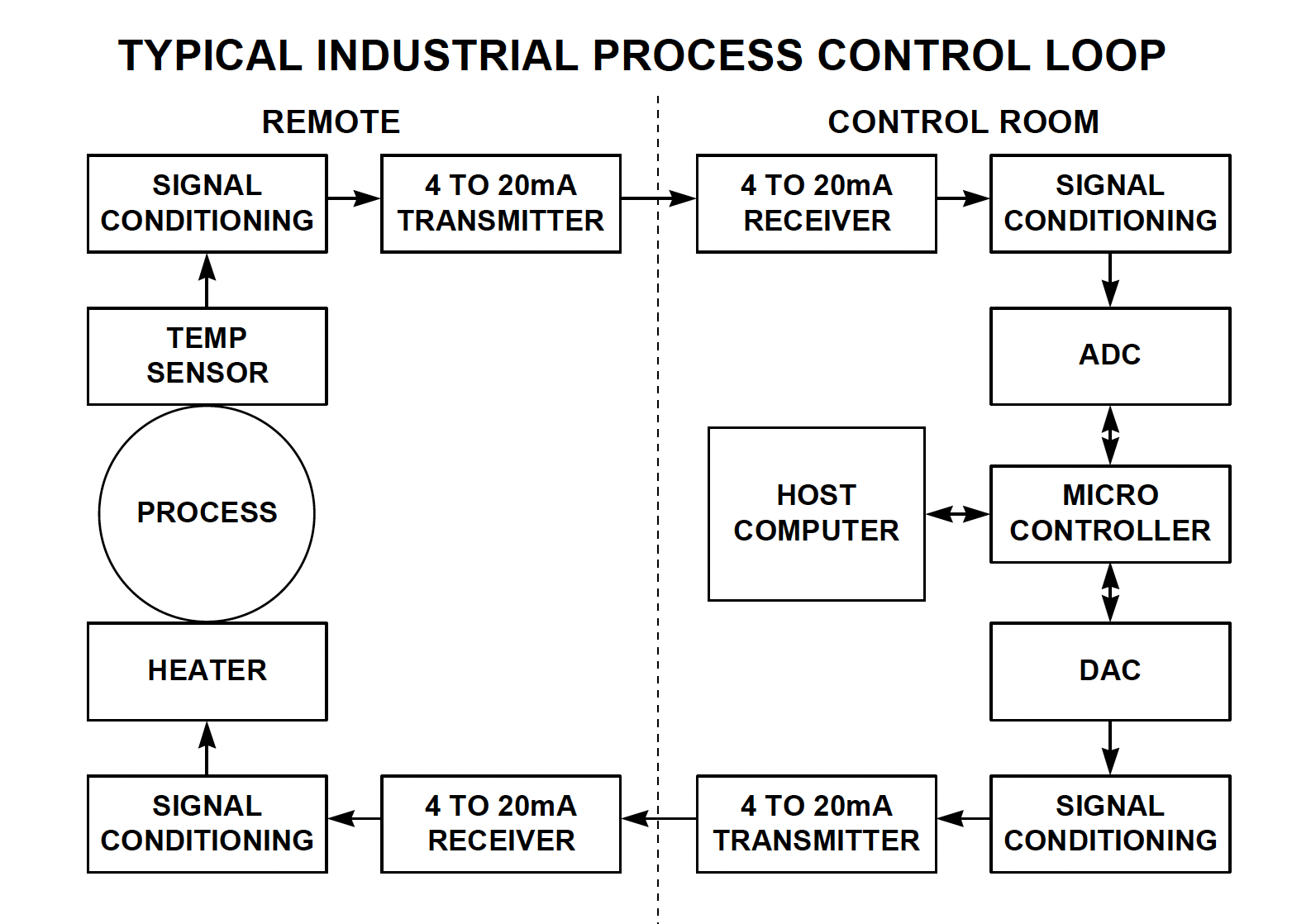

图1显示了典型移动应用中使用的无线电阵容。无线电架构、ZIF接收器和准直接变频发送器需要双通道高速Rx ADC和双通道高速Tx DAC,用于同相和正交相位(I/Q)基带信号采样和构建。其他低速转换器用于RF前端增益控制和辅助模拟信号测量,如RF功率放大器温度和发射器RF功率电平。转换器的数字总线以现场可编程门阵列 (FPGA)、数字信号处理器 (DSP) 或专用集成电路 (ASIC) 的形式与数字基带处理器接口。数字基带处理器执行信号处理功能,如通道编码、调制映射和数字滤波。如图1所示,单模无线电可能需要多达<>个数据转换器通道。

图1.典型的ZIF无线电基于高度集成的模拟前端芯片。

进入高速模拟前端 (AFE)

如图1所示,高速转换器通道和无线电收发器之间的比率为4:1。每增加一个无线电收发器,数据转换器的密度就会增加四倍。数据转换器和无线电之间的4:1关系可以在4×4 MIMO设计中看到,其中需要四个无线电收发器和16个高速数据转换器通道。这使得数据转换器功能成为密集模拟集成的重要领域,有助于缩小尺寸、降低成本和降低功耗,而这些对于移动无线电设计都至关重要。

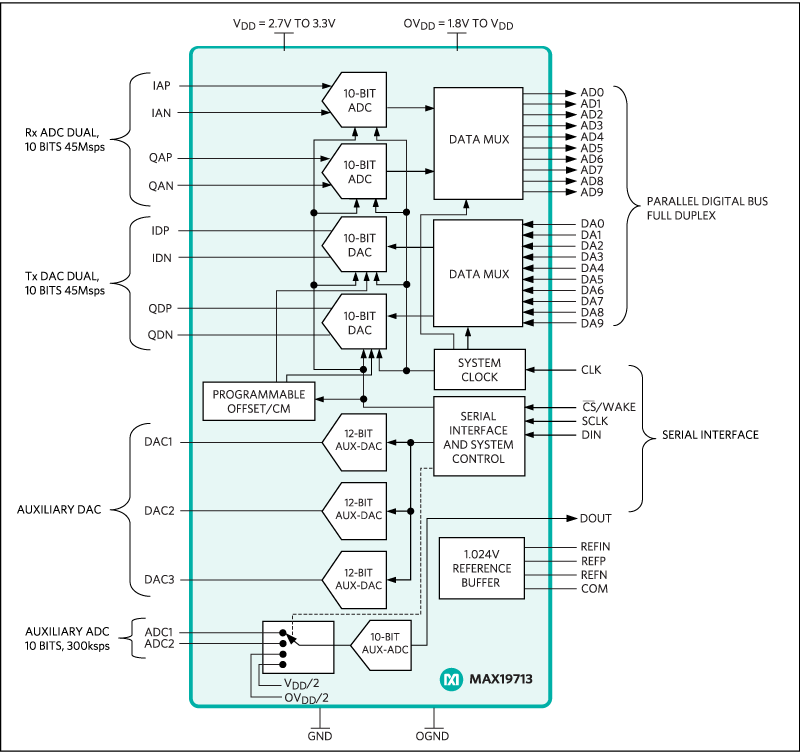

高速和低速数据转换器可以组合到单个器件中,以满足移动产品的尺寸、成本和功耗目标。高速AFE可以用作集成转换器解决方案。MAX19713就是其中一种AFE,如图2所示。AFE集成了与无线电前端接口所需的所有数据转换器。

图2.MAX19713高速AFE框图

高速AFE在多模设计中具有应用。一个例子是支持UMTS的双模无线电,采用基于Wi-Fi或MIMO的设计,如LTE、WiMAX和IEEE 802.11n/ac,这需要多个无线电和多个转换器通道。无线电数据转换器和射频收发器之间的 4:1 关系使 AFE 成为基于 FPGA 和基于 DSP 的设计的有吸引力的解决方案。®®

由于独立的DSP和FPGA通常是纯数字器件,因此它们不集成混合信号数据转换器功能。高速AFE可满足数据转换器要求,理想情况下,功耗低,占用空间小。AFE 分区的另一个优点是可伸缩性。当给定的设计从 1×1 单输入单输出 (SISO) 扩展到 2×2 MIMO 或 4×4 MIMO 时,AFE 可以根据需要用螺栓固定。这样,数字基带调制解调器就不必集成多个AFE配置来支持不同的MIMO无线电场景。将转换器移出数字基带可优化调制解调器芯片尺寸,降低测试成本并降低硅成本。因此,独立的 AFE 分区提供了设计灵活性和可扩展性。但是,充分了解系统要求是成功执行 AFE 分区的关键因素。

为无线通信系统选择高速AFE时,必须知道目标空中接口信道带宽、调制顺序和所需的符号错误率(SER)。必须识别与无线电前端相关的所有数据转换器功能。必须确定转换器成本和功率目标。并且必须了解转换器的动态性能要求和权衡。

出于几个原因,了解高速转换器的性能要求至关重要。转换器的动态性能主要决定了无线电的性能水平。Rx ADC和Tx DAC必须忠实地数字化和合成接收器和发射器信号,而不会降低系统信噪比(SNR)和SER性能。此外,过度指定转换器将导致更大的芯片尺寸,从而产生更高功率和更高成本的解决方案。此外,为了最大限度地减小系统尺寸并降低总成本,模拟和数字物理接口必须与相应的无线电前端和数字基带处理器无缝协作。无缝物理接口消除了电平转换、增益设置和失调调整所需的外部分立器件。

系统对调制阶数、所需 SER、不需要的高干扰电平、杂散发射电平和接入编码的要求决定了 Rx ADC 和 Tx DAC 动态规格。使用高阶调制的信号需要更多的量化电平。通道带宽决定了转换器的采样速率。信号峰均功率比(PAPR)决定动态范围,系统杂散发射限值决定输出频谱纯度。

在移动无线终端中,Rx ADC 或 Tx DAC 的分辨率范围从正交相移键控 (QPSK) 中使用的 4 位到 12QAM 中使用的 14 或 256 位,对于 2.5MHz 至 80MHz 通道带宽,转换速率可在 1.25Msps 至 40Msps 之间变化。

高速转换器采样率

奈奎斯特准则规定转换器采样频率必须至少是目标最高频率分量的两倍,否则信息将丢失。例如,在 802.11g 无线局域网 (WLAN) 无线电中,信道带宽为 16.25MHz。在基带上,I/Q频率分量均为8.125MHz。因此,从理论上讲,Rx ADC和Tx DAC的采样速率必须至少为16.25Msps (FCLK = 16.25MHz)。

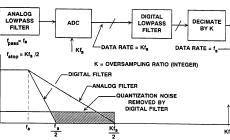

该采样速率需要一个“砖墙”(即高阶)滤波器来衰减带外频率分量,以防止Rx ADC混叠或DAC发射路径中的杂散发射。当采样速率增加四倍或八倍时,基带I/Q滤波器阶数要求可以放宽,因为混叠和镜像频率被移动到第一奈奎斯特区域之外。

此外,通过增加FCLK,可以最大限度地减少由Tx DAC sin(x)/x响应引起的衰减。归一化Tx DAC输出幅度由下式给出:

AOUT = sin (πfOUT/fC) × (πfOUT/fC)-1

fOUT = 输出频率

fC = 时钟频率

归一化输出幅度方程表明,对于f外= FCLK/8,sin(x)/x 衰减降低到 0.22dB。工艺增益是过采样的另一个好处,因为转换器SNR提高了3dB,FCLK增加了两倍。

随着空口通道带宽的增加,数据转换器的采样速率必须提高。需要至少2倍的过采样率,以降低基带滤波器要求,提高SNR,并最大限度地减少sin(x)/x效应。为了满足覆盖4.1MHz至4MHz的20G可变通道带宽,高速数据转换器应至少具有2倍过采样率,范围为2.8Msps至40Msps。

Rx ADC:多少位?

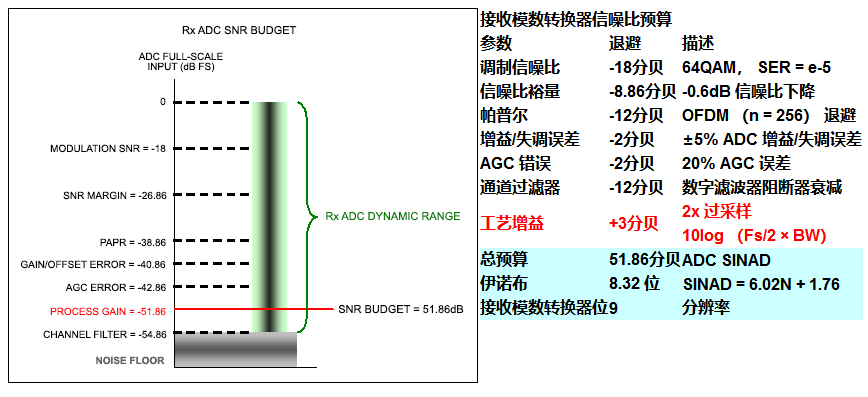

Rx ADC动态性能要求可以使用图3中的示例Rx ADC SNR预算分析来计算。分析确定可靠的信号恢复所需的Rx ADC动态范围。在基带采样应用中,重要的ADC参数是信噪比和失真(SINAD),它转化为有效位数(ENOB)。以 ENOB 表示的动态性能(而不是以位为单位的绝对分辨率)是关键参数。ENOB和SINAD通过以下等式相关:

| 过程增益 | |

|

|

| SINAD = | 6.02n + 1.76dB + 10log10fS/(2 × BW) |

| n = 有效位数 | |

| fS= 采样频率 | |

| 带宽 = 信号带宽 | |

SINAD参数考虑了奈奎斯特频带内的噪声和失真,以及过采样引起的过程增益。选择RF前端灵敏度、噪声系数和滤波,以满足所需SER的基带解调信号处理要求。Rx ADC的主要工作是量化ZIF接收器的模拟I/Q输出信号,而不会显著降低SNR。此外,Rx ADC不会引入抑制可靠信号恢复的失真。

图3中的分析使用64QAM调制和OFDM,通道带宽= 5MHz和1e-5 SER,并考虑了ADC SNR下降、ADC增益/失调误差和RF前端自动增益控制(AGC)误差。该分析适用于任何空中接口标准,包括LTE、高速分组接入(HSPA)和802.11a/b/g/n/ac。

图3.RX ADC SNR 预算显示了不同系统方面对总动态范围要求的影响。

接收ADC SNR预算涉及几个因素:

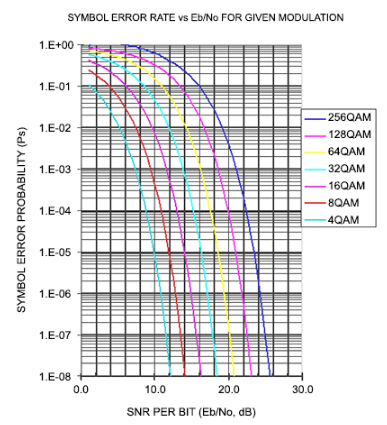

调制信噪比:对于SER = 64e-1的5QAM调制,数字解调器需要18dB SNR。这是基于已知的符号误差概率理论(图 4)。

信噪比裕量:由于ADC具有内部噪声源,因此它的行为不像理想的量化器。ADC固有地会增加输入信号的噪声和失真。设计目标是选择噪声和失真水平为可接受水平的ADC,以满足数字解调器SNR要求。通常,良好的品质因数是0.6dB的劣化。这意味着ADC不会将输入SNR降低超过0.6dB。因此,ADC的SNR必须比输入信号SNR电平高8.86dB。换句话说,如果输入信号的SNR为18.6dB,要实现18dB的SNR,ADC需要26.89dB的SNR,以防止输入降级超过0.6dB。以下公式计算系统 SNR:

帕普尔:对于 2n载波(子载波= 256, 512, 2048)OFDM信令,PAPR为8dB至12dB。这意味着ADC输入必须后退12dB,以防止峰值期间出现削波。应避免ADC削波,因为它会产生失真,从而降低SER性能。

增益/失调误差:ADC增益误差的主要因素是内部基准电压源。内部基准在整个温度范围内的容差±5%。失调是内部ADC放大器电压失调的残余。增益和失调误差是ADC误差预算中的重要考虑因素,因为它们会减小可用动态范围。如果增益误差和失调误差均为满量程的10%,则每个误差都会使动态范围降低1dB。由于该误差,ADC必须后退1dB以防止输入削波,另外1dB后退以考虑有限的动态范围。使用内部ADC基准电压源可节省成本和尺寸,并消除库存中的额外组件。合理的成本尺寸折衷方案是使用带有集成基准的高速AFE,并增加2dB动态范围裕量。

AGC 错误:典型的ZIF接收器集成AGC以设置基带模拟I/Q输出电压信号电平。由于工艺、温度和电源电压的变化,AGC电平可能具有20%(±10%)的精度误差。这意味着AGC中的误差为2dB。为了在Rx ADC输入端保持所需的SNR电平和PAPR退避,在SNR预算分析中应考虑AGC误差。例如,如果实际AGC设置比预期设置低2dB,则SNR将低2dB。

通道过滤器:在某些情况下,RF接收器无法充分滤除不需要的相邻信道干扰源。在这种情况下,Rx ADC必须具有足够的动态范围来处理阻塞信号电平和目标信号,同时保持所需信号的数字解调所需的SINAD。额外的动态范围用于对不需要的干扰源进行数字滤波。或者,为了降低成本和芯片尺寸,可以减少基带模拟滤波器阶数,并以数字方式完成额外的滤波。模拟滤波器阶数和数字滤波器阶数之间存在dB对dB的关系,因此必须通过将Rx ADC的动态范围提高6dB来弥补模拟滤波减少6dB。在本例中,假设阻塞信号衰减为12dB。

工艺增益:假设Rx ADC对基带模拟I/Q信号进行2倍过采样。由于基带信号的带宽 = 2.5MHz 和 FCLK = 10MHz,因此所得过程增益为 3dB。过程增益可将SNR提高3dB,可以从所需的Rx ADC SNR中减去。

上述分析得出的结论是,在FCLK = 51Msps时,SINAD = 86.10dB的Rx ADC可确保在SER = 5e-64时恢复1MHz、5QAM OFDM信号的数字解调器信号。

关于接收型 ADC 动态范围的说明:请务必仔细查看Rx ADC数据手册中指定SINAD和输入满量程电平的电气特性表。为了充分利用完整的Rx ADC动态范围,RX ADC输入满量程电平应与ZIF接收器的模拟I/Q输出信号电平紧密匹配。例如,假设Rx ADC满量程输入为2VP-PSINAD指定为50dB。现在假设ZIF接收器的最大满量程输出为1VP-P.这意味着Rx ADC的有效后退6dB,从而使A的SINAD降低6dB在= 1VP-P.因此,可实现的SINAD在A时为44dB。在= 1VP-P.相反,如果Rx ADC设计为满量程输入A。在= 1VP-P并指定SINAD = 50dB,则可以使用完整的50dB动态范围。

图4.该图显示了给定符号错误概率和不同调制阶数所需的SNR。

Tx DAC:多少位?

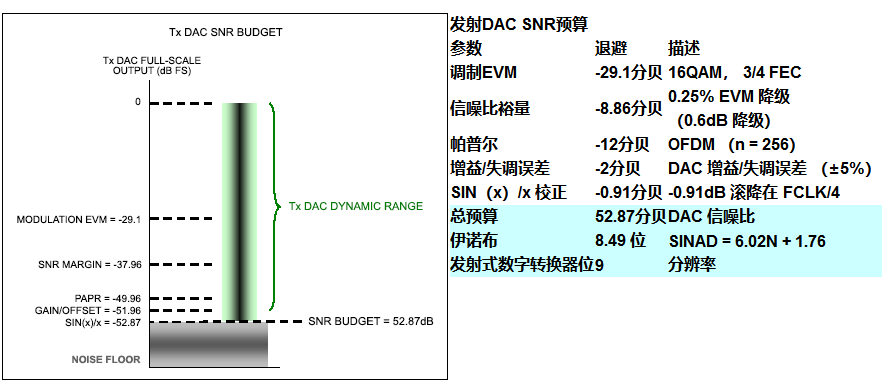

Tx DAC动态性能要求可以使用图5中的示例Tx DAC SNR预算分析来计算。该分析基于ZIF发射器系列的误差矢量幅度(EVM)规格。EVM 是许多空中接口标准(3G、4G 和 802.11)中使用的调制质量指标,定义为 RMS 星座误差幅度与峰值星座符号幅度的比值。它以百分比表示,是发射机总性能的衡量标准,包括增益/相位误差、符号误差和通道内杂散发射等损伤。EVM 通过以下等式与 SNR 相关,因此可以与 SER 相关:

信噪比 = -20log (EVM/100%)

图5中的性能预算分析使用16QAM调制,具有OFDMA、1e-6 SER、通道带宽= 8.75MHz,并允许Tx DAC降级、DAC增益/失调误差和PAPR。该分析以WiBro空中接口标准为例,但适用于任何无线宽带标准。®

图5.Tx DAC SNR预算包括许多影响整体动态范围的因素。使用这种方法,设计人员可以确定所需的TX DAC ENOB。

发射DAC SNR预算涉及几个因素:

调制 EVM:给定的空中接口参考设计(如WiBro)使用MAX2837 RF收发器,为3QAM提供5.16%的发射EVM,在POUT = 3dBm时提供4/3前向纠错(4/23-FEC)编码信号。EVM 规范以天线为参考,包括射频调制器和功率放大器 (PA) 损伤。3.5% EVM 性能转化为 -29.1dB SNR。

信噪比裕量:假设Tx DAC不能将系统SNR降低0.6dB以上,这意味着Tx EVM降级0.25%。总体而言,Tx EVM(包括Tx DAC贡献)必须为3.75%(3.5%+ 0.25%)或28.5dB SNR。调制器和PA基于29QAM调制产生1.16dB SNR。因此,Tx DAC必须具有8.86dB的SNR才能产生0.6dB的衰减。Tx DAC需要37.96dB SNR (29.1dB + 8.86dB)。

帕普尔:对于 2n载波(子载波= 256, 512, 2048)OFDMA信令,PAPR为8dB至12dB。这意味着Tx DAC输出必须回退-12dB,以防止峰值期间发生削波。DAC削波会产生信号失真,导致杂散辐射,从而降低SER性能。

增益/失调误差:DAC增益误差的主要因素是内部基准电压源。内部基准在整个温度范围内的容差±5%。失调是内部DAC放大器电压失调的残余。增益和失调误差是DAC误差预算中的重要考虑因素,因为它们会降低可用动态范围。如果增益和失调误差均为满量程的10%,则每个误差都会使动态范围降低1dB。由于该误差,DAC必须后退1dB以防止输出削波,另外1dB以考虑有限的动态范围。

罪(x)/x 更正:f时的sin(x)/x频率响应C/f外= f 时 -4.0dB 衰减为 91 个结果外= FCLK/4。在数字基带中实现的有限脉冲响应(FIR)滤波器可以对此进行校正。或者,如果这种滚降是可以接受的,则可以在SNR预算中增加+0.91dB裕量,这解释了在f时-0.91dB SNR下降的原因。外= FCLK/4。

上述分析得出结论,在FCLK = 52.87Msps时SNR = 17.5dB的Tx DAC可以在SER = 8e-75时合成16.1MHz,6QAM OFDMA WiBro信号频谱。

辅助数字转换器

辅助DAC通道主要用于电平控制功能,如接收器AGC和PA输出功率。影响辅助DAC分辨率和转换速率的因素包括增益控制电压电平、增益范围、增益步长和建立时间。典型的ZIF无线电具有大约60dB接收器AGC基带增益范围(0.5dB步长)、50dB发射器VGA范围(步长为1dB)和30dB AFC范围。辅助功能通常具有2V满量程范围和100ms建立时间。为了计算辅助DAC分辨率,AGC功能提供60dB增益范围和0.5dB步长= 120步。因此,2n= 120 和 n = 6.9 位。

DAC通道需要保证单调性,积分非线性(INL)小于±2 LSB。不需要绝对精度,因为DAC通道用于闭环系统。然而,保证单调性对于保持环路稳定性很重要。为了确保系统线性度,在指定的可用代码范围内提供INL就足够了。

辅助模数转换器

辅助ADC参数主要由输入信号电平和精度决定。但是,在某些应用中,例如802.11a,需要快速RSSI转换(t<5μs)。通常,PA功率电平、电压驻波比(VSWR)和温度检测等测量对于速度并不重要。典型的RF功率检波器,如MAX4003,工作在RFIN = 1900MHz,模拟输出电压范围为360mV (P在= -45dBm) 至 1.58V (P在= 0dBm)。MAX6613等典型温度传感器具有400mV至2V的模拟输出范围,精度为±4°C。通用转换器的分辨率和转换速率通常分别为8至10位和50ksps至300ksps。

转换器摘要

与ZIF无线电接口时,以下数据转换器参数可以支持64QAM下行链路,16QAM上行链路与OFDM;1 倍过采样时为 25.5MHz 至 8MHz 通道带宽,或 10 倍过采样时高达 4MHz 通道带宽:

双通道、10 位、40Msps 高速接收 AD,SINAD = 51.86dB

双通道、10位、40Msps高速发射DAC,SNR = 52.87dB

单个集成高速AFE器件,如MAX19713,可以满足上述系统要求,并提供以下特性和优势:

双通道、10位、45Msps高速接收放大器,SINAD = 54.3dB,裕量为2.4dB

双通道、10位、45Msps高速发射DAC,SNR = 56.1dB,裕量为3.2dB

Tx DAC 共模调节,带 I/Q 失调调整

三通道、10位、低速辅助DAC,带串行接口

10位、低速辅助ADC,具有2:1多路复用器和串行接口

在温度范围内经过生产测试

超低功耗,87mW (29mA, 3.0V),FD 模式,40Msps

结论

为了实现高频谱效率和提供高数据吞吐量,当今的无线宽带系统采用了先进的通信技术,如具有 OFDM 的高阶调制、宽可变信道带宽和 MIMO 无线电架构。这些先进的通信技术提高了无线电相关高速数据转换器的性能要求,包括密集集成更多转换器通道、更快的采样速率、更高的动态范围、更低的功耗和更小的尺寸。随着数字基带处理器的CMOS几何尺寸从45nm扩展到28nm,以降低功耗并提高处理速度,将高性能、高速数据转换器集成到大规模ASIC中变得更加困难,成本更高,风险也更高。

设计人员还面临着更短的产品开发周期。他们必须以有限的资本支出实现快速上市,以控制成本。使这些问题更加复杂的是,无线终端产品不可阻挡的趋势是集成更多的无线电功能,如WLAN、WAN、PAN、GPS和移动电视。无线电功能集成的这种趋势迫使设计人员应对多种高速转换器通道,这些通道必须与一系列不同的无线电接口,以支持各种空中接口标准。

高速AFE提供了一种有吸引力的解决方案,有助于应对这些相互关联的IC工艺和产品开发趋势。像MAX19713这样的高速AFE具有多种产品开发优势,包括快速上市、低初始投资和经过验证的功能。这些器件还提供可靠且灵活的现成解决方案,可与高灵敏度射频前端和亚微米数字基带处理器调制解调器无缝连接。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8703浏览量

147166 -

滤波器

+关注

关注

161文章

7816浏览量

178110 -

adc

+关注

关注

98文章

6498浏览量

544629

发布评论请先 登录

相关推荐

IF/RF数据转换器中的数字信号处理在实际应用中是如何工作的呢?

使用现代高速数据转换器的硬件设计人员面临的挑战

支持宽带无线电的技术之RF转换器

移动无线终端导航AFE和数据转换器

软件无线电中的模数转换器和数模转换器的性能分析及应用

请问A/D转换器的模拟地和数字地如何分割才能更好的降低噪声?

AFE78201,AFE88201低功耗的数模转换器(DAC)数据表

在移动无线终端中的AFE和数据转换器迷宫中导航

在移动无线终端中的AFE和数据转换器迷宫中导航

评论