电子发烧友网报道(文/周凯扬)随着AI与HPC运算的盛行,如今为了将算力继续扩展下去,CPU和GPU都在朝着多核的方向发展下去,计算密度也在大幅提升。此外,数据中心也越来越多地开始转向异构工作负载,对基础架构、性能和可用性提出了又一轮的要求,也在加速存储产品的转型,催生了CXL这样的新技术,但仅仅只靠CXL,是无法打破我们所说的内存瓶颈的。

加速内部流量成为服务器性能的新关键

100GbE模块的出现后,在网络交换与传输性能如此发达的当下,远程存储已经成了越来越多企业的首选。但本地存储也在经历一轮性能的革命,NVMe、NVDIMM等技术演进进一步降低了存储的网络延迟,解决了一路走高的内部带宽需求。

那么服务器内部数据的移动要如何跟上呢?在复杂的服务器基础架构中,内部数据的交换往往由多个内存缓冲拷贝组成,比如内核到I/O、I/O到特定硬件,实现方式主要靠不同层级的软件栈,但软件到软件间的数据交换仍靠的是CPU。

当下的内存数据移动的软件标准为memcpu,虽然已经足够稳定,但也限制了应用的性能。比如为了提供上下文隔离而招致更大的软件开销。所以大家开始尝试DMA,这种用于卸载软件复制循环的策略。虽说这样做解放了CPU的部分负担,但这种方案与特定设备的接口绑定,只适合专门的特权软件和I/O用例,更别提前向兼容了,尤其是在公有云这种多人功用的虚拟环境中。

SDXI,新的数据加速器接口标准

这就引出了一系列痛点,比如既要从CPU执行周期中将I/O解放出来,又要保证架构的稳定性。提供虚拟机加速的同时,又能帮助开发者从已有软件栈中迁移到新的方案上,还要考虑到当下新的内存互联方案,比如CXL、Gen-Z等等。为了解决这些痛点,2020年起,SNIA(全球网络存储工业协会)成立了一个新的工作组并提出了SDXI(智能数据加速器接口)这一概念,为的就是提供一个可扩展、虚拟化且前向兼容的内存数据移动与加速接口规范。

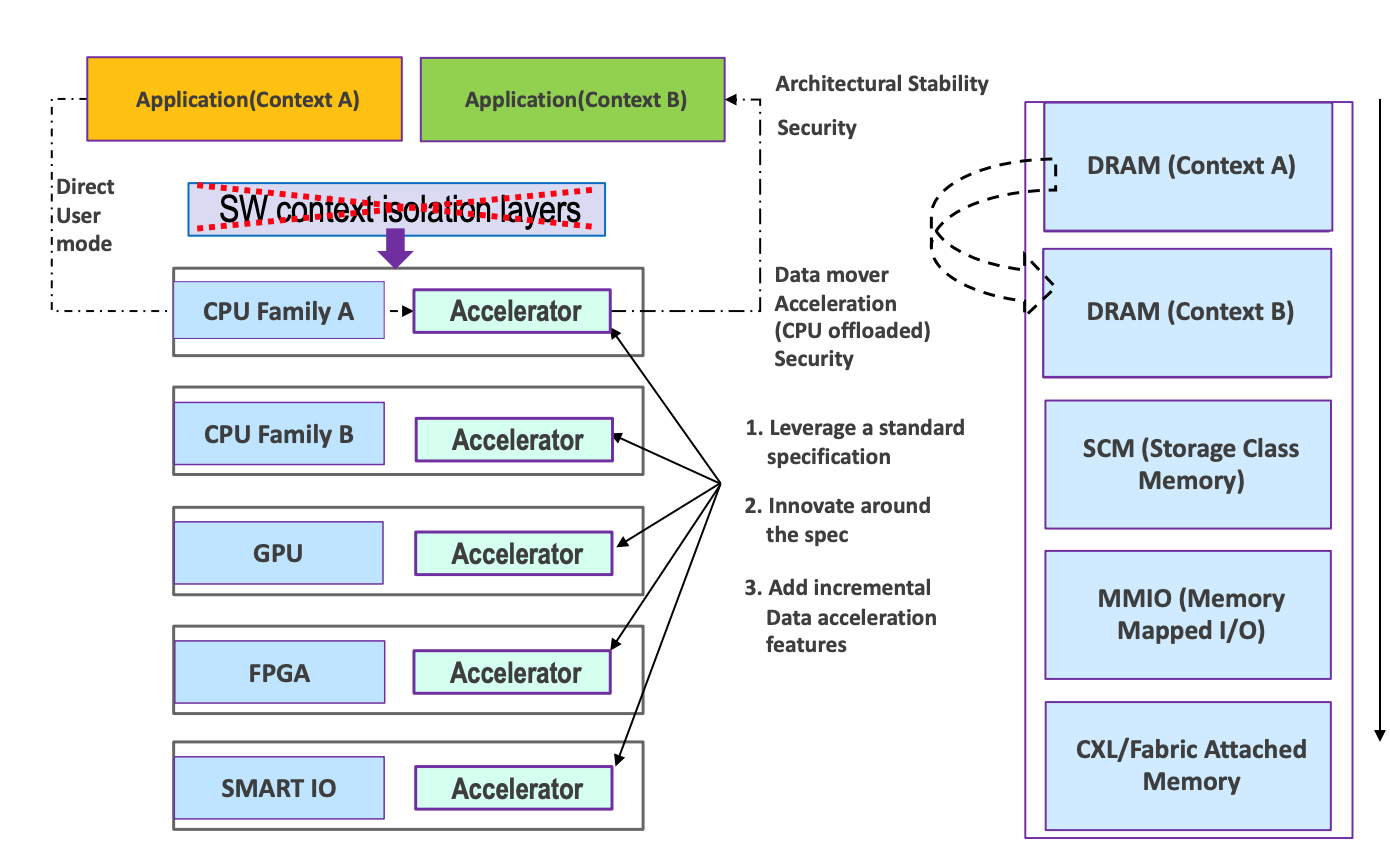

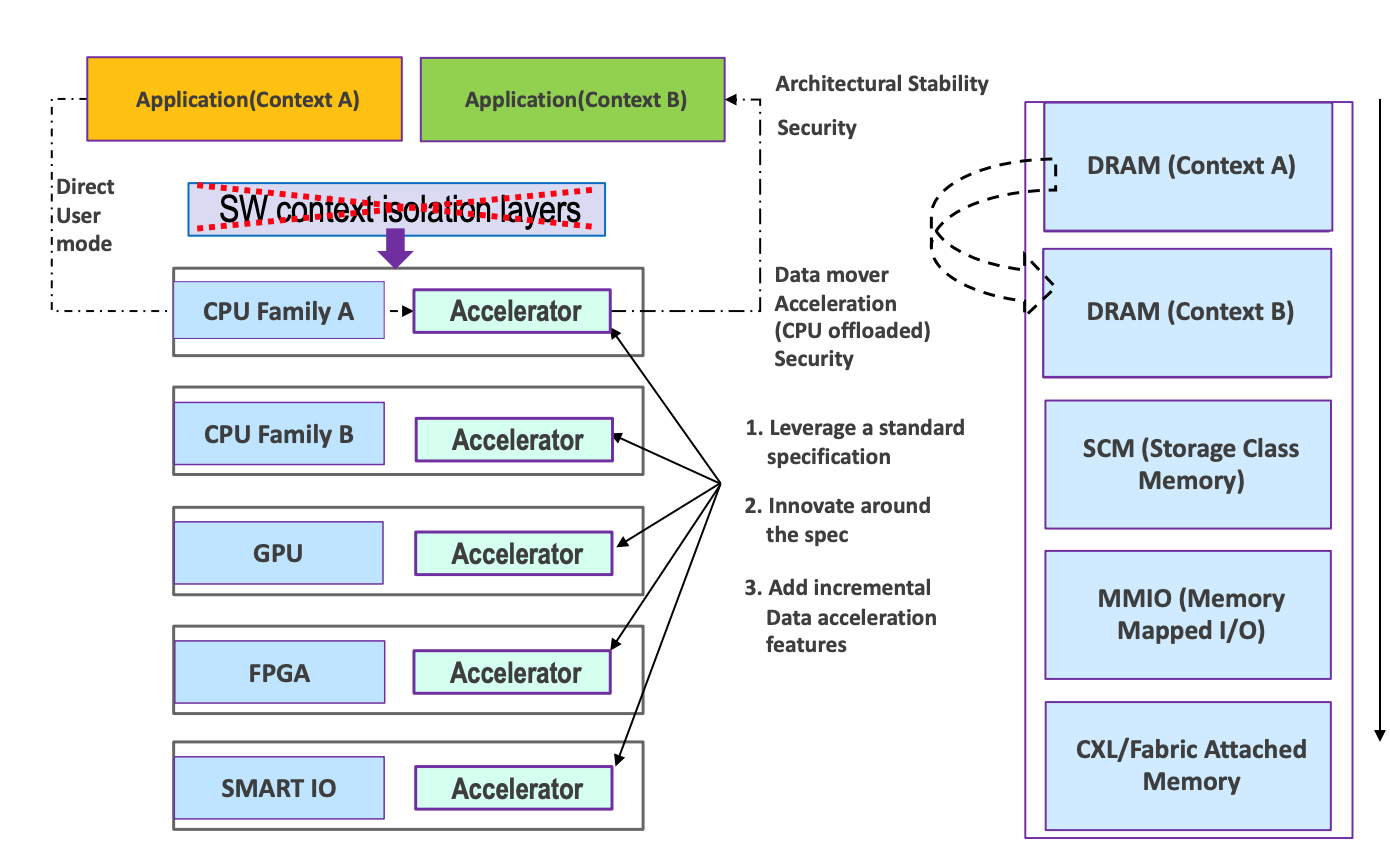

SDXI下的内存间数据移动 / SNIA

SDXI作为一个标准化方案,不仅要兼容DRAM、SCM、MMIO、CXL和Gen-Z这些不同的内存,也要为CPU、GPU、FPGA、智能I/O等提供标准的加速器接口。如此一来,SDXI可以在不同的地址空间实现数据移动,包括用户地址空间和不同的虚拟机等。而且一旦连接建立,数据移动再也不需要特权软件作为中介。从戴尔在PCIe 3.0 FPGA上的原型测试上来安,改用SDXI可以实现超过memcpy两倍以上的线性拷贝速度。

截至目前,不少内存厂商和服务器厂商都已经加入了对SDXI的贡献行列中来,比如AMD、Arm、戴尔、HPE、IBM,以及美光、三星、SK海力士等。他们也在考虑在1.0标准之后,继续从QoS、延迟、RAS上加以改进,在实现未来版本前向与后向兼容的同时,一起推动SDXI在CXL系统架构中的普及。

小结

在ARM、RISC-V纷纷入局数据中心,并推出百核、千核的CPU处理器后,更快的数据交换将成为一个必然的需求,未来的网络与存储技术也需要SDXI提供这样的扩展性。何况SDXI提供的不仅仅是加速,还是一个标准化接口,在满足数据移动性能的同时,支持软件爱你的重复利用和虚拟化。

加速内部流量成为服务器性能的新关键

100GbE模块的出现后,在网络交换与传输性能如此发达的当下,远程存储已经成了越来越多企业的首选。但本地存储也在经历一轮性能的革命,NVMe、NVDIMM等技术演进进一步降低了存储的网络延迟,解决了一路走高的内部带宽需求。

那么服务器内部数据的移动要如何跟上呢?在复杂的服务器基础架构中,内部数据的交换往往由多个内存缓冲拷贝组成,比如内核到I/O、I/O到特定硬件,实现方式主要靠不同层级的软件栈,但软件到软件间的数据交换仍靠的是CPU。

当下的内存数据移动的软件标准为memcpu,虽然已经足够稳定,但也限制了应用的性能。比如为了提供上下文隔离而招致更大的软件开销。所以大家开始尝试DMA,这种用于卸载软件复制循环的策略。虽说这样做解放了CPU的部分负担,但这种方案与特定设备的接口绑定,只适合专门的特权软件和I/O用例,更别提前向兼容了,尤其是在公有云这种多人功用的虚拟环境中。

SDXI,新的数据加速器接口标准

这就引出了一系列痛点,比如既要从CPU执行周期中将I/O解放出来,又要保证架构的稳定性。提供虚拟机加速的同时,又能帮助开发者从已有软件栈中迁移到新的方案上,还要考虑到当下新的内存互联方案,比如CXL、Gen-Z等等。为了解决这些痛点,2020年起,SNIA(全球网络存储工业协会)成立了一个新的工作组并提出了SDXI(智能数据加速器接口)这一概念,为的就是提供一个可扩展、虚拟化且前向兼容的内存数据移动与加速接口规范。

SDXI下的内存间数据移动 / SNIA

截至目前,不少内存厂商和服务器厂商都已经加入了对SDXI的贡献行列中来,比如AMD、Arm、戴尔、HPE、IBM,以及美光、三星、SK海力士等。他们也在考虑在1.0标准之后,继续从QoS、延迟、RAS上加以改进,在实现未来版本前向与后向兼容的同时,一起推动SDXI在CXL系统架构中的普及。

小结

在ARM、RISC-V纷纷入局数据中心,并推出百核、千核的CPU处理器后,更快的数据交换将成为一个必然的需求,未来的网络与存储技术也需要SDXI提供这样的扩展性。何况SDXI提供的不仅仅是加速,还是一个标准化接口,在满足数据移动性能的同时,支持软件爱你的重复利用和虚拟化。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

热点推荐

无线快充技术,国内首个统一标准发布

电子发烧友报道(文/李弯弯)近日,中国通信标准化协会与电信终端产业协会联合宣布,《移动终端融合快速充电 无线充电技术要求》团体标准正式发布,该标准由中国信通院联合国内主流终端与芯片企业

2026年了,为什么多环境DDL发布还不能只靠脚本和习惯?

数据库表结构发布进入新阶段,核心不是工具界面更好看,而是流程开始被平台真正接住。NineData 的多环境编排能力,正是数据库 DevOps 从“执行层自动化”走向“流程层自动化”的一个代表。

Aliro 1.0 全新统一标准发布 重塑智能门锁及门禁生态系统

加利福尼亚州戴维斯市——2026 年2 月26 日—— 连接标准联盟(联盟)今日正式发布Aliro 1.0 规范。作为一套全新通信协议与凭证标准,Aliro 将彻底改变用户在生活各类场景中与门禁设备

为什么原厂越来越需要一套自己的 Studio

外设怎么配

第一版工程如何快速跑起来

这些问题,已经很难只靠数据手册解决。

二、手册 + 示例工程,逐渐不够用了

大多数原厂其实已经做了很

发表于 02-05 09:37

澜起科技发布PCIe 6.x/CXL 3.x AEC解决方案

澜起科技今日宣布,率先在国内推出基于PCIe 6.x/CXL 3.x标准的高性能有源电缆(AEC,Active Electrical Cable)解决方案。该方案面向数据中心从单机架向多机架复杂架构

Penguin Solutions SMART Modular CXL NV-CMM E3.S 2T 内存模块通过 CXL 兼容性认证

失性内存模块已成功通过 CXL® 兼容性测试。此项里程碑不仅代表产品符合行业标准,也进一步确立 Penguin Solutions 在 CXL

借助CXL和压缩技术实现高效数据传输

AI、科学计算、海量内存处理……这些硬核工作负载正在不断挑战系统极限。而 FPGA 异军突起,成为了实现高效数据传输的“关键推手”。想知道怎么在不改变整体架构的前提下,让带宽和能效实现“双飞跃”?答案就藏在压缩 IP 与基于 CXL(Compute Express Lin

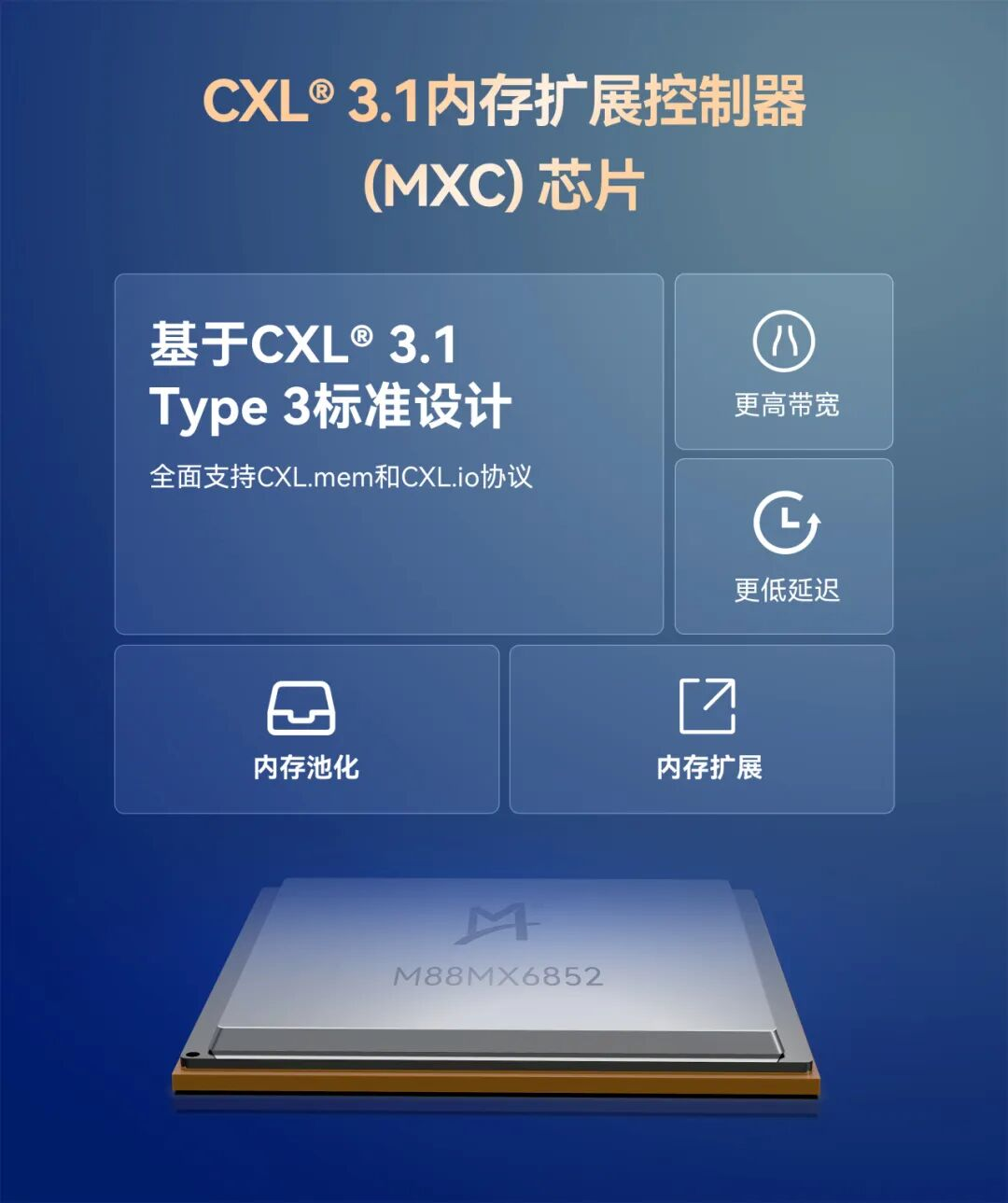

64GT/s+8000MT/s:澜起CXL 3.1芯片破解数据中心内存瓶颈

。 M88MX6852:性能卓越,满足多元需求 M88MX6852芯片全面支持CXL.mem和CXL.io协议,其核心使命是为下一代数据中心服务器打造更高带宽、更低延迟的内存扩展和池化解决方案。在

澜起科技推出CXL® 3.1内存扩展控制器,助力下一代数据中心基础设施性能升级

下一代数据中心服务器提供更高带宽、更低延迟的内存扩展和池化解决方案。 澜起科技CXL 3.1内存扩展控制器采用PCIe® 6.2物理层接口,支持最高64 GT/s的传输速率(x8通道),并具备多速率

只靠CXL还不够,数据移动也需要统一标准

只靠CXL还不够,数据移动也需要统一标准

评论