一.Vt 简介

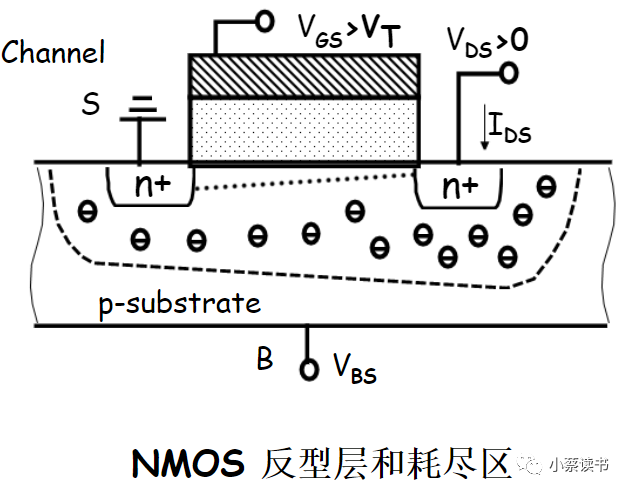

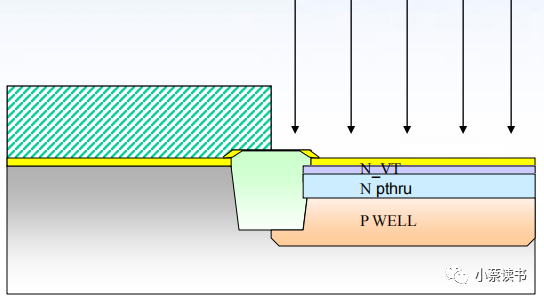

Vt指的是MOS管的阈值电压(threshold voltage)。具体定义(以下图NMOS为例):当栅源电压(Vgs)由0逐渐增大,直到MOS管沟道形成反型层(图中的三角形)所需要的电压为阈值电压。

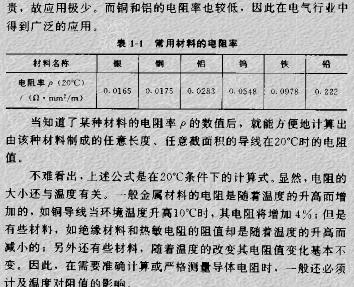

二.阈值电压和哪些因素有关系

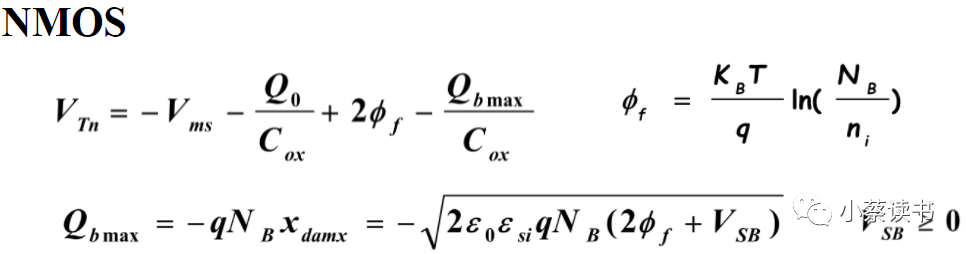

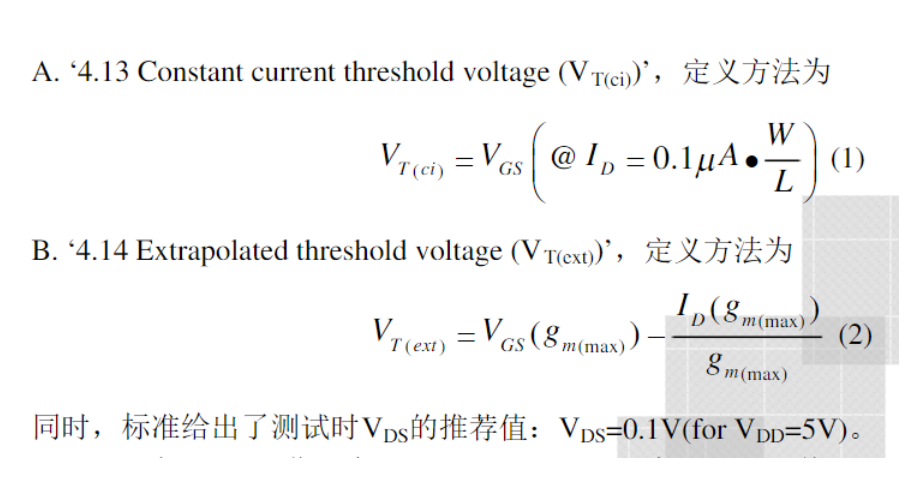

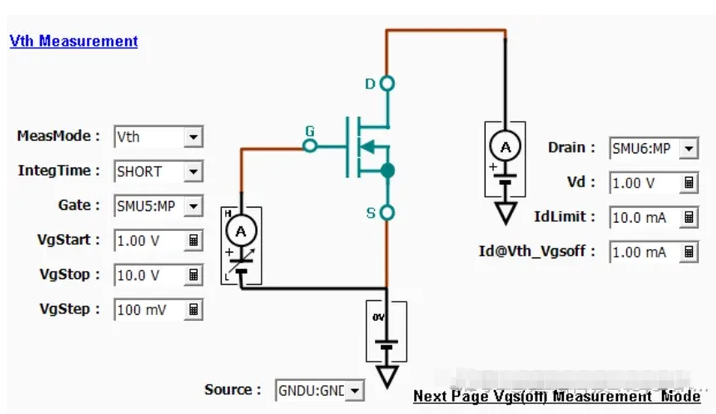

首先看阈值电压的公式(以NMOS为例),具体推导过程不再介绍。

相关因素

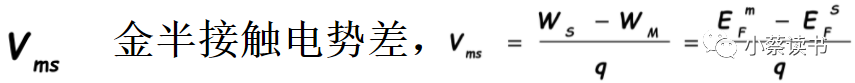

1.金半接触电势差:和栅极金属方块电阻以及衬底掺杂浓度有关。

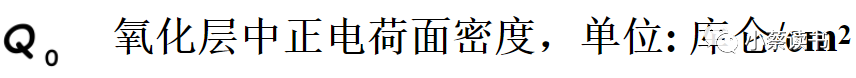

2.氧化层中的电荷密度

3.半导体费米势

4.栅氧化层厚度

5.衬底掺杂浓度

6.源衬电压

三.不同Vt cell工艺是怎么实现的?

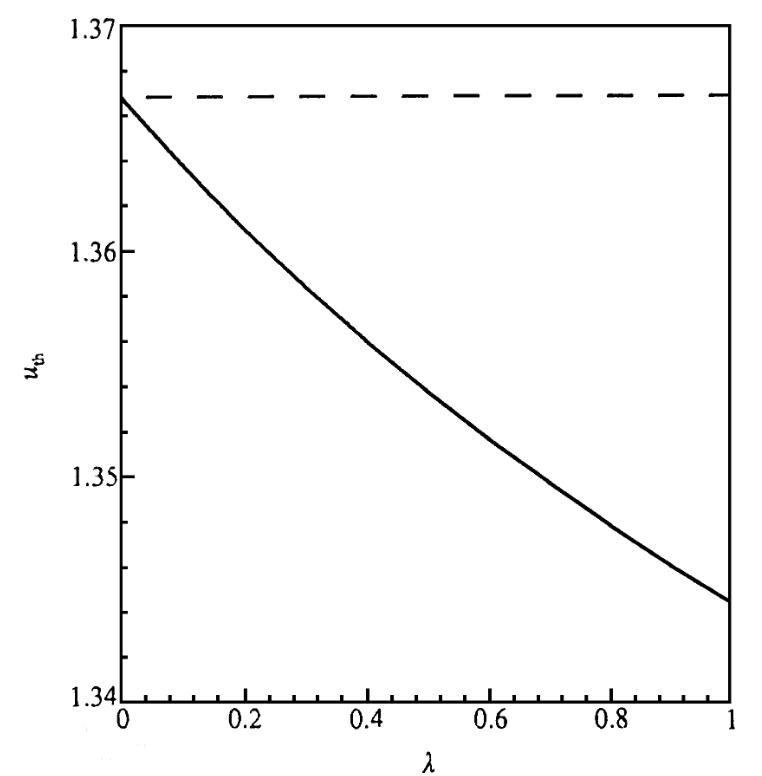

上面提到了这么多影响Vt的因素,那么实际中不同的Vt cell是通过控制哪个变量来实现的呢?衬底掺杂浓度。现在有的先进工艺有7、8种Vt cell,看到比较老的工艺资料(如下图)介绍是通过控制衬底掺杂浓度来控制阈值电压,可能先进工艺会用到更多手段。简单的理解就是:沟通掺杂浓度越高(以NMOS为例),越容易形成反型层,所以阈值电压越小;或者可以反的理解为假如不做沟道掺杂,阈值电压应该是最大的。

掺杂工艺需要控制的三个变量:气体类型(带B或者P)、注入剂量、注入能量。

四.功耗与性能(时序)的tradeoff

foundary提供这么多种Vt cell,就是为了让用户根据不同设计的电路做出最好的功耗与性能的tradeoff。首先要说的是:Vt越大(比如HVT),cell功耗越小,延时越大;相应的Vt越小(比如ULVT),cell功耗越大,延时越小。所以对于一个design来说,性能要求比较高的模块,可能需要ULVT cell多一点,比如CPU;对于性能要求低一些的cell,不需要那么多ULVT cell就可以省功耗。当然cell的延时不仅和Vt类型有关,也和沟道宽长比有关(比如宽度7T,9T,长度C30,C35)。

1.时序与Vt

还记得刚入行的时候,跑完place,时序有些违例,然后就想知道是继续往下跑还是调整floorplan。找young master过来看了一下,打开时序报告,看了下最大违例路径launch上的cell类型,很多是LVT或者SVT,说可以往下跑,还可以换ULVT以满足时序。这就是使用ULVT来减小延时满足setup的案例。

2.功耗与Vt

在综合、PnR、STA阶段都可以采取一些措施减小功耗,看了下原理:在时序路径setup满足且有余量的情况下,把这些路径下的cell 换成更高阈值的cell,这样最少可以减小leakage power;现在innovus也可以在PnR阶段读saif文件去优化dynamic power。

在IR/EM signoff阶段,有一种违例类型就是:功耗太大的cell(驱动太大和Vt太小),然后会让block负责人去报这条路径下的setup余量,假如有,可以换功耗小的cell(小驱动和高Vt),这也是一种fix IR/EM的方式。

3.LVT cell做时钟树一定比SVT做时钟树功耗大吗?

这里只讨论时钟树的功耗,之前的实验结果显示:LVT cell做时钟树并不一定比SVT做时钟树功耗大。首先从leakage power的角度讲,假如时钟树的buffer/invert级数一定,LVT cell leakage power肯定比SVT大;但是SVT换成LVT,时钟树的级数一定不变吗(怎么变?)?dynamic power(transition,load)也会变小吗?

编辑:黄飞

-

MOS管

+关注

关注

111文章

2814浏览量

77891 -

Cell

+关注

关注

0文章

19浏览量

17783

原文标题:搞芯片不懂cell别乱用!看看Vt cell都是啥?

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

lcd的显示速度跟哪些因素有关呢?

MOS管阈值电压与沟长和沟宽的关系

如何突破EDA封锁 卷起来的阈值电压

NMOS晶体管的阈值电压公式 nmos晶体管的阈值电压与哪些因素有关

影响MOSFET阈值电压的因素

什么是MOS管亚阈值电压?MOSFET中的阈值电压是如何产生的?

浅谈影响MOSFET阈值电压的因素

MOSFET阈值电压是什么?影响MOSFET阈值电压的因素有哪些?

不同Vt cell工艺是怎么实现的?阈值电压和哪些因素有关系?

不同Vt cell工艺是怎么实现的?阈值电压和哪些因素有关系?

评论