题目说明

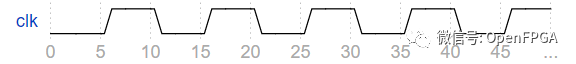

编写一个创建模块dut实例(具有任何实例名称)的测试平台,并创建一个时钟信号来驱动模块的clk输入。时钟周期为 10 ps。时钟应初始化为零,其第一个转换为 0 到 1。

模块端口声明

moduletop_module();

题目解析

生成clock有很多种方式,常见的就是forever和always。

timeunit1ps; timeprecision1ps; moduletop_module(); logicclk; dutu1_dut( .clk(clk) ); initialbegin clk<= 1'b0 ; end always #5 clk <= ~clk ; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 174-tb1

题目说明

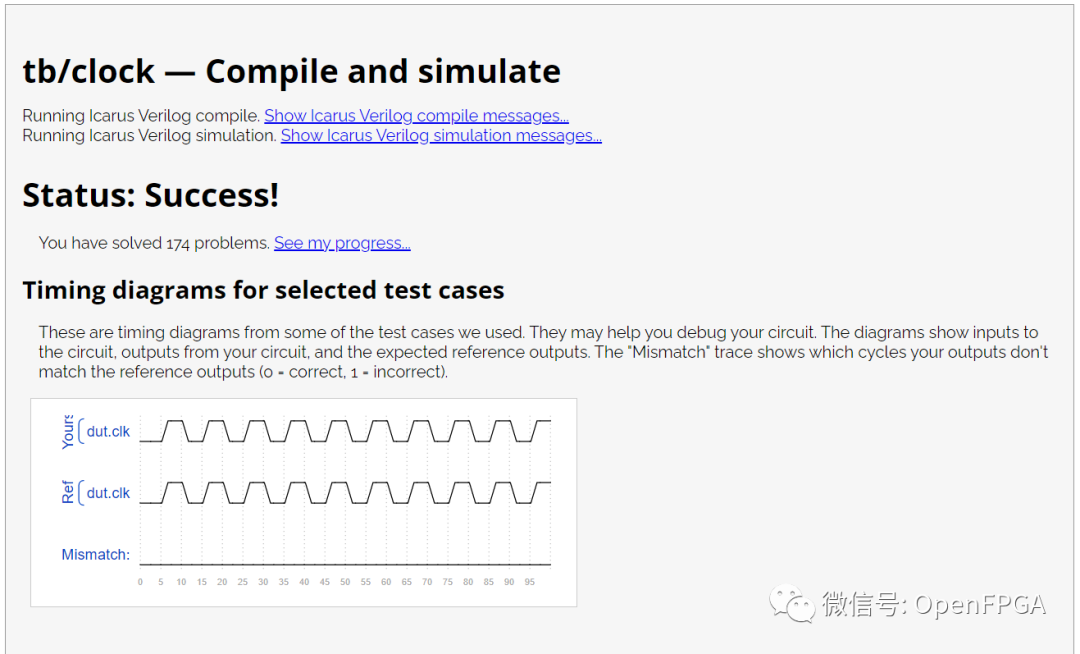

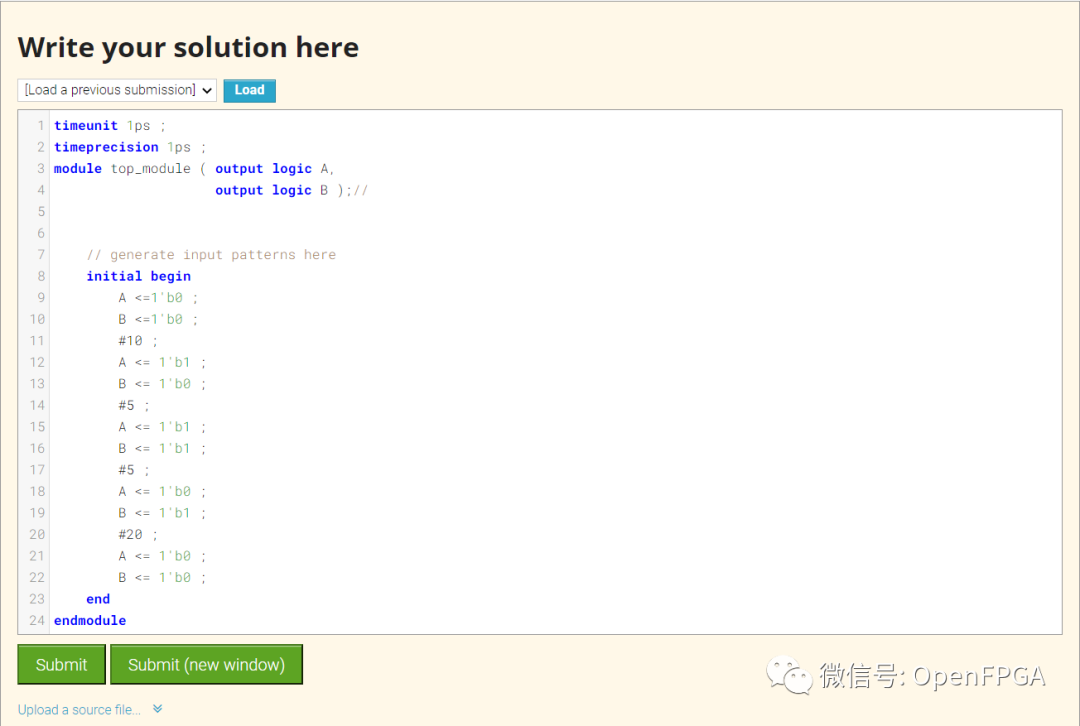

创建一个 Verilog 测试台,它将为输出 A 和 B 生成以下波形

模块端口声明

moduletop_module(outputregA,outputregB);

题目解析

initial+# n即可。

timeunit1ps; timeprecision1ps; moduletop_module(outputlogicA, outputlogicB);// //generateinputpatternshere initialbegin A<=1'b0 ; B <=1'b0 ; #10 ; A <= 1'b1 ; B <= 1'b0 ; #5 ; A <= 1'b1 ; B <= 1'b1 ; #5 ; A <= 1'b0 ; B <= 1'b1 ; #20 ; A <= 1'b0 ; B <= 1'b0 ; end endmodule

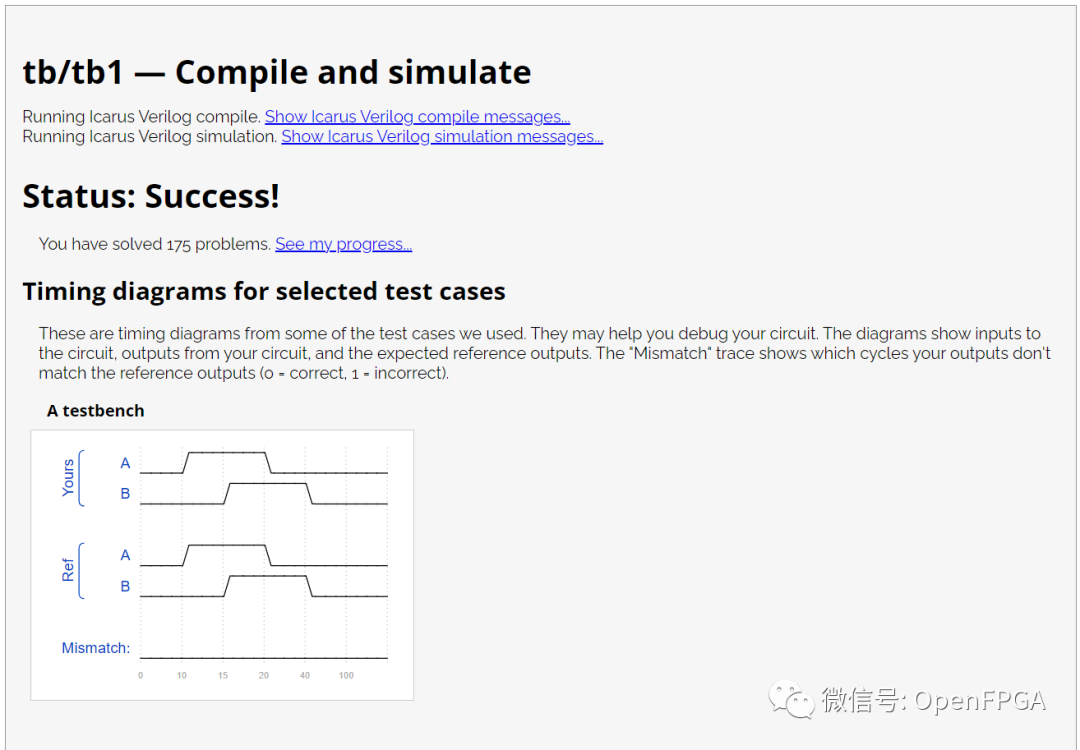

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 175-and

题目说明

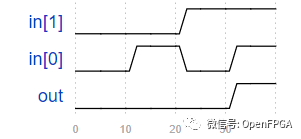

给给定的与门写测试文件,波形参考下图。

模块端口声明

moduletop_module();

题目解析

和上一题类似。

timeunit1ps; timeprecision1ps; moduletop_module(); logic[1:0]in; wirelogicout; andgateu_andgate( .in(in), .out(out) ); initialbegin in<= 2'b00 ; #10 ; in <= 2'b01 ; #10 ; in <= 2'b10 ; #10 ; in <= 2'b11 ; end endmodule

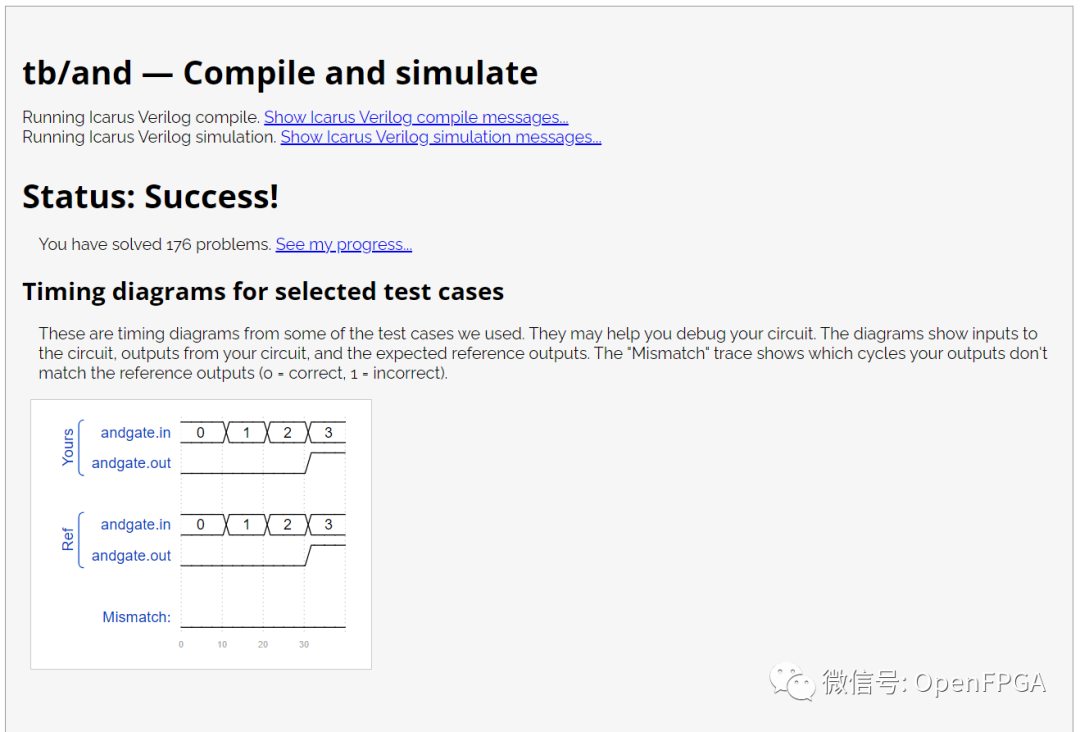

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 176-tb2

题目说明

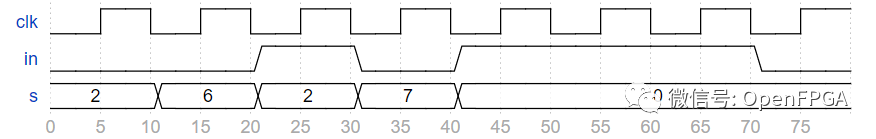

给定一个q7电路,按照下图编写testbench:

模块端口声明

moduletop_module();

题目解析

timeunit1ps; timeprecision1ps; moduletop_module(); logicclk; logicin; logic[2:0]s; wirelogicout; q7u1_q7( .clk(clk), .in(in), .s(s), .out(out) ); initialbegin clk<= 1'b0 ; forever #5 clk <= ~clk ; end initial begin in <= 1'b0 ; s <= 3'd2 ; #10 ; in <= 1'b0 ; s <= 3'd6 ; #10 ; in <= 1'b1 ; s <= 3'd2 ; #10 ; in <= 1'b0 ; s <= 3'd7 ; #10 ; in <= 1'b1 ; s <= 3'd0 ; #30 ; in <= 1'b0 ; s <= 3'd0 ; end endmodule

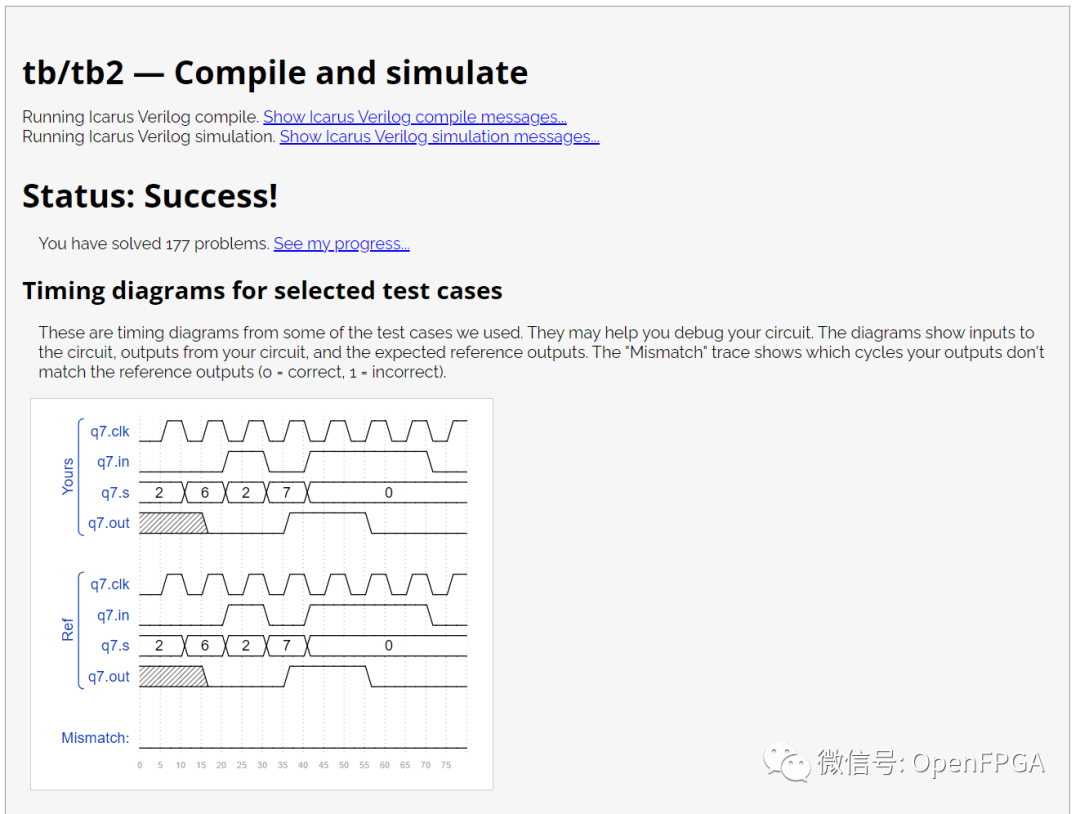

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

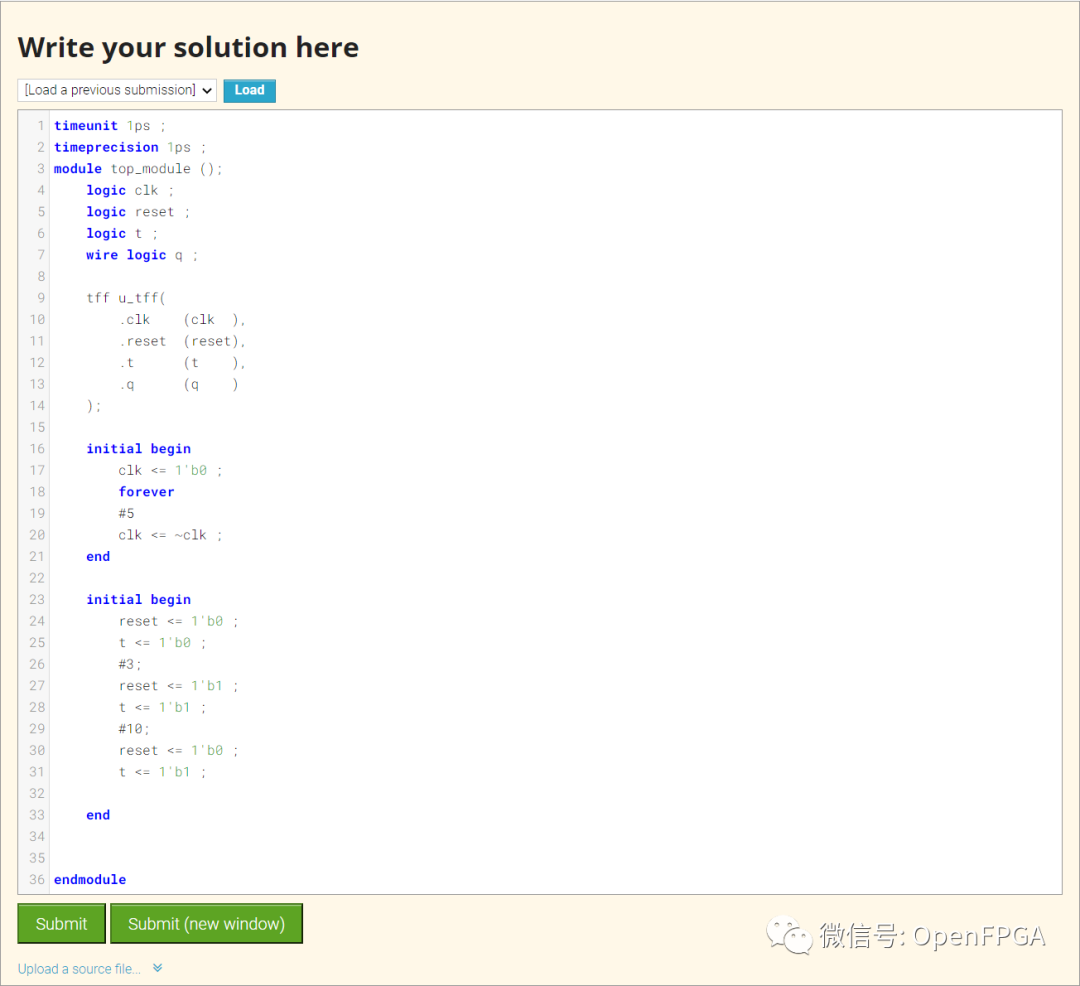

Problem 177-tff

题目说明

给题目中给定的tff编写测试文件。

模块端口声明

moduletop_module();

题目解析

timeunit1ps; timeprecision1ps; moduletop_module(); logicclk; logicreset; logict; wirelogicq; tffu_tff( .clk(clk), .reset(reset), .t(t), .q(q) ); initialbegin clk<= 1'b0 ; forever #5 clk <= ~clk ; end initial begin reset <= 1'b0 ; t <= 1'b0 ; #3; reset <= 1'b1 ; t <= 1'b1 ; #10; reset <= 1'b0 ; t <= 1'b1 ; end endmodule

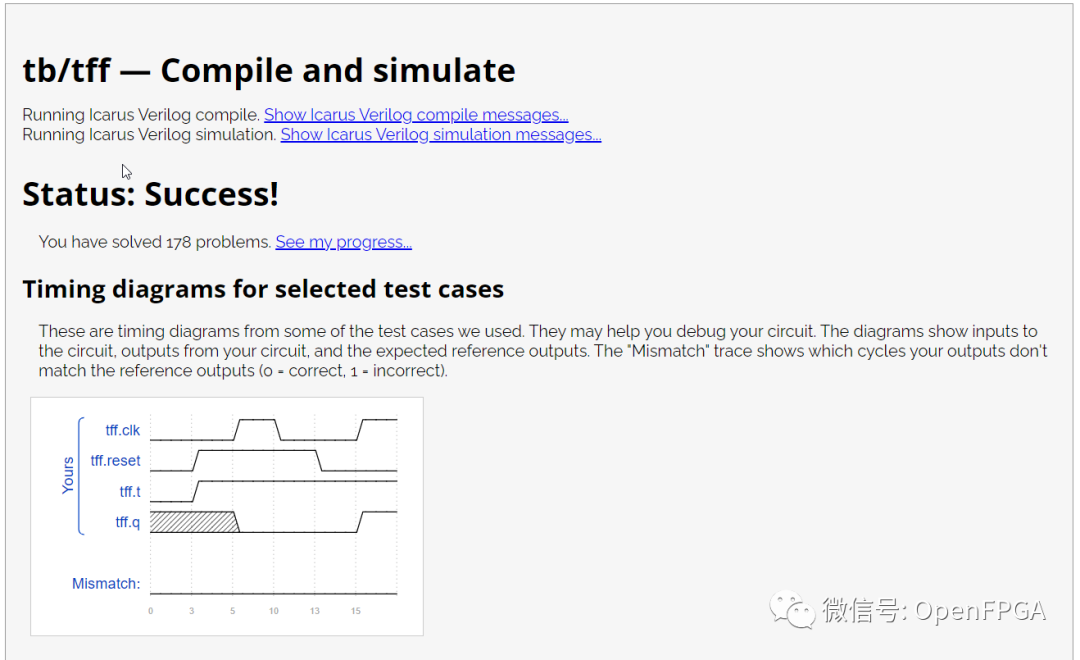

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

审核编辑:刘清

-

Verilog

+关注

关注

28文章

1351浏览量

110163 -

HDL

+关注

关注

8文章

327浏览量

47411 -

时钟信号

+关注

关注

4文章

449浏览量

28596 -

CLK

+关注

关注

0文章

127浏览量

17184

原文标题:HDLBits: 在线学习 SystemVerilog(二十四)-Problem 163-177(TestBench)

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何在PetaLinux流程外创建模块

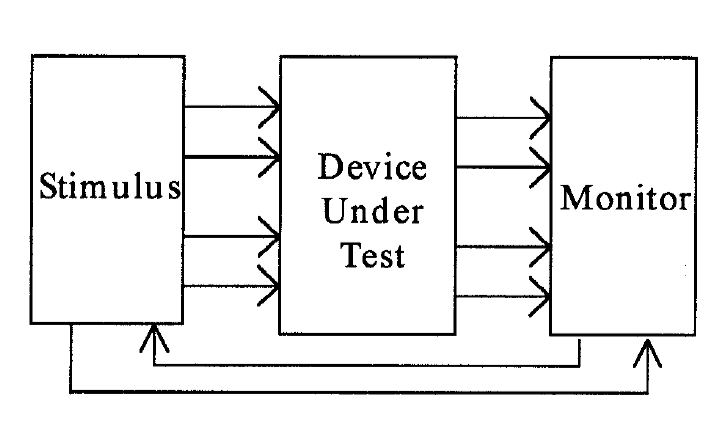

FPGA固件开发- 测试平台的编写

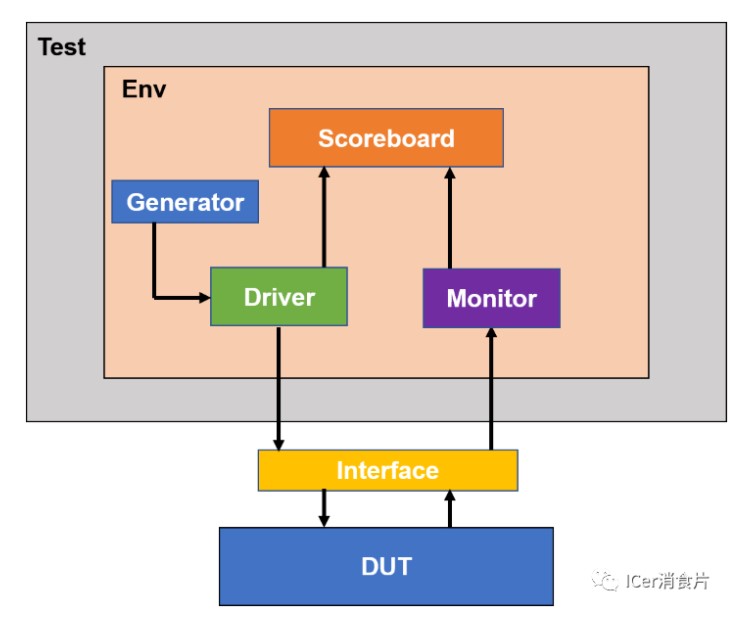

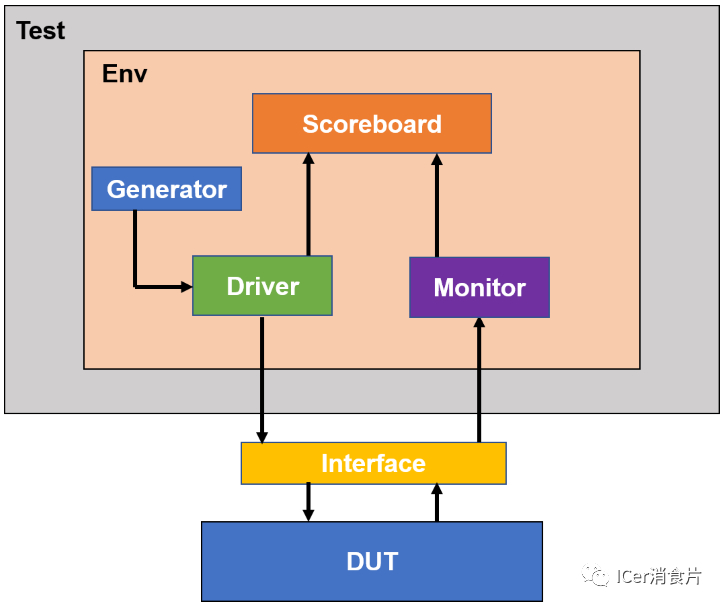

数字IC验证之“构成uvm测试平台的主要组件”(4)连载中...

Simulink建模仿真实例快速入门

Verilog HDL硬件描述语言_建模实例

PCB设计:网络分析仪测试DUT出现2个差不多的阻抗?

VHDL测试平台编写综述

编写一个创建模块dut实例的测试平台

编写一个创建模块dut实例的测试平台

评论