双倍数据速率(DDR)同步动态随机存取存储器(SDRAM)最近越来越受欢迎。DDR 内存需要跟踪主内存电压 VDDQ 的主动端接 VTT。本应用笔记提供开关稳压器方案,利用MAX1957脉宽调制(PWM)降压控制器为VTT端接提供1/2跟踪输出。

双倍数据速率 (DDR) 同步动态随机存取存储器 (SDRAM) 越来越受欢迎,因为在相同时钟速度下,与 SDRAM 相比,它可以提供双倍的数据速率并降低功耗。这些优势带来了更复杂的端接电压要求。

DDR 端接电源 VTT 现在必须能够提供和吸收电流。VTT 必须跟踪 1/2VDDQ,即输出电源电压(目前 VDDQ 为 2.5V,精度为 ±3%)。输入接收器现在是一个差分级,需要一个基准偏置VTTR,它必须跟踪终端电压VTT到±40mV以内(参考JDEC标准JDSD79和JDSD8-9)。

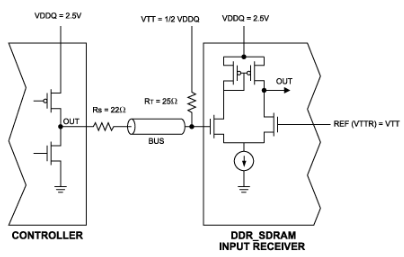

图1是一个典型的输出缓冲器和输入接收器级,在DDR_SDRAM单端接系统中具有2.5V (SSTL-2)的串联短截线端接逻辑。对于双端接,用于长总线,总线两端各有两个RT端接。

图1.单端接 SSTL-2 DDR_SDRAM系统。

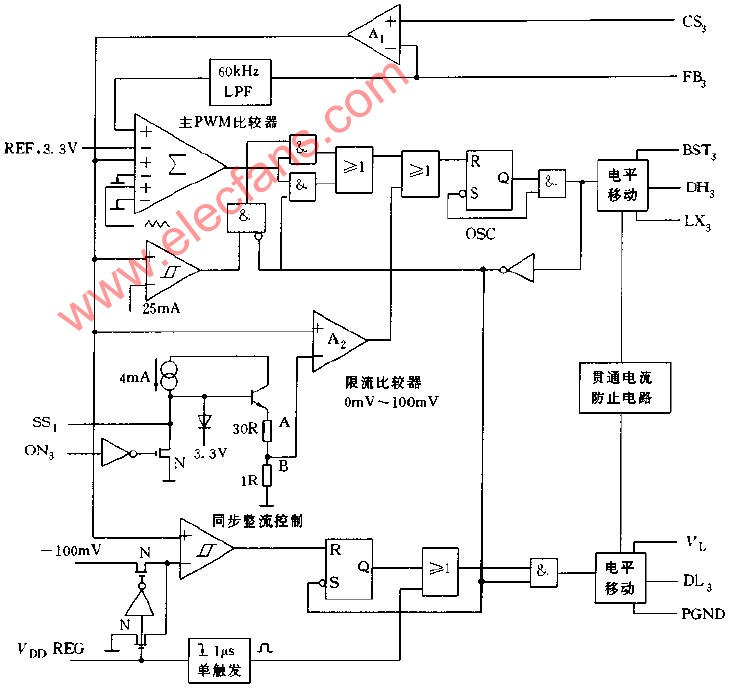

图2中的MAX1957电路提供VTT和VTTR用于DDR_SDRAM。MAX1957具有基准输入(REFIN),连接到内部误差放大器的同相输入,将输出VTT调节至与REFIN相同的电压。为了使VTT和VTTR跟踪1/2VDDQ,REFIN由VDDQ的电阻分压器(R1和R2)开发。电容C6为去耦滤波器。MAX1957工作在恒定频率PWM,使得VTT能够根据DDR-SDRAM的要求提供和吸收电流。图 2 中使用的组件提供超过 3 安培的拉电流和灌电流能力,这是 128Mb 内存系统的最大要求。

图2.MAX1957典型应用电路,用于VTT和VTTR。

表 1.MAX1957典型应用电路的元件列表

| 元件 | 数量 | 描述 |

| C1 | 1 |

电容 10μF/6.3V X5R 陶瓷。 太阳汤殿:JMK212BJ106MG |

| C2 | 1 |

电容 4.7μF/6.3V X5R 陶瓷。 太阳汤殿:JMK212BJ475MG |

| C3 | 3 | 电容 22μF/6.3V |

| C4,C5 | 2 |

电容 0.1μF/50V X7R 陶瓷。 太阳汤殿 UMK107BJ104KA |

| C6 | 1 |

电容 1500pF/50V X7R 陶瓷。 村田制作所GRM89X7R152K50 |

| C7, C8, C9 | 3 |

电容 270μF/2V SP 电容器。 松下EEFUE0D271R |

| C10 | 1 |

瓶盖 470pF/50V X7R 陶瓷。 村田制作所: GRM89X7R471K50 |

| C11 | 1 |

电容 68pF/50V X7R 陶瓷。 村田制作所: GRM39COG680J50 |

| D1 | 1 |

二极管, 肖特基, 30V, 100mA, SOT-23. 中央:CMPSH-3 |

| 集成电路 | 1 | IC,同步降压控制器:MAX1957 |

| L1 | 1 |

电感器, 2.7μH, 6.6A. 线艺: DO3316P-272HC |

| R1、R2 | 2 | 电阻, 0805, 1K, 1% |

| R3 | 1 | 电阻 51K, 0805, 5% |

| R4 | 1 | 电阻 10K, 0805, 5% |

| Q1/2 | 1 |

晶体管, 双通道 MOSFET 仙童 FDS6890A 20V, 0.018Ω |

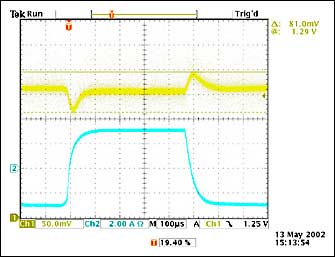

图 3 显示了在 VTT 上承受 -3A 至 +3A 阶跃负载时的 VTT 和 VTTR。VTT的峰值电压偏差小于±40mV。

图3.顶部迹线:电压VTT(交流耦合)。底部迹线:电流ITT步进从-3A到+3A和从+3A到-3A。

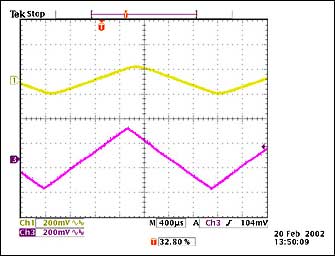

图 4 显示了 VDDQ,随着 VDDQ 的上升和下降,VTT 跟踪到 VDDQ 的一半,显示 VTT 的变化是 VDDQ 变化的一半。

图4.顶部迹线:电压VTT(交流耦合)。底部迹线:2.5V VDDQ(交流耦合)。

已经表明,MAX1957可用作同步降压转换器的控制器,以提供终止电压V电传用于DDR_SDRAM系统。对于要求更高电流的应用,MAX1957的驱动电路能够驱动较大的外部功率MOSFET,输出电流高达20A。

审核编辑:郭婷

-

控制器

+关注

关注

112文章

16487浏览量

179806 -

存储器

+关注

关注

38文章

7534浏览量

164489 -

DDR

+关注

关注

11文章

717浏览量

65599

发布评论请先 登录

相关推荐

符合JEDEC标准的两款终端稳压器BD3539FVM和BD3539NUX

1.2V至5.5V的输出电压和2V至5.5V的输入电压的STEVAL-ISA063V2

3.0V至5.5V的ISL83386E带独立发射机/接收机逻辑电源

如何使用线性调节器简化DDR-SDRAM终端

DC634A LT1930AES5演示板 | APD偏置电源,3V至5.5V输入,VOUT = 30V至90V(高达2mA)

耐辐射保障3V至5.5V输入、3A 同步降压转换器TPS7H4002-SP数据表

耐辐射保障3V至5.5V输入、3A 同步降压转换器TPS7H4002-SP数据表

THVD1400V 3V至5.5V RS-485收发器数据表

THVD24xxV ±70V故障保护、3V至5.5V RS-485收发器数据表

用于DDR-SDRAM终端的电源工作在3V至5.5V输入电压

用于DDR-SDRAM终端的电源工作在3V至5.5V输入电压

评论