一、概述

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习LUT如何构成组合逻辑。

二、LUT实现原理

LUT,中文名字叫做查找表,其原理其实也就是一个一个查找表,根据输入去找到相应位置的信号,然后做输出。说白了就好像一个小容量的ROM,把输入当作地址信号,对LUT里面预存的内容进行寻址。

7系列的FPGA的LUT有6个输入端口(A1-6),然后有两个输出端口(O5,O6)。下图是SLICEL里面的LUT。

其可以实现6输入的布尔组合逻辑函数,输入信号为A1,A2,A3,A4,A5,A6,输出端口为O6。如下

O6=f(A1,A2,A3,A4,A5,A6)

其实现方式就是将输入(A1,A2...A6)对应的输出在LUT里面预存好(这一步在我们用bit文件配置FPGA时实现),然后把输入信号当作地址信号去把对应的输出信号调出来。

同样其还可以构成两个5输入的布尔组合逻辑函数,其中这两个函数共用5个输入信号(A1,A2,A3,A4,A5),A6被拉高,O5,O6分别是两个布尔逻辑的输出。

O5=f(A1,A2,A3,A4,A5)

O6=f(A1,A2,A3,A4,A5)

故这也相当于实现的是一个5输入2输出的逻辑函数。

[O5,O6]=f(A1,A2,A3,A4,A5)

三、总结与提升

总结一下,就好比单个LUT里面可以预存 2^6=64个结果。那么单个LUT可以实现

(1)输入信号最多为6bit,输出信号为1bit的的布尔逻辑函数;

(2)输入信号最多为5bit,输出信号为2bit的逻辑。

一个SLICE里面有四个LUT故最多可以预存的输出信号个数为 2^6*4=2^8。

因此在一个SLICE里面,借助选择器将多个LUT进行互连,可以实现输入数,输出数最多为如下所示的逻辑。

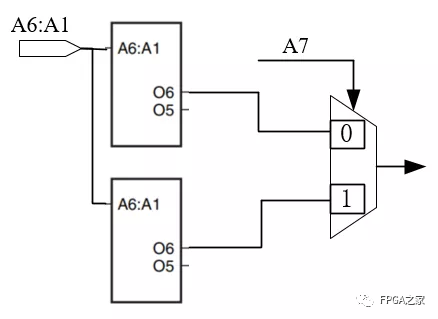

(1)2个LUT通过互连可以构成7bit输入,单bit输出的逻辑。实现方式为两个LUT的输入信号A1,A2,A3,A4,A5,A6接到一起,输出信号经过选择器选择输出,选择器的选择信号也是逻辑函数的一个输入信号。

将逻辑函数的输出送到Storage Element便可以形成同步时序逻辑。

(2)4个LUT通过互连可以构成8bit输入,单bit输出的逻辑。实现方式大家可以根据上面的实现方式自行推理。

(3)2个LUT通过互连可以构成6bit输入,2bit输出的逻辑。实现方式自行推理。

(4)4个LUT通过互连可以构成7bit输入,2bit输出的逻辑。实现方式自行推理。

超过8输入的布尔逻辑就需要多个SLICE来实现。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22509浏览量

639595 -

逻辑函数

+关注

关注

1文章

23浏览量

9752 -

组合逻辑

+关注

关注

0文章

48浏览量

10402 -

LUT

+关注

关注

0文章

52浏览量

13207 -

CLB

+关注

关注

0文章

30浏览量

6399

原文标题:初识FPGA CLB之LUT实现逻辑函数

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

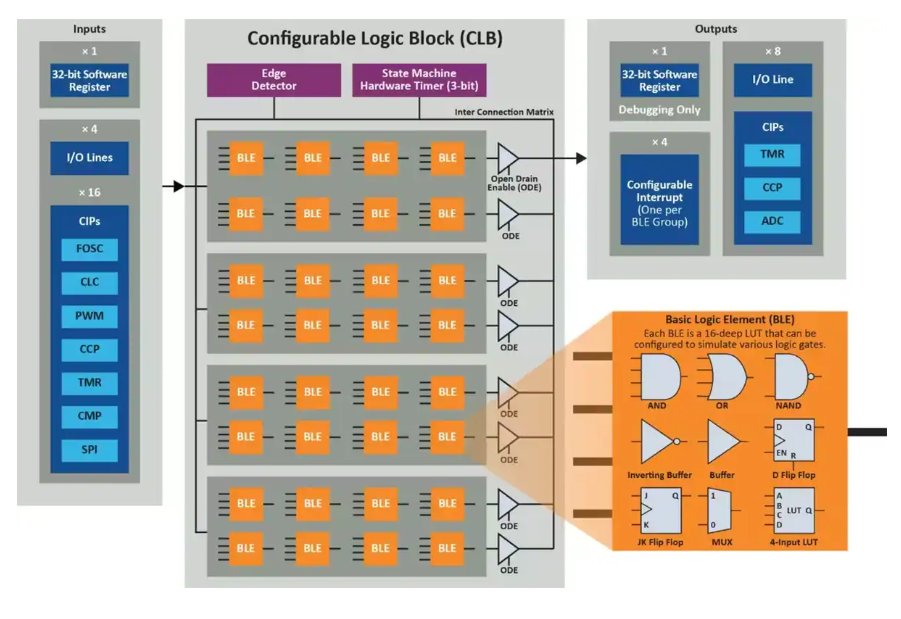

Microchip CLB-MCU融合方案:重构时序关键系统设计范式

SN54LS181、SN54S181、SN74LS181、SN74S181算术逻辑单元/函数发生器详解

SN54AS181B与SN74AS181A算术逻辑单元/函数发生器:特性、应用与设计考量

探索 SN54LS181、SN54S181、SN74LS181 和 SN74S181 算术逻辑单元/函数生成器

工程师高培解读XilinxVivadoFPGA设计进阶与AI自动编程

赛灵思FPGA电源解决方案全解析

【黑金云课堂笔记】第一~二期知识点总结

核芯互联正式发布国产高性能时钟缓冲器芯片CLB7043

FPGA 入门必看:Verilog 与 VHDL 编程基础解析!

复杂的软件算法硬件IP核的实现

PIC16F13145微控制器技术解析:CLB架构与低功耗设计

FPGA利用DMA IP核实现ADC数据采集

基于FPGA实现FOC算法之PWM模块设计

初识FPGA CLB之LUT实现逻辑函数

初识FPGA CLB之LUT实现逻辑函数

评论