本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

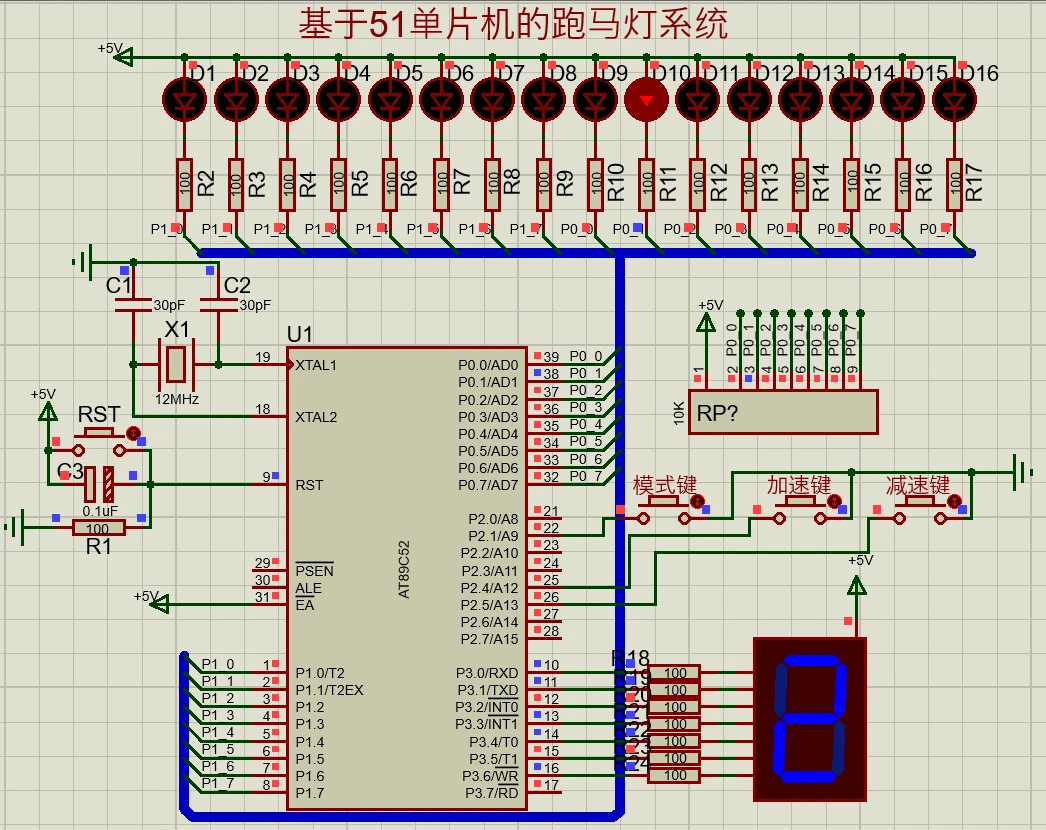

LED流水灯设计

在学习软件设计时,第一个例程总是“hello world!”,那么学习硬件时,也会有硬件的“hello world”------流水灯。本篇硬件基于叁芯智能科技的 SANXIN-B01开发板,如有想要入手,可查看以下链接,官方淘宝店已上架。

在FPGA开发板上有四个LED,我们要做的流水灯,顾名思义就是要LED像流水一样的点亮熄灭。直白点说就是,点亮第一个一段时间,然后熄灭第一个的同时,点亮第二个·····。在此,我们设置每一个LED点亮的时间为1秒钟。

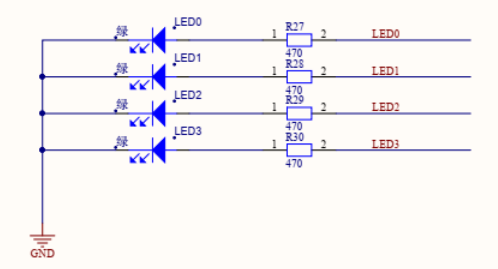

硬件介绍

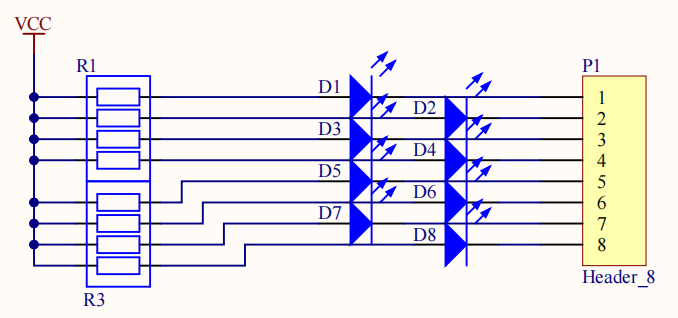

在我们的开发板上有四个LED,设计逻辑为:FPGA输出高电平时,LED点亮;FPGA输出低电平时,LED熄灭。

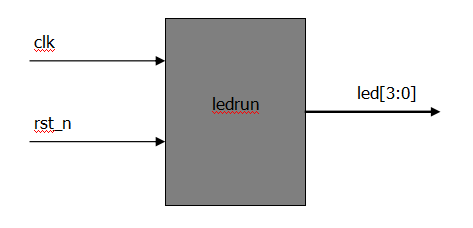

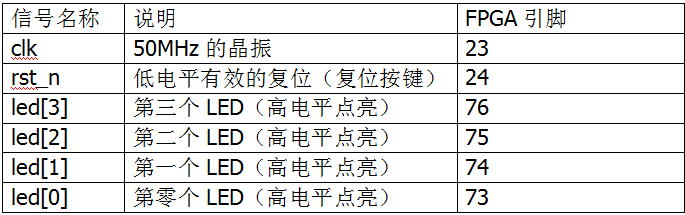

架构设计和信号说明

本设计的模块名称为ledrun。

建立工程、新建文件等步骤在专辑前篇中已经明确罗列,以后将不再叙述。这里给出超链接,方便参考学习。

设计代码

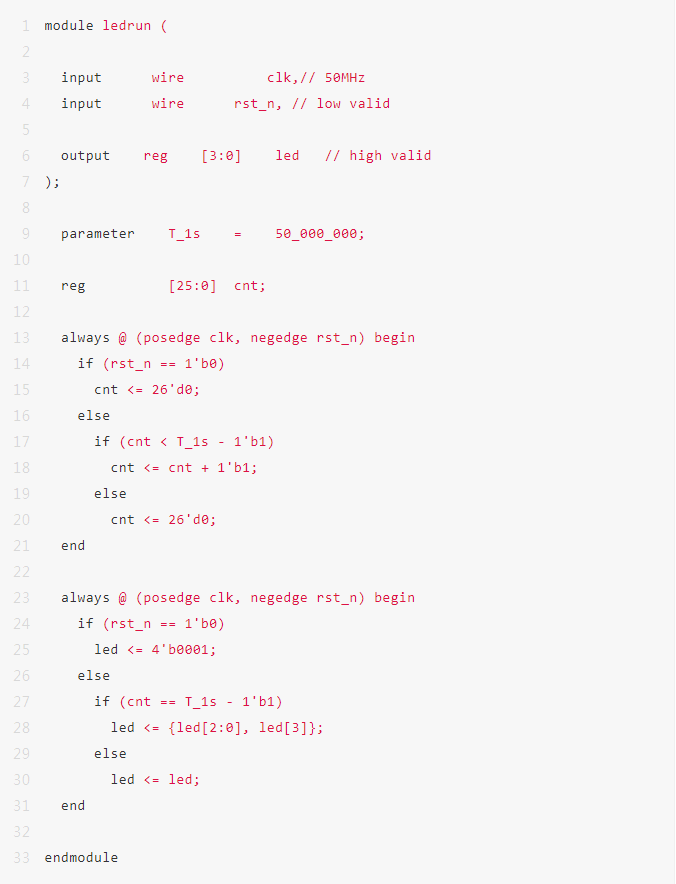

parameter可以定义一个参数(默认是32位)。在写代码时,对于某些数字,设计者经常利用定义参数的方式进行编写,方便修改,也方便阅读。

在硬件电路中,使用计数器当做计时器,每记录一个数字等于过去一个时钟周期。由于本设计中采用的clk为50MHz,所以经过50_000_000(在verilog中,如果是描述数字,中间的下划线只起到分隔的作用,不影响数值的大小)个周期正好为1秒钟。由于计数器是从0开始计数,所以计数器只需要记录到50_000_000-1即可。

为了能够记录到50_000_000-1这么大的数字,所以定义了一个26位的计数器cnt(参考附录1:设计中位宽的概念和计算位宽的小技巧)。

在verilog中,“{}”( 大括号)的第一个特殊作用为位拼接。{a,b}相当于将a和b拼接为一个整体,并且是高位为a,低位为b。

当led输出为4’b0001时,第一个led点亮;经过1秒钟,输出4’b0010时,第二个led点亮;经过1秒钟,输出4’b0100时,第三个led点亮;经过1秒钟,输出4’b1000时,第四个led点亮;经过1秒钟,输出4’b0001时,第一个led点亮······按照上述的过程周而复始,就形成了流水灯。

不难发现,led的输出,一直为3个0,1个1。并且1的位置每1秒钟移动一次,从头到尾,然后又到头。这种现象可以利用移位的思想进行实现。即:led[3]<=led[2]; led[2]<=led[1]; led[1]<=led[0]; led[0]<=led[3];如果将被赋值的组成一个整体,那就是led,赋值的组成一个整体就是{led[2:0], led[3]}。

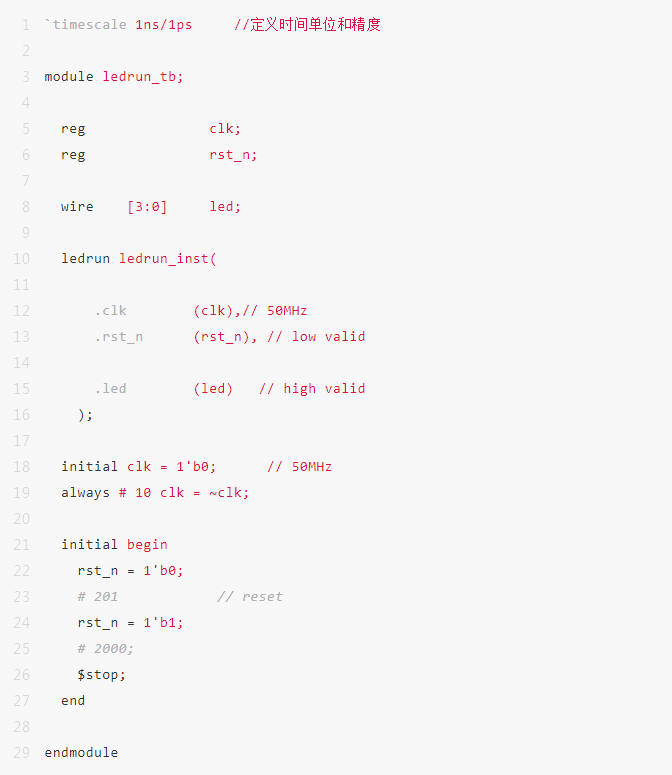

仿真代码

$stop是一个系统任务,功能为将modelsim的仿真停止。

设置好testbench后,运行分析综合后,打开RTL仿真。

波形分析

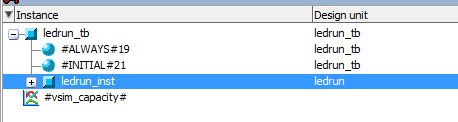

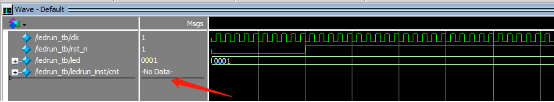

在modelsim中,打开sim窗口,选择ledrun_tb下的ledrun_inst。

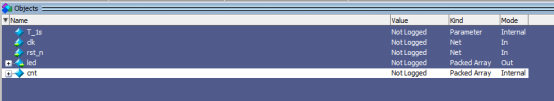

打开objects,将cnt选中。

objects窗口中显示在sim窗口中选中模块中所有的信号。

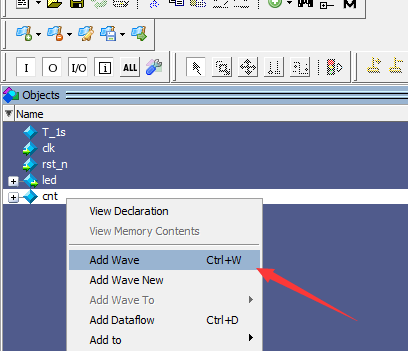

右击,将其添加入波形窗口。

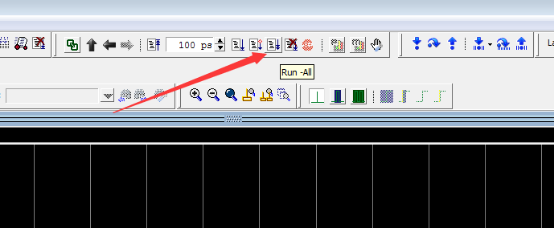

返回到wave窗口中,cnt信号已经添加到wave窗口中。由于新添加进来,没有数据(no data)。

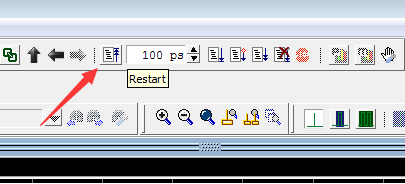

点击restart。

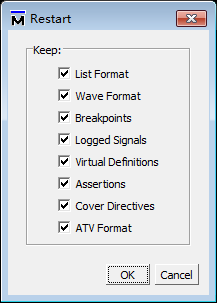

restart按钮为重新运行波形,点击后,软件会询问是否保持各种属性,点击ok即可。

wave窗口中所有的波形都处于no data 状态。点击run –all按钮,开始运行波形。

运行后,会自动停止。停止在tb文件中的$stop处。

返回wave窗口,各个信号都会有波形。

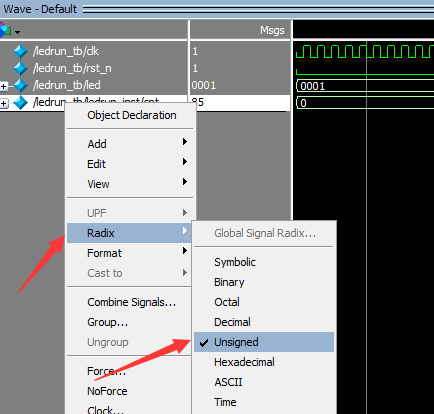

设置cnt的信号进制为无符号的十进制:右击cnt信号,选择radix中的unsigned。

把光标放到复位结束时,选择放大波形。

放大按钮的左侧第一个按钮为全局缩放,功能为将所有运行波形,显示到目前的窗口里;左侧第二个为缩小。最左边和最右边的按钮暂时用不到,这里不再介绍。

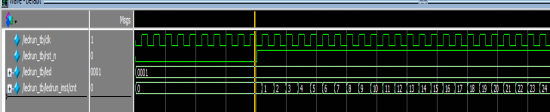

可以看到,在复位结束后,cnt信号每一个时钟周期都会增加1。

由于我们设计的流水灯是每1秒钟流动一个,在上述的仿真中,led数值是不会变化的。如果仿真几秒钟的话,仿真的时间会比较长。在此不建议仿真几秒钟的时长,有可能会导致电脑卡住。

仿真时,可以将T_1s的值,改成一个较小值。例如:5。然后在此编译仿真。

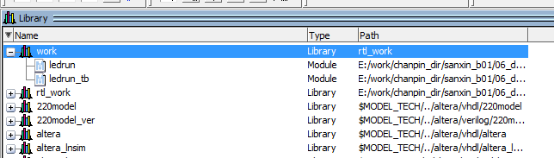

在quartus的编译器中,修改完后。进行综合分析,保证没有任何语法错误。在之前打开的modelsim中,打开library窗口,找到最上面的work,打开其前面的“+”。

选中刚才修改过的文件,右击,选择recompile。此时,modelsim会重新编译此文件。

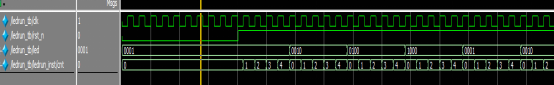

回到wave窗口中,点击restart,run-all。运行波形。

能够清楚的看到,led在进行移位,并且都是5个周期移动一次。

仿真通过后,关闭modelsim。回到quartus中,将参数修改成为50_000_000,综合分析后,分配管脚。布局布线,生成配置文件,进行下板测试。

开发板上的四个LED开始做流水状点亮。

本文由电子发烧友社区发布,转载请注明以上来源。如需社区合作及入群交流,请添加微信EEFans0806,或者发邮箱liuyong@huaqiu.com。

热门推荐干货好文

1、RK3568!四核64位ARMv8.2A架构,汇聚编译源码及实战样例

2、开源作品秀,教你如何DIY一款自己的声源跟踪小车

3、从零入门物联网OH开源平台,从简单到高阶项目,创客、电子爱好者都爱用!

4、低成本ESP32方案,支持OpenHarmony系统开发(附10+项目样例Demo)

5、从0到1玩转瑞萨RA4系列开发板,教你变着花样玩板子

6、四核64位,超强CPU ,看RK3568“竞”开发板DEMO!

8、全部开源 | 基于全志V85X的运动相机,工业网关,可穿戴式摄像头

9、高性能双核RISC-V,满足大多数开发,这款国产MCU工程师都爱

-

电子技术

+关注

关注

18文章

911浏览量

56189 -

电子发烧友论坛

+关注

关注

4文章

197浏览量

1124

原文标题:【教程分享】FPGA零基础学习:LED流水灯设计

文章出处:【微信号:gh_9b9470648b3c,微信公众号:电子发烧友论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【正点原子STM32H7R3开发套件试用体验】流水灯

低成本单片机方案——触摸流水灯开关控制

零基础嵌入式开发学习路线

FPGA 实验一:流水灯模块

【紫光同创盘古PGX-Nano教程】——(盘古PGX-Nano开发板/PG2L50H_MBG324第三章)键控流水灯实验例程

【紫光同创盘古PGX-MINI-4K教程】——(盘古PGX-MINI-4K开发板/PGC4KD-6ILPG144第二章)LED 流水灯实验例程

【紫光同创盘古PGX-Lite 7K教程】——(盘古PGX-Lite 7K开发板/PGC7KD-6IMBG256第二章)LED 流水灯实验例程

从入门到放弃……为什么你会觉得FPGA难学?如何学习FPGA?

【教程分享】FPGA零基础学习:LED流水灯设计

【教程分享】FPGA零基础学习:LED流水灯设计

评论