光子技术正在成为新一代半导体技术。

就像电子技术一样,光子技术如今正在推动全球经济的发展。据预测,从2021年到2027年,硅光子芯片收入将从1.52亿美元增长到约9.7亿美元,年复合增长率达36%。目前通信设备占据光子市场90%的份额。随着网速从100 Gbps提升到400 Gbps,再到采用电子开关ASIC的共封装光子器件迅速从26.6 Tbps发展到51.2 Tbps,这个市场还将持续扩大。 集成光子设计的真正增长点将发生在汽车行业的激光雷达和光纤陀螺仪(FOG)、医疗行业的免疫测定和光学相干断层扫描(OCT)、消费保健行业的可穿戴设备传感器、人工智能和量子计算行业的光计算加速器,以及高性能计算(HPC)行业的光互连等领域。

硅光子技术的主要挑战则包括更好的激光集成、先进的封装(包括小芯片设计)、硅通孔(TSV)、光子中介层,以及可加快光子调制的新材料。开发者需要更好的设计工具和方法,才能成功设计和测试这些新系统。

英特尔案例分享

用于光计算的集成光子电路

2000年后,单线程和处理速率趋于饱和,行业转向了集成内核来实现更多的并行计算,以此提高计算性能。由于处理器内核数量的大幅增加,计算瓶颈转移到了片外I/O带宽,以及驱动各类处理器之间的片外信号所需的功耗提升。不久之后,芯片I/O和互连所需的功耗就超过了计算所需的功耗。所以说,带宽密度和信号延迟必须大幅提高,而光计算互联(OCI)则在满足这些需求上起着重要作用。

在英特尔的构想中,电子小芯片(EIC)和光子小芯片(PIC)是分开的,这样就可以分别使用各领域的出色技术。为了实现电子小芯片和光子小芯片之间的低损耗、高带宽通信,英特尔采用了3D堆叠技术。电子小芯片包含变速箱逻辑、信号到光的格式转换,以及驱动和控制组件,而光子小芯片则处理所有的发射、接收和光纤耦合。英特尔在电子小芯片上集成了激光器和SOAs,从而降低功耗并提高整个系统的可靠性。

这一系统的优势包括:能够实现计算扩展和资源共享,电子小芯片可插拔光子学封装产量更高,封装前能够对已知合格裸片进行基于晶圆的测试。而且在同一裸片上集成所有光子组件时,功耗更低、带宽密度更高、成本更低、可靠性更高。

英特尔的一个典型OCI架构有8个激光器,并通过微环谐振器使用200GHz的间隔进行调制和滤波。偏振管理和信号放大在接收端完成,之后信号会以交替方式注入偶数和奇数通道,并发送到单独的光电二极管。英特尔的一个OCI扩展路线图显示了单条光纤速度的扩展情况,从使用64G NRZ和16个波长时只有1 Tbps,一直到使用128G PAM4双极性和64个波长时大于10 Tbps。

Global Foundries案例分享

集成电子技术 V.S. 光子技术

CMOS的RF性能在大约45nm CMOS节点处达到顶峰。因此,Global Foundries (GF) 选择了该节点作为其光子产品的基础,其光子产品采用业界唯一的单片硅基平台,将高速RF-CMOS和光子融合在同一个芯片上。这种300mm晶圆工艺称为GF Fotonix,已于2022年初获得认证。GF针对多种设计工具平台提供了工艺设计套件(PDK)。该PDK包括有源和无源组件,以及各种针对数据中心通信应用的器件。

从光子设计到制造的完整生态系统需要四个要素,即批量PIC制造、EDA、IP和封装。过去几年,GF一直与领先的EDA供应商合作,推出了一个强大的光子PDK,该PDK可与EDA设计工具一起用于电路级光子芯片设计。该PDK相当于代工厂和客户之间的隐性合同,表明用该PDK设计的任何芯片均可制造。该PDK也充当了一个抽象层次,让开发者可以在电路层面而非器件层面开展设计,从而创建和制造更复杂的设计。

对于光子IP生态系统,该PDK以可编程布局单元、符号和仿真模型的形式来提供预表征的构建块,是IP生态系统的基础。不过,企业仍可以创建应用专用IP,如TIA、调制驱动器、DAC/ADC、具有加热器控制的光子DWDM滤波器,以及为特定终端应用领域创建的小芯片。

在封装方面,封装成本和行业在大批量生产上的技术成熟程度是集成光子技术全面普及的主要障碍。GF正在积极研发封装相关技术,以减少集成光子技术的采用障碍,其中包括低成本无源光纤连接、具有w/Cu-P和Cu u-pillars的回流兼容组装、2.5D兼容性、直接激光连接、JEDEC规格(如适用)和可满足客户封装需求的微电子OSAT模型。

POET案例分享

光子中介层

将晶圆级芯片封装拓展到光子系统中十分具有挑战性,其中最主要的挑战之一就是对数十亿复杂的异构系统进行组装、封装和测试。开发者们使用兼具电子和光子连接的通用中介层,对优质小芯片进行异构集成。借助中介层,开发者可以用已知合格的裸片来构建复杂的系统,并在晶圆层面完成中介层互连测试。

POET Technologies(POET)是数据中心、电信和人工智能市场中领先的光中介层与光子集成电路设计企业,他们提出了“光子中介层”的概念,即通过增加光子连接来扩展电子中介层。这样做的好处是消除了引线键合,降低了功耗并减少了小芯片之间的寄生效应,所有工艺均在完整的晶圆上通过自动化流程完成,一次可处理数百个。光子中介层具有电层和光层,可以采用8英寸或12英寸晶圆进行加工。中介层上混合集成了电子小芯片和光子小芯片,POET称之为“光学引擎”。

这一解决方案的一个主要优势是它使用的是传统的倒装芯片工艺技术。无源电子组件和光子组件印刷在硅中介层上,而有源组件以小芯片的形式混合集成到中介层上。光子中介层支持在电子中介层之间放置两个不相互作用的光波导层。光可以垂直或水平地耦合输入和输出。该技术支持硅通孔(TSV),因此中介层的两面都可以使用。如果在光子中介层中设计热隔离和管理,还能让热量远离激光器和谐振器件等敏感的光子元件。

在POET的几个小型100G和400G的收发器中,其空分复用通道从8个到16个不等,速度介于1.6 Tbps和3.2 Tbps之间,与使用分立组件的设计相比,尺寸缩小了75%。由于没有引线键合,信号完整性会更好。正因为信号完整性更好,POET目前正在考虑完全去除DSP,这样还可以再减少6瓦到8瓦的功耗。

新思科技布局

光学及光子学领域数十年

新思科技光子设计平台旨在让CMOS开发者能够使用与AMS类似的熟悉设计流程来推动集成光子设计。这方面的示例包括使用由原理图驱动的布局,利用布局的反向注释进行仿真,电子和光子版图与原理图一致性检查,以及针对曲线布局而调整的设计规则检查。

几乎所有光子芯片最终都会与电子芯片进行协同设计,两者有时还会进行共封装。EIC和PIC的协同设计和共封装为EDA供应商带来了更多的挑战,新思科技正在与客户一起应对这些挑战。

以下是新思科技光子解决方案的独特功能:

- 兼顾光子与电子技术的编译器

- 用于曲线布局的自动化全角度支持

- 自动波导连接,具有约束驱动的波导总线连接

- 使用反向波导连接进行准确的布局后光子仿真

- 光子电路和系统级仿真

- 电子/光学联合仿真

- 基于链接的仿真,具有驱动器、接收器、光纤、光放大器和分析模型

- 自定义器件工具流程,开发者可以用自己的器件来增强代工厂PDK

- 用于器件表征和CAD视图生成的麦克斯韦方程求解器

- 签核质量的DRC和LVS,以确保器件可制造

-

新思科技

+关注

关注

5文章

822浏览量

50517

原文标题:谁在提前布局光子赛道?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EastWave应用:自动计算光子晶体透反率

柠檬光子半导体激光芯片制造项目落户江苏南通

华为海思正式进入Wi-Fi FEM赛道?

什么是光子学?

光通信时代的引领者:光子晶体光纤

什么是单光子探测器

光子集成芯片是什么

简单认识微波光子集成芯片和硅基光子集成芯片

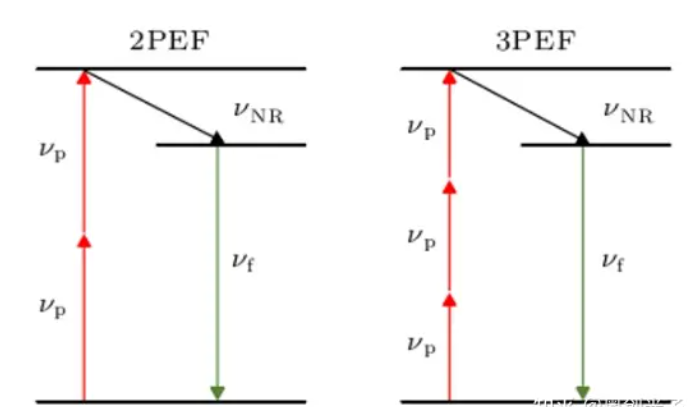

多光子成像技术原理及优势分析

谁在提前布局光子赛道?

谁在提前布局光子赛道?

评论