任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,终于找到了一种很简单的解读办法,可以看透它的本质,而且不需要再记复杂的公式了。

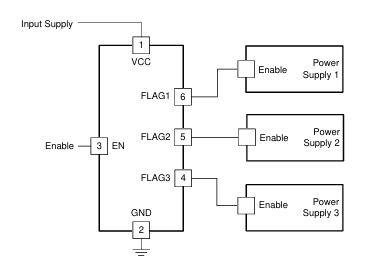

我们的分析从下图开始,下图是常用的静态分析结构图,一开始看不懂公式不要紧,因为我会在后面给以非常简单的解释:

这两个公式是一个非常全面的,准确的关于建立时间和保持时间的公式。其中Tperiod为时钟周期;Tcko为D触发器开始采样瞬间到D触发器采样的数据开始输出的时间;Tlogic为中间的组合逻辑的延时;Tnet为走线的延时;Tsetup为D触发器的建立时间;Tclk_skew为时钟偏移,偏移的原因是因为时钟到达前后两个D触发器的路线不是一样长。

这里我们来做如下转化:

因为对于有意义的时序约束,建立时间余量Tslack,setup和保持时间余量Thold都要大于0才行,所以对于时序约束的要求其实等价于:

Tperiod>Tcko+Tlogic+Tnet+Tsetup-Tclk_skew (1)

Tcko+Tlogic+Tnet>Thold+Tclk_skew (2)

之前说了,这两个公式是最全面的,而实际上,大部分教材没讲这么深,他们对于一些不那么重要的延时没有考虑,所以就导致不同的教材说法不一。这里,为了得到更加简单的理解,我们按照常规,忽略两项Tnet和Tclk_skew。原因在于Tnet通常太小,而Tclk_skew比较不那么初级。简化后如下:

Tperiod>Tcko+Tlogic+Tsetup (3)

Tcko+Tlogic>Thold (4)

简单多了吧!但是你能看出这两个公式的含义吗?其实(3)式比较好理解,意思是数据从第一个触发器采样时刻传到第二个触发器采样时刻,不能超过一个时钟周期啊!假如数据传输超过一个时钟周期,那么就会导致第二个触发器开始采样的时候,想要的数据还没有传过来呢!那么(4)式又如何理解呢?老实说,一般人一眼看不出来。

我们对于(4)式两边同时加上Tsetup,得到(5):

Tcko+Tlogic+Tsetup>Thold+Tsetup (5)

结合(3)式和(5)式,我们得到如下的式子:

Thold+Tsetup

这个式子就是那个可以让我们看出规律的式子。也是可以看出静态时序分析本质的式子。

Tcko+Tlogic+Tsetup是指数据从第一级触发器采样瞬间开始,传输到第二级触发器并被采样的传输延时。我们简称为数据传输延时。下面讲述(6)式两端的含义。

Tcko+Tlogic+Tsetup< Tperiod :约定数据传输延时不能太大,如果太大(超过一个时钟周期),那么第二级触发器就会在采样的时刻发现数据还没有到来。

Thold+Tsetup

综上,我们就可以知道,数据传输延时既不能太大以至于超过一个时钟周期,也不能太小以至于小于触发器采样窗口的宽度。这就是静态时序分析的终极内涵。有了这个,就不需要再记任何公式了。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:解读FPGA的静态时序分析

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22504浏览量

639302

原文标题:解读FPGA的静态时序分析

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

工程师高培解读XilinxVivadoFPGA设计进阶与AI自动编程

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

数字IC/FPGA设计中的时序优化方法

ADP7000系列示波器特色功能:抖动分析,捕捉时序之微

Chroma 80611 电源时序/安规综合分析仪:电器安全与性能的自动化验证专家

什么是CVE?如何通过SAST/静态分析工具Perforce QAC 和 Klocwork应对CVE?

vivado时序分析相关经验

FPGA测试DDR带宽跑不满的常见原因及分析方法

HarmonyOSAI编程智能代码解读

LM3880三轨简单电源时序控制器技术文档总结

汽车软件团队必看:基于静态代码分析工具Perforce QAC的ISO 26262合规实践

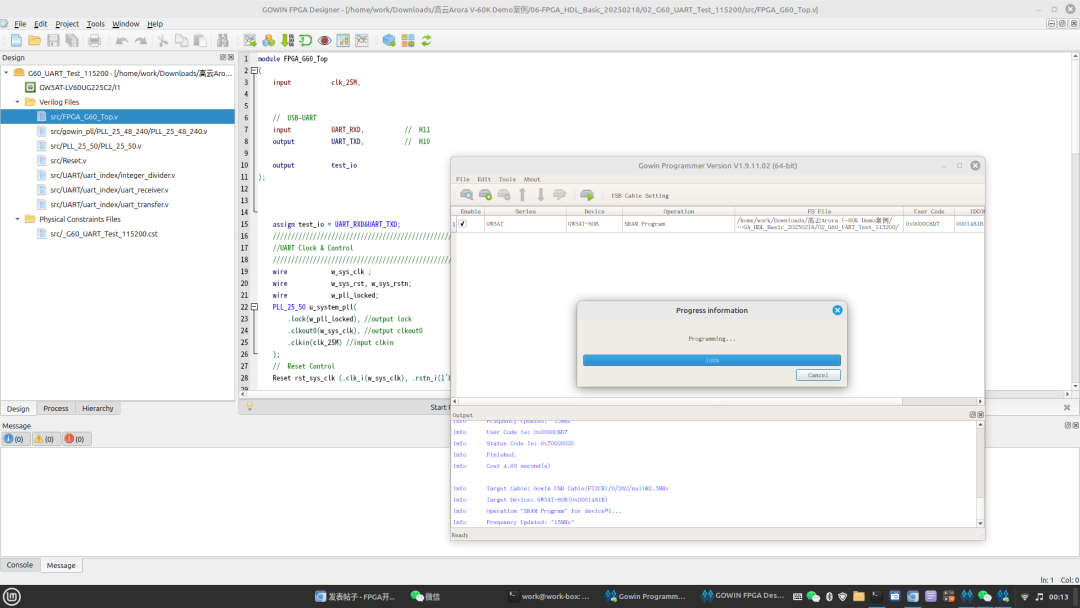

【经验分享】玩转FPGA串口通信:从“幻觉调试”到代码解析

解读FPGA的静态时序分析

解读FPGA的静态时序分析

评论