PCB工程师layout一款产品,不仅仅是布局布线,内层的电源平面、地平面的设计也非常重要。处理内层不仅要考虑电源完整性、信号完整性、电磁兼容性,还需要考虑DFM可制造性。

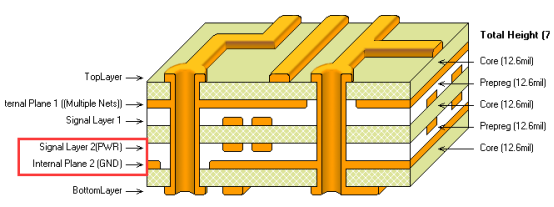

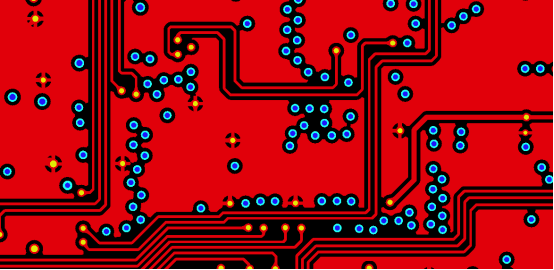

PCB表层是用来走线焊接元器件的,内层则是规划电源/接地层,该层仅用于多层板,主要用于布置电源线和接地线。我们称之为双层板、四层板和六层板,通常指信号层和内部电源/接地层的数量。

一、4个重要的内层设计问题

在高速信号,时钟信号,高频信号等关键信号的下面设计地线层,这样信号环路的路径最短,辐射最小。

高速电路设计过程中,必须考虑如何处理电源的辐射和对整个系统的干扰问题,一般情况电源层平面的面积小于地平面的面积,缩进2倍的介质厚度为最佳,可以对电源起屏蔽作用。

1、层叠规划

电源层平面与相应的地平面相邻,目的是形成耦合电容,并与PCB板上的去耦电容共同作用,降低电源平面阻抗,同时获得较宽的滤波效果。

2、选择参考平面

参考层的选择非常重要,理论上电源层和地平面层都能作为参考层,但是地平面层一般可以接地,屏蔽效果要比电源层好很多,所以一般优先选择地平面作为参考平面。

3、信号线不能跨区域走线

相邻两层的关键信号不能跨分割区,否则会形成较大的信号环路,产生较强的辐射和耦合。

4、电源、地走线规划

要保持地平面的完整性,不能在地平面走线,如果信号线密度太大,可以考虑在电源层的边缘走线。

二、影响内层制造的多种情况

由于PCB制造复杂的工艺流程,内层制造的工艺只是其中一部分,在生产内层板时还需考虑其他工序的工艺影响内层的制造能力,比如压合公差、钻孔公差都会影响内层的品质良率。

PCB的层数可分为单面板、双面板、多层板,这三种板子工艺流程也大不相同,尤其是多层板,生产工艺比单双面板复杂许多,因此在设计多层板时,需考虑多层板复杂的工艺流程及DFM可制造性设计。

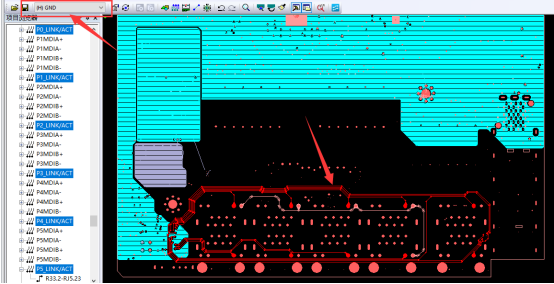

1、删除独立焊盘

独立焊盘就是非功能性的PAD,在内层不与任何网络相连,在PCB制造过程中会取消独立焊盘,因为此独立焊盘取消对产品的设计功能无影响,反而在制造时会影响品质及生产效率。

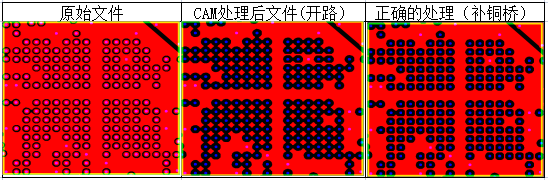

2、内层BGA区域

BGA器件比较小,引脚非常多,因此设计出的过孔非常密集,在制造过程中钻孔到走线、铜皮需要保留一定的间距,否则在压合及钻孔工序可能会短路,在保证钻孔距铜皮、走线留一定的距离时,孔与孔中间的铜无法保留,会导致网络开路,因此在CAM工程师处理BGA区域时需注意孔与孔中间的铜开路了需补铜桥,保证生产后网络连接不断开。

3、内层设计异常

内层负片的孔全部有孔环,转成正片图形就是所有孔与铜皮不相连完全隔离,完全隔离就等于内层没有任何作用,不做内层都可以,生产制造遇到此问题会跟设计工程师确认,是否设计异常,内层铜皮没有添加网络导致完全隔离。

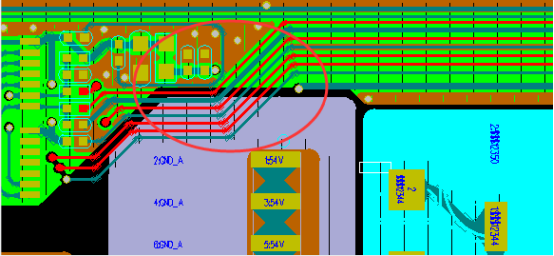

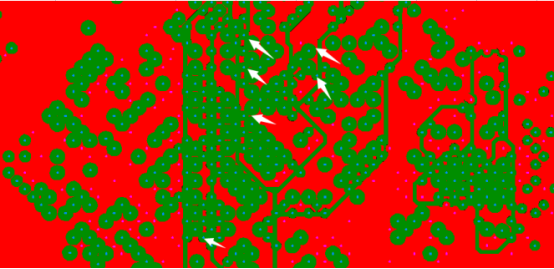

4、内层负片瓶颈

在内层设计电源层、地层分割时,由于过孔密集会出现网络导通的瓶颈,电源网络导通的铜桥宽度不够,会导致过不了相匹配的电流,从而导致烧板,甚至有些瓶颈位置直接开路,导致产品设计失败。

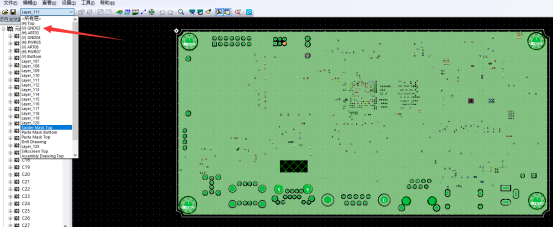

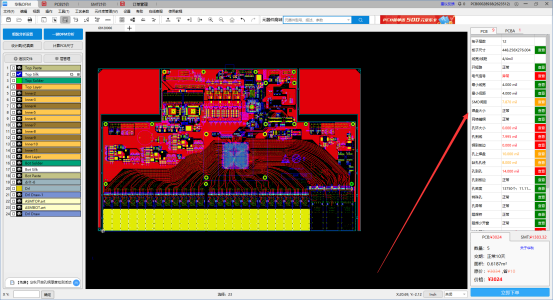

三、一键DFM检测内层设计

内层设计隐患繁多,很难提前规避所有风险,这里推荐一款华秋DFM可制造性分析软件,对于上文提到的可制造性问题都能够检测出来,并提示存在的制造风险,让设计工程师在制造前发现设计存在的缺陷,并修改检测的问题点,避免设计的产品在制造过程中出现问题,从而提升产品的成功率,减少多次试样的成本。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

软件下载地址(复制到浏览器下载) ↓

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_fsyzlh.zip

审核编辑黄宇

-

电源

+关注

关注

184文章

17671浏览量

249833 -

PCB

+关注

关注

1文章

1787浏览量

13204

发布评论请先 登录

相关推荐

【工程师进阶】搞懂PCB内层的可制造性设计是关键

【工程师进阶】搞懂PCB内层的可制造性设计是关键

评论