一、什么是数字后仿?

这是相对于数字前仿来说的。从概念上来说,数字验证包含两方面的内容,数字前仿和数字后仿。前者中timing被默认为理想情况,主要用来验证数字电路的功能,后者主要用来验证timing相关。数字后仿做为数字电路设计中重要的一环,用来检查时序是否满足,有没有时序违例的情况发生。数字后仿需要的文件有门级网表和sdf文件。工程师需要将sdf文件进行反标,从而使得仿真工具改变数字电路的默认timing。

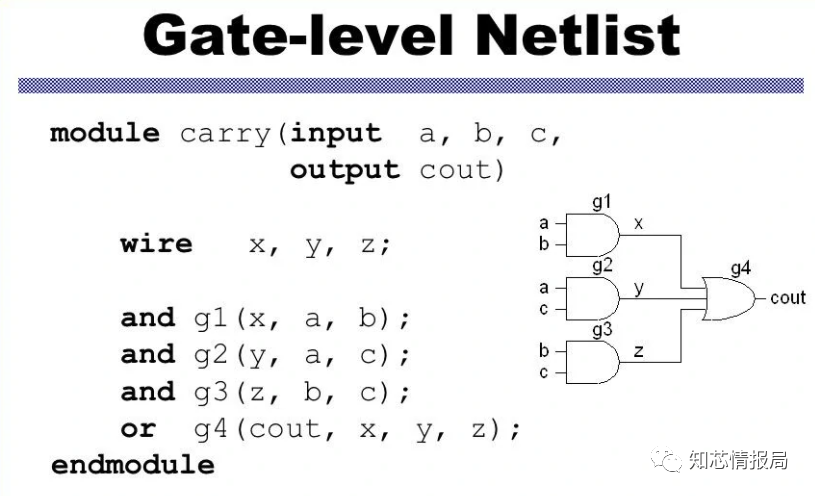

二、什么是门级网表?

数字前端设计的RTL代码 中的寄存器和组合逻辑,其物理实现还是对应到具体门电路。由于基本的寄存器或组合逻辑,对应的电路结构已经很稳定,电学特性也很明确,故而在综合级别较高的 EDA 工具中,一般不需要再亲自去描述它们的实现方法,而是调用现成的库信息。EDA 工具会根据 RTL 描述自动编译出门级的电路描述,这就是门级网表。门级网表分为pr前网表和pr后网表。

PR前网表:又称为综合(一般为Design Compiler)后网表,采用的是工艺库中default的timing,且只有cell的timing信息。此时由于内部的setup和hold没有修好,会出现不少violation的情形。

PR后网表:相比于pr前网表,pr后网表加上了buf,decap,filler和antenna等器件,timing信息也与pr前网表一致。

三、什么是sdf文件?

SDF文件(standard delay format),直译过来就是标准延时格式。它描述设计中的timing信息,指明了模块管脚与管脚之间的delay,时钟到数据的delay,内部连接delay等。后端布局布线之后由“QRC”出spef,通过PT生成sdf,所以sdf中timing信息都是布局布线之后客观存在的timing。总而言之,SDF文件是把布局布线过程中的器件延时和线延时信息记录下来,从而在进行路径时序分析时可以将整条路径的时序计算出来,再根据时序约束条件判断是否满足时序要求。

设计过程中如果时序不满足时需要多次迭代的。每次布局布线后都会通过QRC抽取连线寄生参数,配合timing library得到当前的SDF时序反标信息,从而帮助设计人员对时序违背的路径进行修改。一般来讲,在时序收敛前用SDF分析帮助修改设计,时序满足后,利用SDF进行动态仿真double check下时序满足情况。

四、如何反标sdf文件?

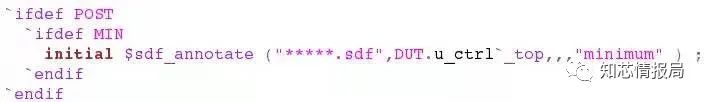

较为常见的方法是在bench中调用系统函数$sdf_annotate来完成。还有其他的方法,比如作为elaboration的选项指定等。$sdf_annotate的标准格式如下:

$sdf_annotate(“sdf_file”[,module_instance][,“sdf_configfile”][,“sdf_logfile”][,“mtm_spec”][,“scale_factors”][,“scale_type”]);

其中:

“sdf_file”:指定SDF文件的路径。

“module_instance”:指定反标设计的范围(scope)

“sdf_configfile”:指定SDF配置文件

“sdf_logfile”:指定VCS保存error 和warnings消息的SDF日志文件。也可以使用+sdfverbose runtime option来打印所有反标消息

“mtm_spec”:指定延迟类型"MINIMUM(min)", "TYPICAL(typ)“或者"MAXIMUM(max)”。

“scale_factors”:分别指定minmax的缩放因子,默认是"1.01.0"

“scale_type”:指定缩放之前延迟值的来源。

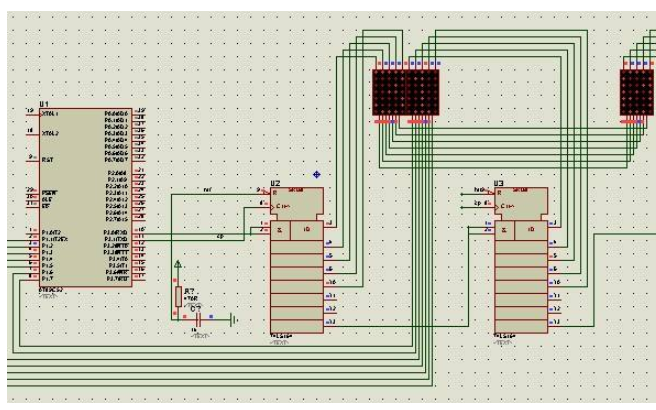

如下图举例:

在反标SDF后,specify块中定义的延迟不再有用,取代的将是SDF文件中的延迟。So,如何在芯片数字后仿中反标sdf,你了解了吗?

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5336浏览量

120231 -

EDA工具

+关注

关注

4文章

267浏览量

31787 -

RTL

+关注

关注

1文章

385浏览量

59761 -

数字电路

+关注

关注

193文章

1605浏览量

80580 -

门级电路

+关注

关注

0文章

15浏览量

1957

原文标题:科普 | 浅谈芯片数字后仿的那些事

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字后端设计工程师主要干什么?

为什么使用XceliummAIn18进行数字后仿会发生故障?

数字后端设计流程

数字后端关于Litho Grid基本概念介绍详解

介绍数字后端概念--Shape Blockage

数字后端基本概念介绍

浅谈数字后端工程师的工作

数字后端基本概念介绍—FinFET Grid

基于超表面天线阵列的射频前端与数字后端联合抗干扰方案

什么是数字后仿?浅谈芯片数字后仿的那些事

什么是数字后仿?浅谈芯片数字后仿的那些事

评论