近年来,处理器性能越来越强,无论是通用处理器还是嵌入式处理器,都进入了多核处理器时代,多核处理器中,每个核心不能独立工作,需要协同工作才能充分发挥处理器的性能,也就是需要高效的核间通信(Inter-processor Communication)机制。核间通信的主要目标是,充分利用硬件提供的机制,实现高效的核间通信,从而充分发挥Soc的整体性能。

核间通信(IPC)方案简介

TI J7 DRA8xx/TDA4xx、AM65xx、J6家族的处理器,基于异构、可扩展的架构开发,拿TDA4VM的处理器来说,该处理器包含了TI DSP处理器(C66/C7x)、Cortex A72、Main域Cortex R5F、MCU域Cortex R5F、深度学习加速器MMA、图形处理器GPU等核,属于多核异构的架构。Cortex A72可用于通用计算、图形处理器GPU用于3D图像的加速、DSP可用于算法的加速、C7x/MMA可支持深度学习的处理、Cortex-R5F可用于外设的控制和图像的前后处理等。多核异构的优点是采用适合的核做擅长的事,再加上专用硬件加速器也可处理特定任务,从而在性能、功耗和成本 上达到最佳平衡。

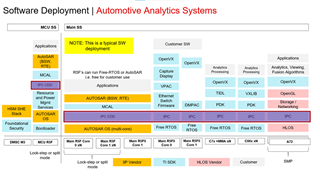

核间通信(IPC)从软件的角度来讲, IPC提供了运行在处理器上的软件接口,可供客户调用,从而实现在多核处理器中核与核之间的通信。举个例子来说,如图1: TI Jacinto7软件框架紫色框模块所示,每个核上都运行了IPC软件模块,从而实现了TDA4VM上不同核之间的核间通信。本文的后续部分将以TDA4VM为例说明TI多核异构处理器的核间通信方案,对于其它Jacinto7处理器、AM65xx、J6 等多核环境中的处理器之间进行通信采用的是同样的方式。

图1 : TI Jacinto7 TDA4VM SW Framework

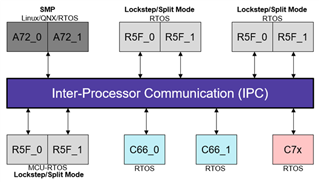

Jacinto7 TDA4VM处理器的核间通信(IPC)框图如图2所示,TDA4VM拥有2*A72、6*R5F、2*C66、C7x等核,不同核之间的通信依赖IPC(Inter-Processor Communication)。同时,同一种类型的多个核心又可以运行在不同的模式,比如A72可以运行的SMP模式,双核R5F可以运行在Lockstep或Split Mode上,因此,核间通信方案要充分利用硬件提供的机制,实现高效的核间通信,从而充分发挥Soc的整体性能。

图2 : TI Jacinto7 TDA4VM IPC Framework

TDA4VM硬件提供了Mailbox硬件模块,Mailbox中断机制允许软件在两核之间建立通信通道,这种机制类似于邮箱工作的方式。每个核都有一个专属的邮箱,邮件就是消息内容,通过指定接收方,就可以将消息传递到指定核。Mailbox硬件上支持中断,因此指定核有消息时,就会收到中断,然后开始处理邮件,即处理消息。这就是Mailbox的工作方式。

TDA4VM的IPC方案,基于Mailbox的实现的方式的不同,常用的核间通信方式有两种。

基于RPMSG的核间通信解决方案,适合小块数据消息传递。

基于Share Memory核间通信解决方案,适合大块数据传输。

基于RPMSG的核间通信解决方案

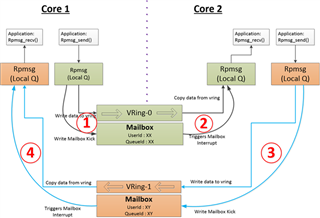

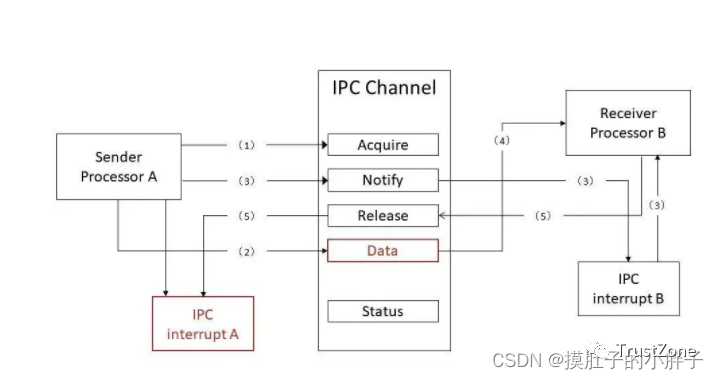

RPMSG定义了通信协议的接口,采用RPMSG协议,基于Mailbox模块的核间通信方案如图3所示,该方案传递消息时,首先需要将消息拷贝到的共享内存中(VRing),然后,利用Mailbox将消息传递到指定核上。

图3: RPMSG的核间通信解决方案

上图中术语和缩写解释如下:

| Term | Definition or Explanation |

|---|---|

| IPC | Inter-Processor Communication |

| MailBox | IP which provides queued interrupt mechanism for communication channel |

| VRing | Ring Buffer in shared memory |

| Rpmsg | queue on local memory |

核间通信步骤如下所述(步骤如红色圈中所示):

发送端发送: Core1核调用Rpmsg_send发送消息,应用程序复制到两个 CORE 之间使用的 VRING。此后,IPC 驱动程序将 VRING ID 发布到硬件指定Mailbox的通道中。

接收端接收:Core2核上Mailbox触发中断,在core2的 ISR 中,它提取 VRING ID,然后根据 VRING ID,检查该 VRING 中的任何消息。

接收端发送: Core2核应用程序调用Rpmsg_send发送消息,应用程序复制到两个 CORE之间使用的 VRING。此后,IPC驱动程序将 VRING ID 发布到硬件Mailbox 的另外一个通道中。

发送端接收: Core1核上Mailbox触发中断,在core1的ISR中,它提取 VRING ID,然后根据 VRING ID,检查该 VRING 中的任何消息。

注意事项:

RPMSG传输消息最大512 Byte。

Performance 参考这里.

基于Share Memory核间通信解决方案

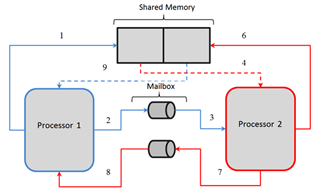

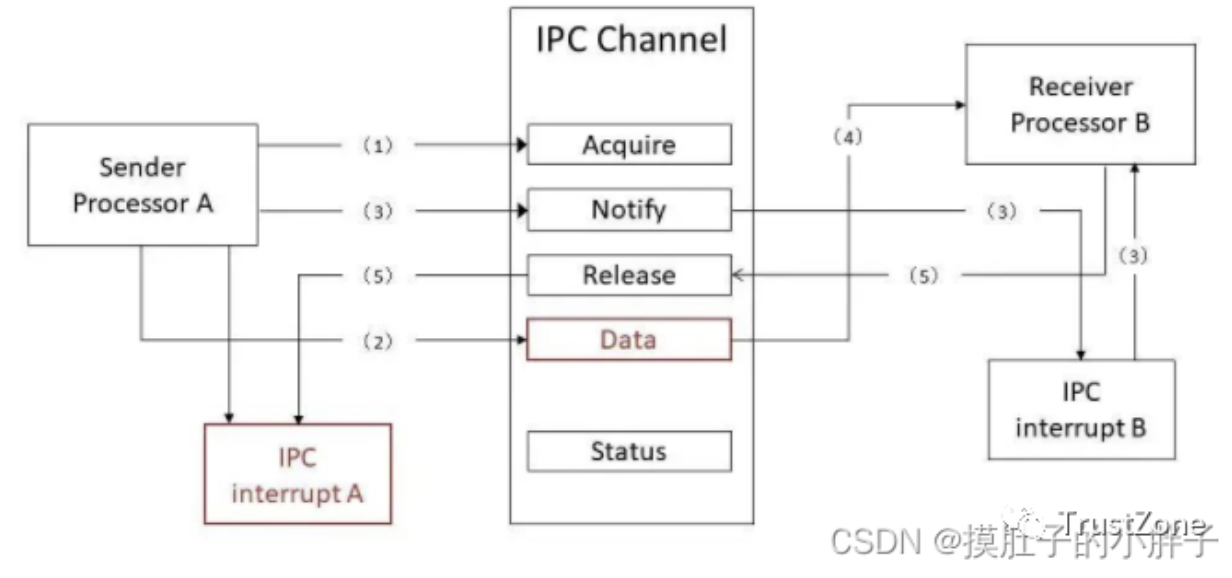

基于Share Memory的核间通信解决方案,底层仍然使用的是硬件的模块Mailbox,如图4所示所示,发送和接受采用的是不同的Mailbox通道。 每一组核与核之间使用的都是指定的Mailbox通道。同时,Share Memory的解决方案需要分配指定Share Memory用以核间通信共享数据。 Share Memory是一段memory 能够被多个核所所访问,所以名为共享内存,在TDA4VM中,这段内存通常是来自于DDR中的一个数据段。共享内存在核间通信方案中,一个核可以将数据写入共享内存,Mailbox可以将内存指针传递到另一个核上,另一个核可以拿到内存指针后,直接从Share Memory读取数据,这一个过程不需要经过数据的拷贝,因此,非常高效,适合大数据量的传输。

图4: 基于Share Memory的核间通信解决方案

核间通信步骤如下所述:

Processor 1: 拷贝数据到Share Memory中的指定位置;

Processor 1:将Share Memory中的指定地址等信息写入Mailbox的指定通道;

Processor 2:接收Mailbox 中断和消息的地址;

Processor 2:从Share Memory中的指定地址读取消息;

Processor 2: 处理接收到的消息,并准备回复消息;

Processor 2:拷贝数据到Share Memory 指定位置;

Processor 2:将Share Memory中的指定地址等信息写入Mailbox的指定通道;

Processor 1:接收Mailbox 中断和消息的地址;

Processor 1:从Share Memory中的指定地址读取消息;

Processor 1:处理接收到的消息。

总结

核间通信广泛应用于TI的多核异构处理器,本文介绍了TI多核异构处理的两种核间通信(IPC)的两种解决方案。基于RPMSG的核间通信解决方案采用了RPMSG协议,广泛应用于Soc内部核之间的消息传递,比如不同核对Camera的控制。适用于消息量小的类型。基于Share Memory核间通信解决方案,由于消息传递过程不需要数据拷贝,数据传输更高效,因此,适用于大块的数据传输,TDA4VM内部图像数据的传输就来自于这种方案。另外,需要注意的时,TDA4VM划分了主域核MCU域,MCU域的软件通常单独开发,对于MCU与其它核的通信采用CDD IPC软件模块,基于Share Memory核间通信解决方案可适用有大数据量传输的需求。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19291浏览量

229904 -

mcu

+关注

关注

146文章

17152浏览量

351260 -

嵌入式

+关注

关注

5083文章

19129浏览量

305400

发布评论请先 登录

相关推荐

SoC的核间通信机制—mailbox介绍

6678 多核导航器 核间通信

关于C6678核间IPC通信的问题

搞定单CPU内双核间的通信和双CPU间的通信

核间通信(IPC)解决方案

非对称双核MCU基础知识及核间通信

Jacinto7 TDA4VM处理器的核间通信解决方案

Jacinto 7核间通信解决方案

Jacinto 7核间通信解决方案

评论