2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自主研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

我们EDA探索频道,今天迎来了第13期的内容——MOSFET Scaling-3D Era,下面就跟着小编一起来开启今天的探索之旅吧~

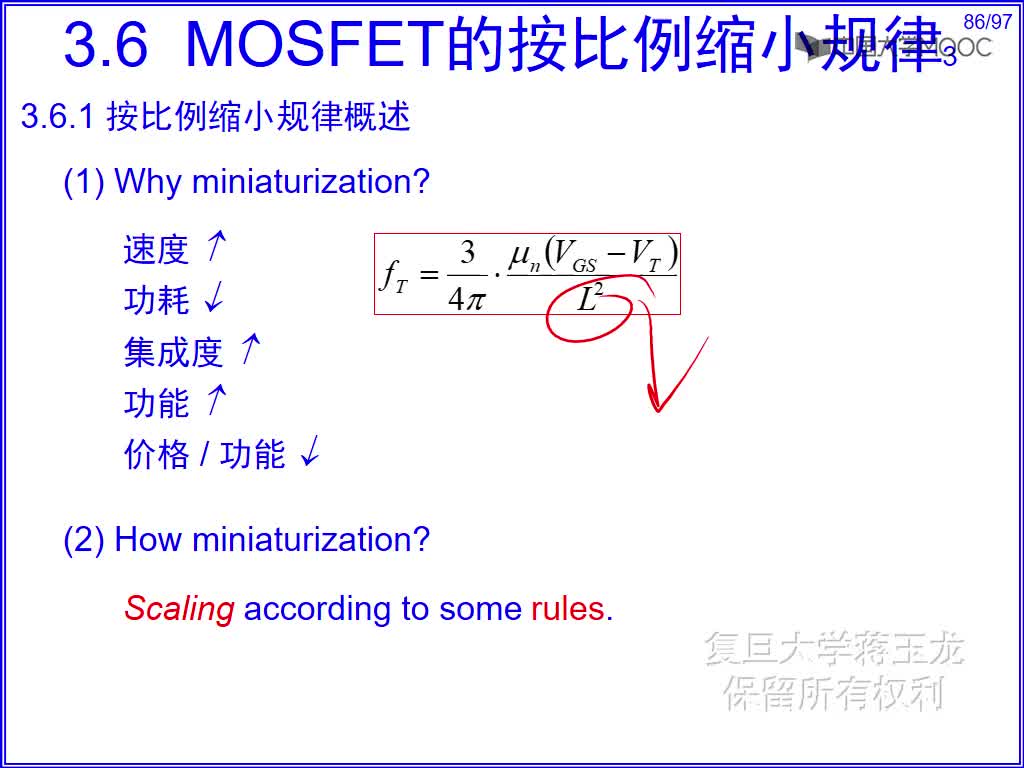

在使用了应力工程和HKMG技术之后,平面MOSFET技术达到了登峰造极的状态。追求MOSFET的微缩需要对器件的结构做出重大的改变。

全耗尽器件

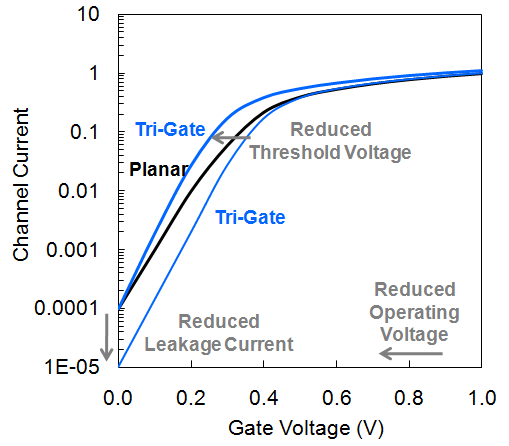

MOSFET性能的基本矛盾点是Ion与Ioff的平衡。粗略地说,提升器件性能或者实现器件微缩有两个基本的路径,即保持漏电基本不变的情况下提升驱动电流和保持驱动电流基本不变的情况下抑制漏电。

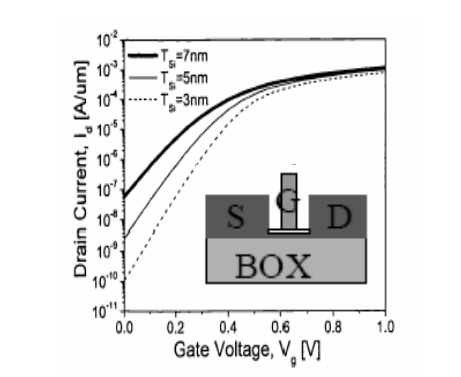

当器件的尺寸越来越小时,漏电的问题会变得越来越明显。回顾我们之前提到的漏电途径,DIBL,源漏穿通等等,都指向于浅结深和隔绝体效应。如果把器件做到只有几十纳米甚至几纳米的厚度,则这些次生的效应都将大大削弱甚至消失,那么漏电流就会极大地被抑制。这便是Ultra-Thin-Body MOSFET(UTBMOSFET)的思路。在这种状态下,沟道在关断时可以达到完全的耗尽状态,所以又可以称为全耗尽器件(Fully Depleted)。

图:UTB-MOSFET示意图。硅的厚度越小,漏电也越小。来自Chenming Hu,Modern Semiconductor Devices for Integrated Circuits

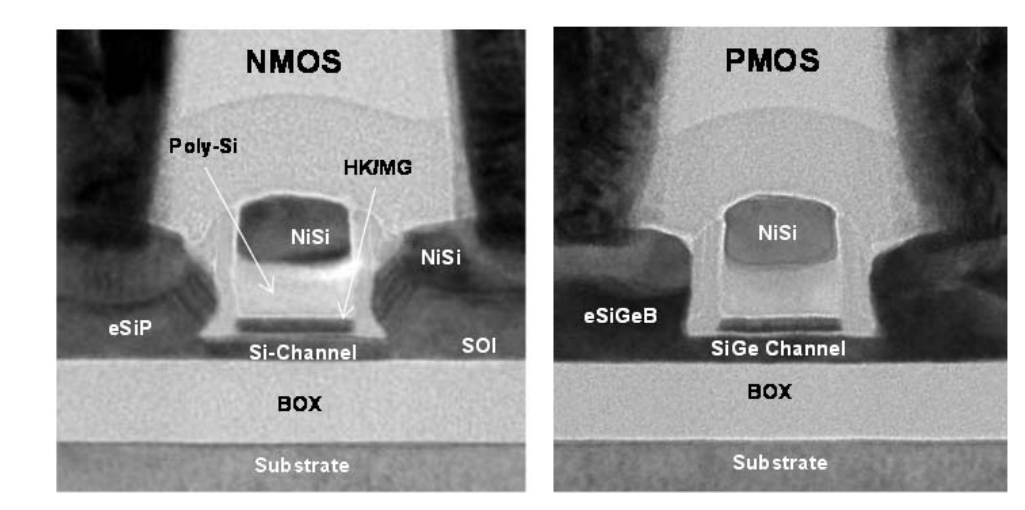

目前主流的实现方式是使用绝缘体上硅(Silicon on Insulator)技术。使用等离子体浸没注入或者晶圆键合技术制造SOI Wafer,在硅下面制造一个氧化硅的埋层,使器件与衬底绝缘。结合器件和制造层面的两个主要特点,可以把这种方式称为FDSOI技术。

图:Global Foundries公开的22nm FDSOI截面照片。来自Carter et al. 22nm FDSOI technology for emerging mobile, Internet-of-Things, and RF applications, IEDM 2016

FDSOI实际上也是一种三维器件的集成技术,如SOI的引入、源漏的外延工程都是在三维上操作的,但是由于后续工艺流程制造方式与传统的平面工艺基本没有区别,所以一般讨论三维器件时并不经常提到FDSOI,而是我们下面要讲的FinFET。

FinFET

FDSOI以较低的成本实现了对漏电流的控制。然而对于驱动电流的提升却贡献寥寥。目前主要用于一些低功耗的场合。而对于高性能计算芯片的微缩,还是要靠FinFET实现,无论是大电流还是小漏电。

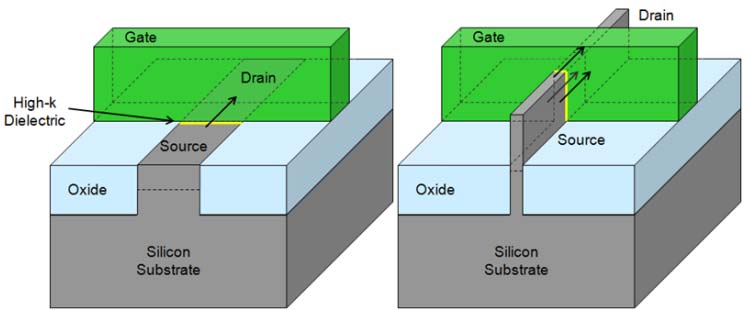

Intel把FinFET称为Tri-Gate,即三栅器件(属于多栅器件的一族,包括了双栅,三栅等类型,篇幅限制不再展开)。相比于平面器件,FinFET把沟道立了起来,三面都有栅极包围。这使得栅极对于沟道的控制大大增强。从抑制漏电的角度来看,同样也可实现全耗尽。所以FinFET同时也是一种全耗尽器件。

图:平面器件和FinFET的示意图。来自Mark Bohr,The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era, IEDM 2011

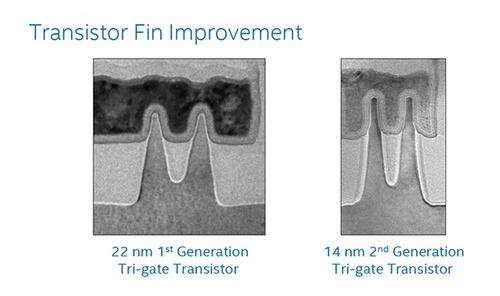

另一方面,FinFET实际上实现了更大的W,即电流的通路,随着器件技术的发展,Fin的高度也越做越高,这样就给电流更大的流过面积。

结合平面时代就有的应力硅技术,HKMG技术等。FinFET把集成电路的电流密度再次带上了一个台阶。

Intel的FinFET截面照片,图片来自

https://www.eetimes.com/intel-ibm-dueling-14nm-finfets/

图:FinFET相比于平面器件性能的提升,能实现更小的漏电或更小的阈值电压。来自Mark Bohr,The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era, IEDM 2011

Intel从22nm技术时代引入了FinFET并沿用至今,代工厂在16/14nm引入了FinFET技术,并且正是在FinFET技术上,台积电对Intel实现了技术反超。未来台积即将量产的“3nm”技术仍是基于FinFET的基础器件设计。然而也正是到了这个节点,FinFET能提供的性能也到了发展的极限。三星对外宣称的”3nm”技术已经采用了名义上更先进的技术。这就是我们下一期要讨论的内容了。

审核编辑 :李倩

-

MOSFET

+关注

关注

148文章

7813浏览量

217201 -

晶圆

+关注

关注

52文章

5076浏览量

128977 -

eda

+关注

关注

71文章

2850浏览量

175657

原文标题:EDA探索丨第13期:MOSFET Scaling-3D Era

文章出处:【微信号:hzwtech,微信公众号:鸿之微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EDA简介(Eng)

FFTC问题求解答!!!动态scaling

探索性数据分析(EDA)及其应用

探索如何打开我国3D打印的应用之路

ERA-3SM+宽带放大器的数据手册免费下载

3D IC先进封装对EDA的挑战及如何应对

EDA探索之MOSFET收缩,Happy Scaling Era

EDA探索之MOSFET的微缩-nanosheet era

EDA探索之MOSFET的微缩- Moore’s Law介绍

在立创EDA中建立器件的3D模型

EDA探索:MOSFET Scaling-3D Era

EDA探索:MOSFET Scaling-3D Era

评论