触发器

利用一个称为“时钟”的特殊定时控制信号去限制存储单元状态的改变时间,具有这种特点的存储单元电路称为触发器。

主从触发器

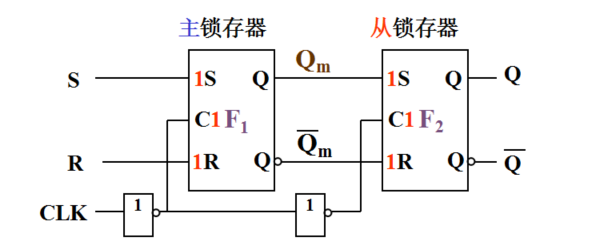

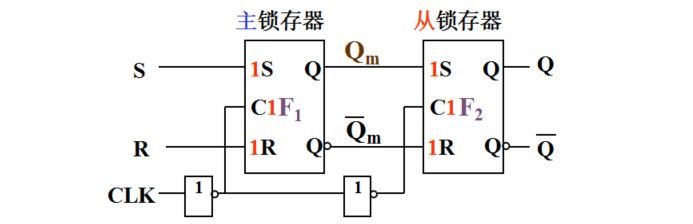

1. 主从RS 触发器

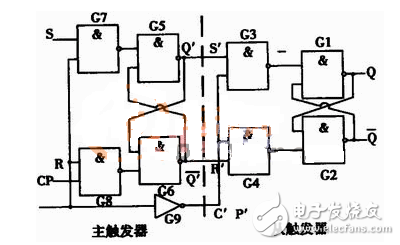

(1)主从 RS 触发器的电路结构

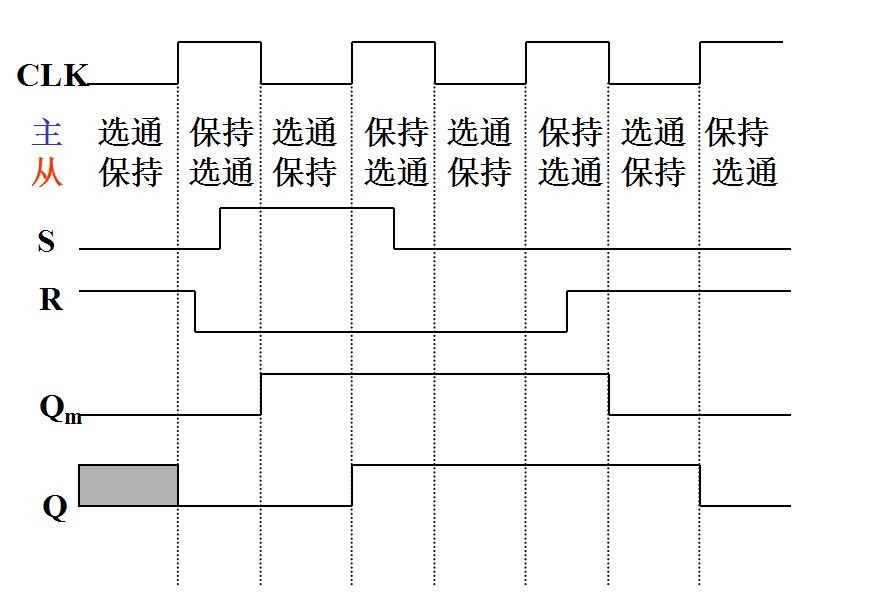

(2)主从 RS 触发器的工作原理

1)在CP=0时,主锁存器F1的控制门打开,处于工作状态,主锁存器按S、R的值改变中间状态Qm;从锁存器F2的控制门关闭,处于保持状态;

2) 在CP=1时,主锁存器F1的控制门关闭,进入保持状态;从锁存器F2的控制门打开,处于工作状态,电路根据Qm的状态改变输出状态;

主从 RS 触发器的电路特点:

1)CLK脉冲不论在低电平或高电平期间,电路的输出状态最多只改变一次;(常把控制信号有效期间,输出状态发生多次变化的现象称为空翻)

2) 将主从RS触发器用于时序电路中,不会因不稳定而产生振荡.

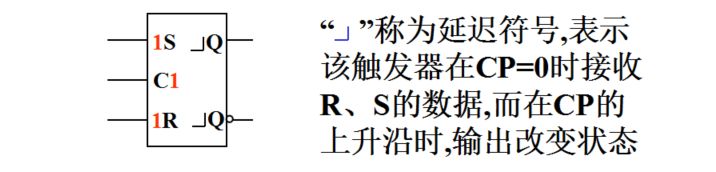

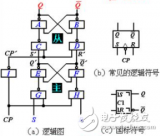

主从 RS 触发器的电路符号:

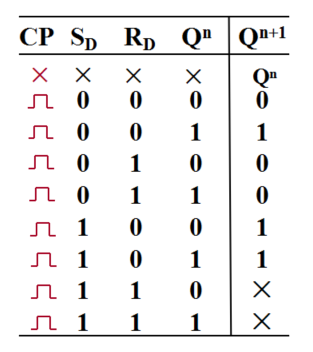

(3)主从 RS 触发器的逻辑功能描述

1)主从RS触发器的特性表

主从RS触发器的特性表和特性方程和RS锁存器基本相同,只是在列特性表时,要加上CP脉冲标志.

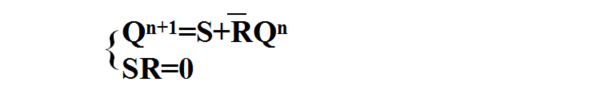

2)主从RS触发器的特性方程

3) 主从RS 触发器的定时波形

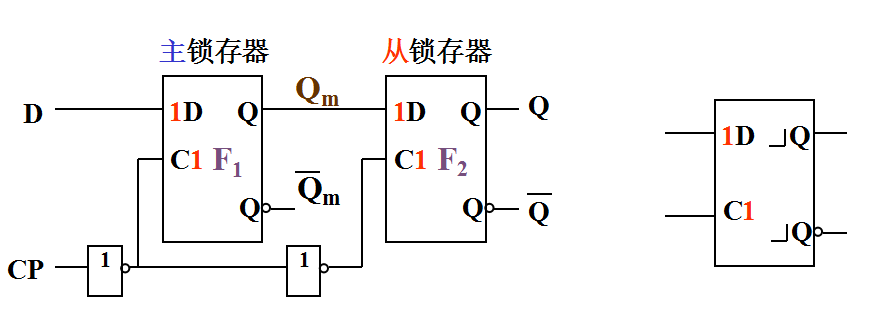

2. 主从D 触发器

工作原理:

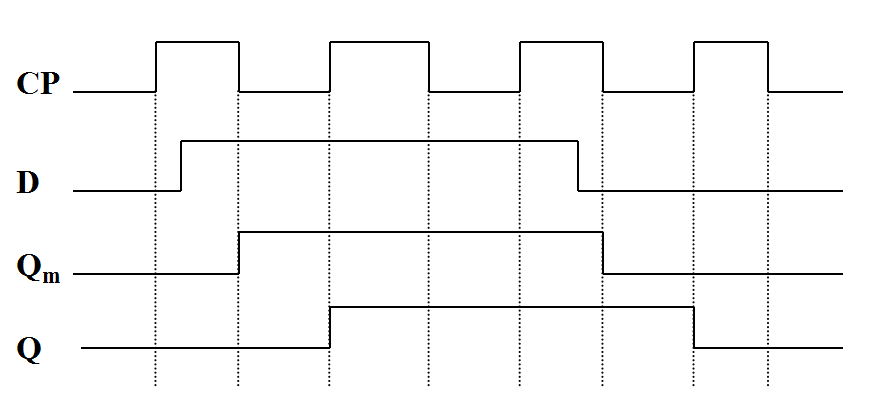

(1) 当CP=0时,主锁存器被选通,Qm=D, 从锁存器保持原态;

(2) 当CP=1时,主锁存器保持原态, 从锁存器被选通,Q=Qm;

特性方程:Q^n+1=D

定时波形图

3. 主从JK 触发器

为去除主从RS触发器的约束条件:RS=0,设计出主从JK触发器.

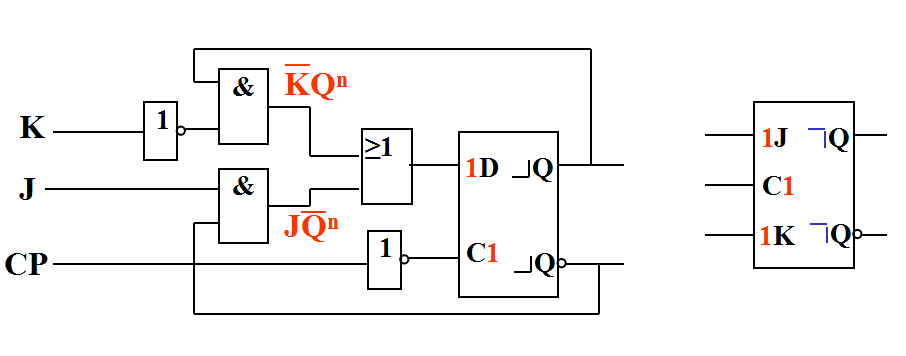

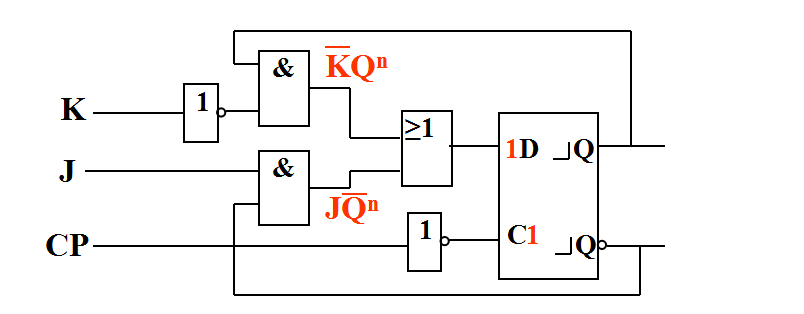

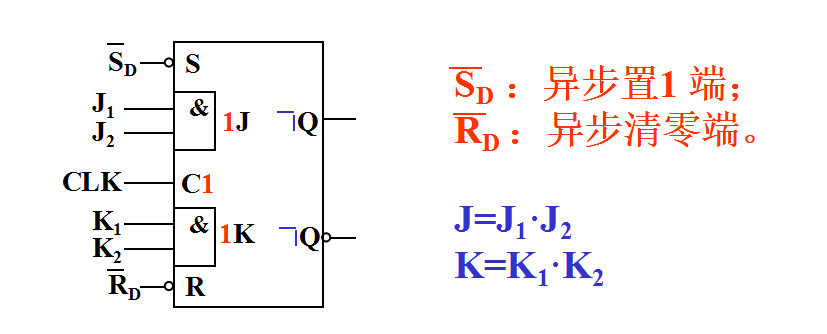

(1)主从JK触发器的一种结构和逻辑符号

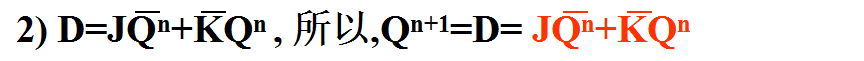

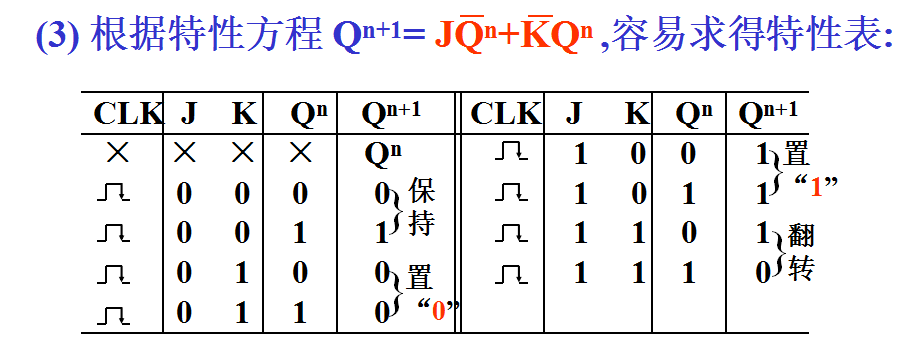

(2)主从JK触发器的特点

1) 电路以D触发器为核心,故不存在约束条件;

3) 由电路可见,CP是经一个非门送入D触发器,所以这种结构的JK触发器为CP下降沿到达时改变状态.

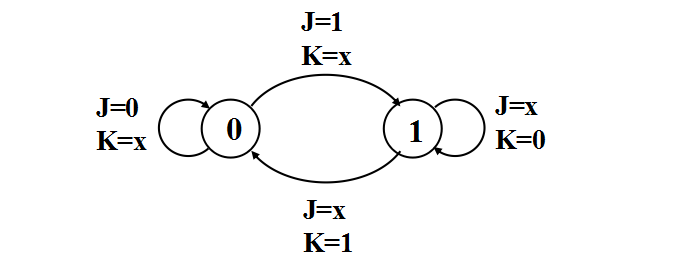

(4) 状态图

(5) 带异步清零、置1端并具有多驱动输入的JK触发器。

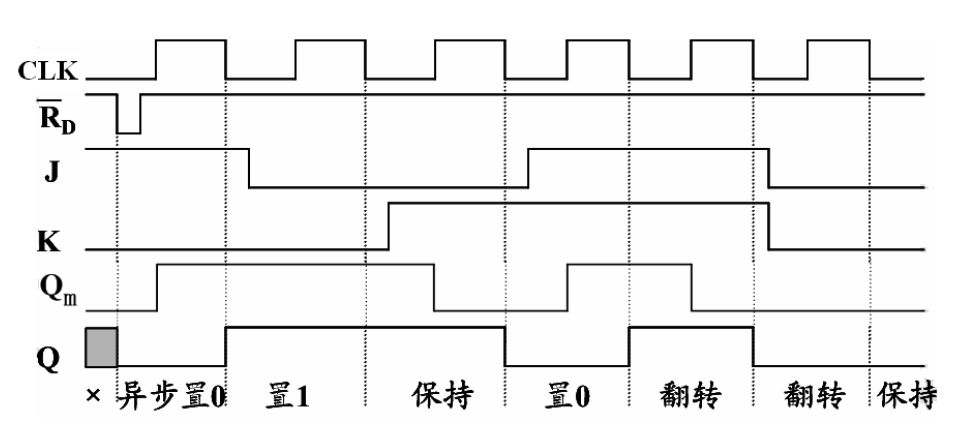

(6) 主从JK触发器定时波形

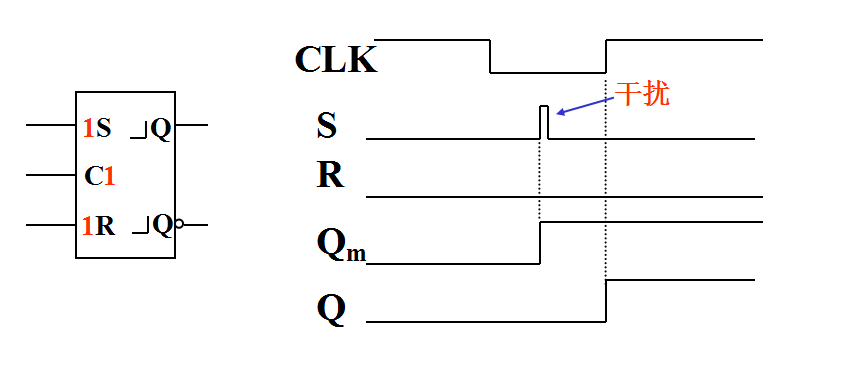

4. 主从触发器的缺陷

主从触发器抗干扰能力不强

上升沿翻转的主从RS触发器

-

RS

+关注

关注

3文章

140浏览量

111551 -

存储单元

+关注

关注

1文章

68浏览量

16801 -

主从触发器

+关注

关注

0文章

13浏览量

6647 -

触发器

+关注

关注

14文章

2065浏览量

63560 -

电路结构

+关注

关注

1文章

38浏览量

9345

发布评论请先 登录

如何用Verilog HDL语言描述D型主从触发器模块

主从触发器,主从触发器的原理和特点有哪些?

主从rs触发器波形图介绍

一文详解主从触发器

一文详解主从触发器

评论