来源:《半导体芯科技》杂志

作者:Andrea Kneidinger,EV Group

数据中心、电信网络、传感器和用于人工智能高级计算中的新兴应用,对于低功耗和低延迟的高速数据传输的需求呈现出指数级增长。我们比以往任何时候都更加依赖这些应用来确保这个世界更安全、更高效。在所有这些市场中,硅光子学(SiPh)在实现超高带宽性能方面发挥着关键作用。因此,开发能够经济高效地扩大硅光子产品生产的解决方案比以往任何时候都更加重要。

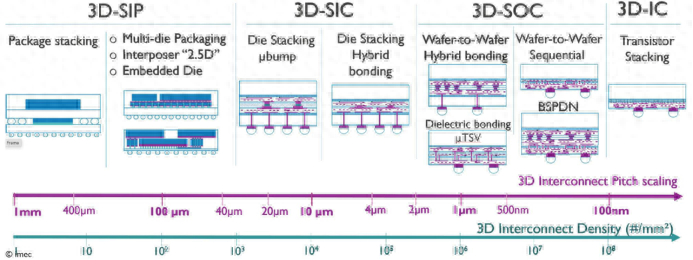

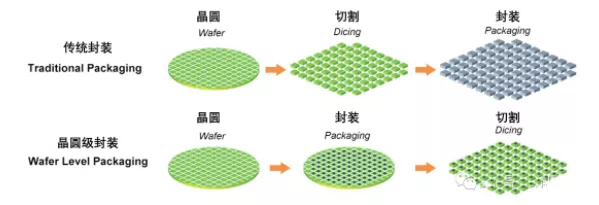

虽然通过使用标准半导体大规模生产工艺和现有基础设施,SiPh的晶圆制造能力已经成熟,但SiPh的封装解决方案仍然是大规模商业化的关键瓶颈。

与晶圆制造相比,SiPh的生产能力仍然落后且缺乏可扩展性。主要的限制因素是光纤到芯片的组装,如今的公司通常依赖于非常复杂的解决方案;例如,通过主动对准或高精度工具在芯片上直接使用粘合剂进行光纤粘合。这些因素限制了SiPh的更广泛部署。为解决这一挑战,EV Group(EVG)与Teramount合作,使用简单、可靠且具有成本效益的晶圆级复制工艺开发光学微结构,从而实现生产能力以及复杂结构生产的规模化。这种被称为纳米压印光刻(NIL)的复制工艺有助于简化、小型化和标准化光学接口,以弥合SiPh封装与晶圆级大批量制造(HVM)之间的差距。

NIL概述

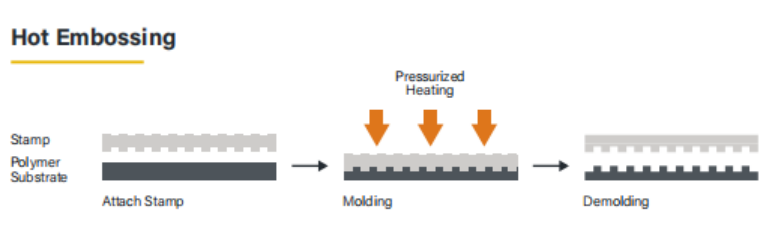

NIL是一种精确的复制技术,已被证明非常适合促进具有挑战性几何形状的微结构的图案化,这是光子市场新兴器件和应用所需的技术。该技术非常灵活,可以生产各种形状和结构,例如反射镜、棱镜、球面和非球面透镜、微透镜阵列,以及各种类型的衍射结构。支持的尺寸结构可以是自由形式的,范围从纳米级分辨率到毫米的横向范围。这些3D结构只需一步即可复制,非常适合光子学行业,其中光物质相互作用在很大程度上依赖于形状和几何尺寸。

NIL的另一个关键特性是将这些复杂和高精度的结构直接转移到HVM中,因为可以在单个工艺步骤中在大面积上以高保真度复制数百或数千个结构。总体而言,晶圆级NIL代表了一种高效且低成本的非常规光刻方法,能够复制复杂的微米级和纳米级结构,尤其是晶圆级光学器件(WLO)。

步进重复母版:将NIL从单个裸片扩展填充到整个母版

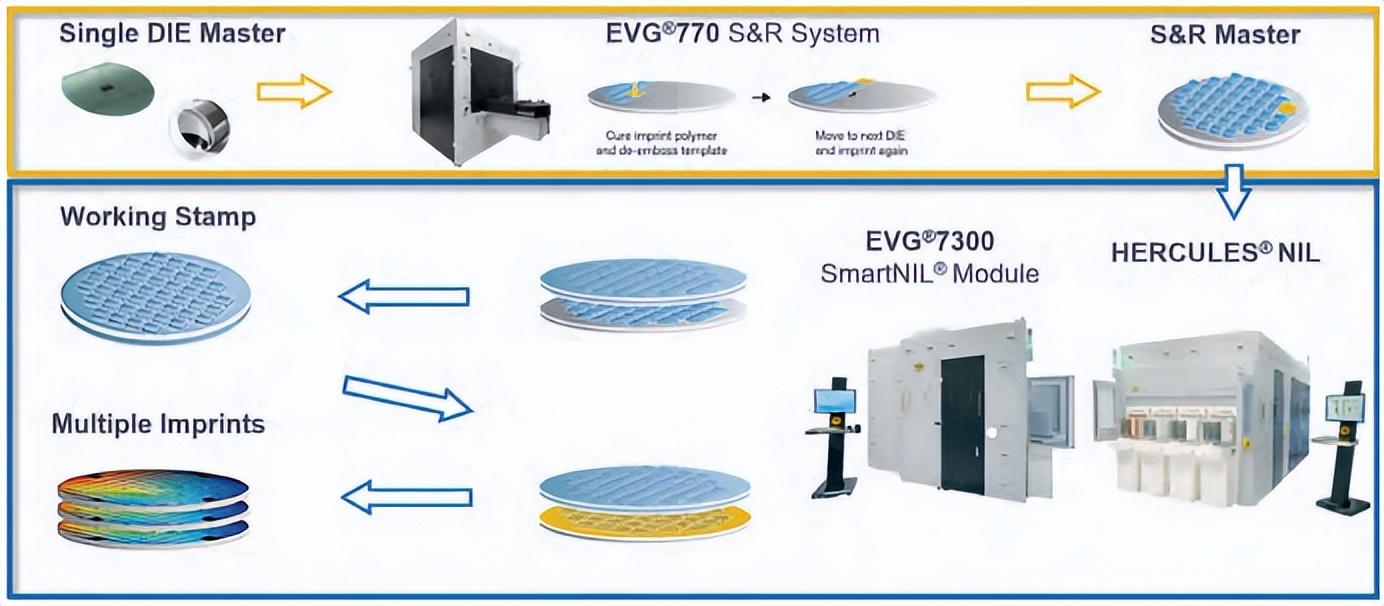

步进重复(S&R)NIL是制造晶圆级微结构或纳米结构的关键使能技术,因为它弥合了芯片级设计和晶圆级生产之间的关键差距。特别是,它允许缩放先前在平方毫米范围内测量的区域上原型化的结构,以填充整个200mm或300mm的晶圆。S&R NIL面临的主要挑战是,初始母版印章的质量决定了后续生产的成功,因此必须保持单个模具母版的质量。因此,单个裸片的母版有必要使用——用电子束、直接激光写入或双光子聚合写入——并精确复制数百甚至数千次,以生产200mm甚至300mm晶圆生产线的全面积母版(见图1)。

△图1:EVG的NIL工艺和扩展技术:从单个芯片,通过分步重复(S&R),到完全填充的母版和大批量制造。

为满足这一需求,EVG开发了EVG770 S&R NIL系统,该系统可以精确复制微米和纳米图案,用于HVM中使用的大面积母版印章制造。它以全自动程序分配光刻胶、对齐结构、相应地压印和脱模。为了支持最先进的母版制作要求,S&R系统包括完整的工艺控制,在250nm内进行精确对准,并且能够将每个结构定位在对准图案旁边。所有工艺步骤——从分配、压印、固化和脱模——也必须在单一环境中精确执行和监控,以实现最佳反馈控制。

这不仅避免了空气中的颗粒或温度变化等外部来源可能导致缺陷的影响,而且还能够创建具有最佳质量的晶圆级母版和每个可以应用的单个芯片的精确复制品到晶圆级制造中。

在每个复制步骤中——从单个芯片到S&R母版,再到工作印章和最终压印——图案尺寸的一些变化是不可避免的,这是由于UV固化过程中交联引起的聚合物收缩。这些变化是可以预测的,一些步骤甚至可以相互补偿,并且对于一组给定的材料,与原始设计的偏差是完全可重复的。因此,可以在主设计中计算补偿。灵活的制造方法,例如2GL(双光子灰度光刻)或电子束,支持此类设计更改以及较短的迭代时间。

用于大批量制造的晶圆级NIL

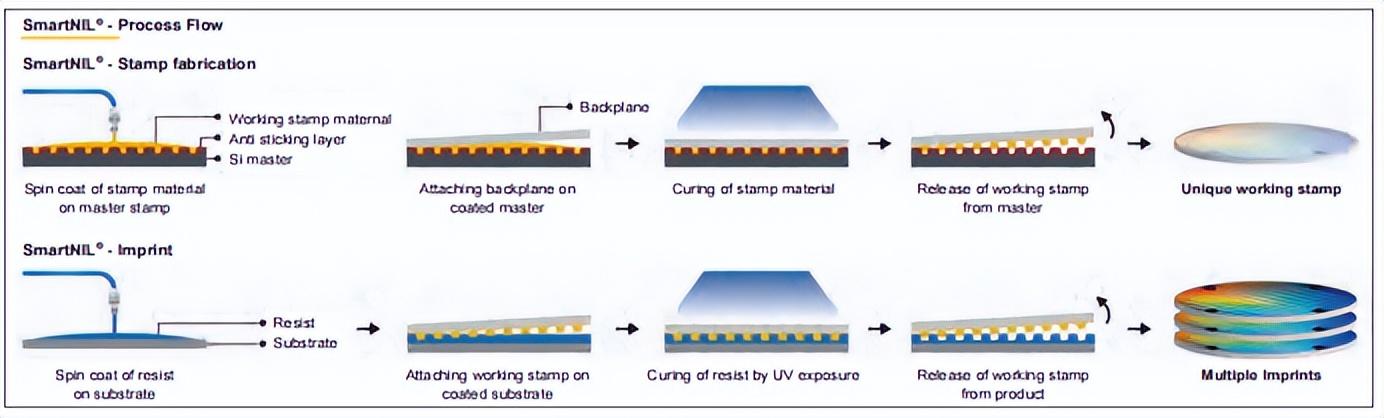

S&R母版制作工艺之后是晶圆级NIL复制,这是在EVG7300上执行的。这个工艺包括两个步骤,这两个步骤都在同一个系统上执行的(图2)。首先,复制S&R母版以制作工作印章。此步骤特别有用,因为它最大限度地减少了昂贵母版的磨损并降低了引入缺陷的风险。有缺陷的工作印章可以快速且低成本地更换,这在大批量生产过程中特别有利。

△图2:NIL工艺的示意图,包括两个步骤:工作印章制作和压印。这两个步骤都是在同一个工具中进行的。

为确保无缺陷的工作印章制造,初始母版上涂有通过旋涂施加的防粘层。接下来,使用EVG120旋涂/喷涂系统通过旋涂工艺将工作印章材料直接涂在母版上。接下来,将透明背板贴在带涂层的母版上。然后使用UV LED光源固化工作印章聚合物,最后从母版上脱模。

制作工作印章后,在器件基板上执行实际压印工艺。这涉及使用与工作印章制造相同的旋涂工艺来在基板上应用专用的材料。

接下来,工作印章和具有分配材料的基板彼此接触。与工作印章制造过程一样,此步骤之后是UV固化和脱模,从而在基板上形成最终器件的多个印章。然后可以将工作印章重复用于多次压印,从而提高NIL工艺效率。这种重用工作印章的方法已经在HVM应用中得到了证实。

NIL工艺早已证明其在光学传感器大批量生产中具有高可重复性,现在正被用于复制硅光子器件封装的复杂光学结构。与金刚石钻孔、激光直写和电子束写入等传统制造方法相比,它为这些结构提供了显著的产量和成本优势,这些方法难以扩展到更大的基板并且其产量有限。结合NIL工艺可以使用性能最佳的芯片,并能够有效地将这些高质量图案带入生产线。特别是,与光子芯片下方光学结构的精确对准,对于SiPh封装器件内所需的出色耦合性能至关重要。NIL还可以生产复杂的结构,这通常不可能通过标准CMOS工艺生产,例如具有锐角、曲面或具有高纵横比和低纵横比的结构的镜子和透镜的光学耦合元件。NIL在SiPh晶圆上提供高图案保真度、可重复性和精确放置光学元件的能力,在将典型的光纤封装复杂性从组装领域转移到晶圆制造领域方面发挥着关键作用。

与Teramount合作

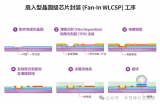

EVG与Teramount的合作展示了NIL如何帮助实现SiPh封装的范式转变。Teramount通过使用NIL实现其PhotonicPlug和PhotonicBump晶圆级光学元件——使光子封装与标准半导体制造和封装工艺保持一致。NIL为硅光子晶圆的后处理提供了一个理想的平台,用于在半导体制造厂或外包半导体组装和测试(OSAT)设施中执行的光子“凸点化”工艺。

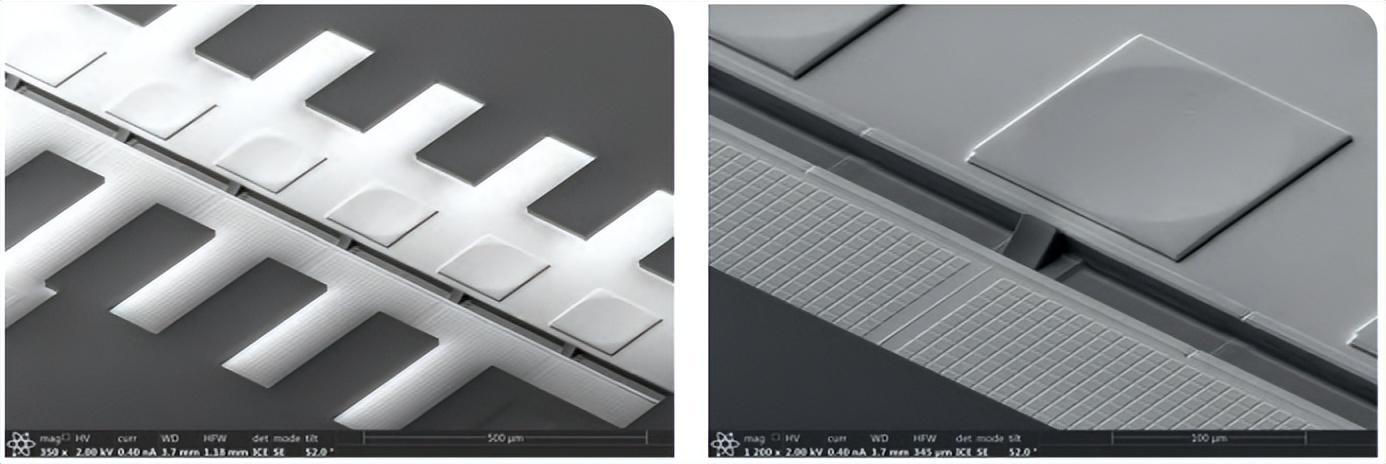

NIL已被用于在8英寸SiPh晶圆上压印光子凸点,用于执行晶圆级光学耦合元件,从光子集成电路的波导和到光子集成电路的波导。图3a显示了压印在多通道SiPh芯片旁边的光子凸点,图3b显示了压印在单个波导通道附近的光子凸点的特写。

△图3:a)SiPh晶圆上多通道光子集成电路波导旁边的光子凸点PhotonicBump NIL压印;b)特写放大图像显示了包括光束偏转镜和光束扩展镜在内的光子凸点PhotonicBump元件。

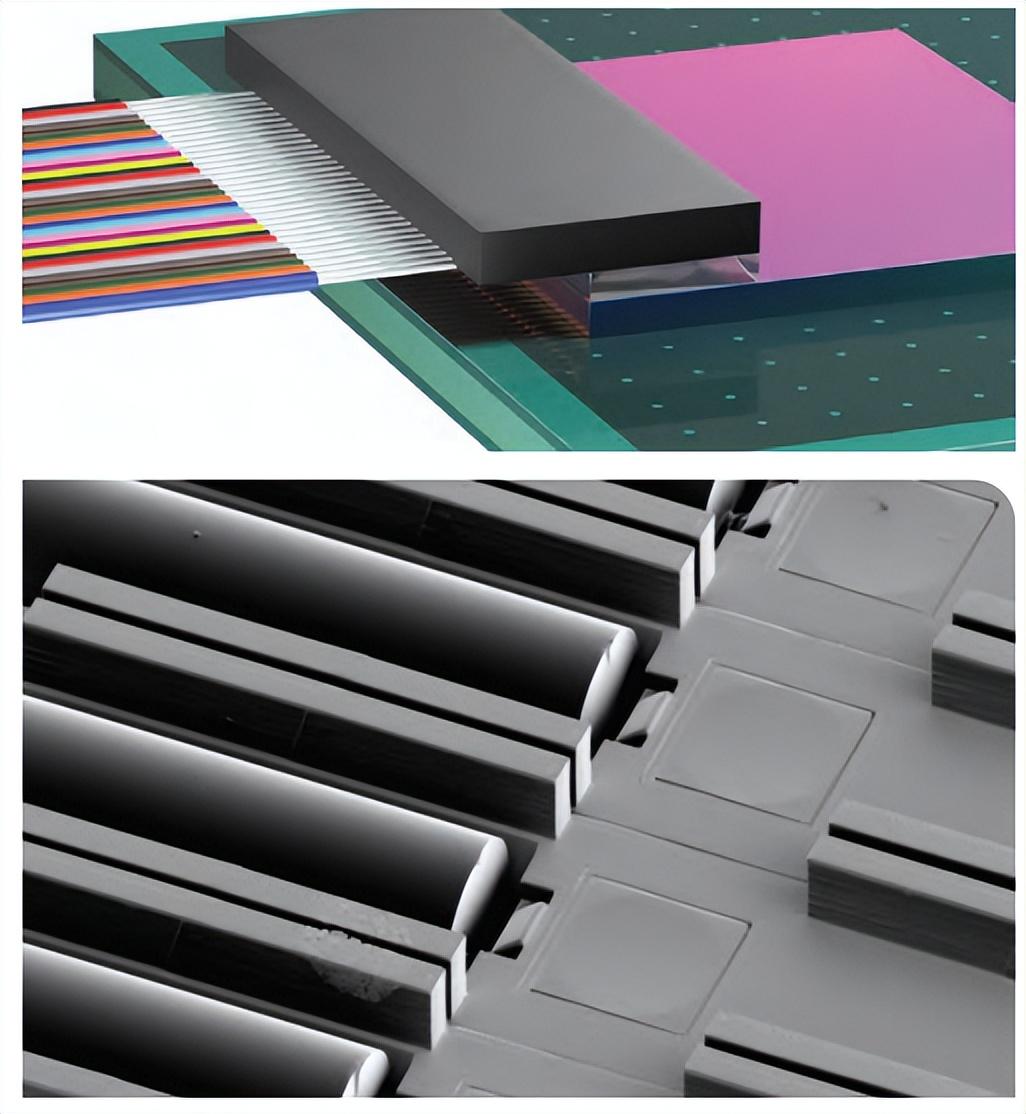

PhotonicBump包含一个压印在深20微米腔内的偏转镜和第二个透镜元件。偏转镜执行垂直光束偏转以实现宽带表面耦合,用来替代通常用于硅光子学封装的复杂侧面耦合几何形状。透镜用于光束扩展,以建立自对准光学方案[1],并在与PhotonicPlug光纤连接器结合时产生较大的装配容差(如图4所示)。

△图4:上)组装在“凸点”SiPh芯片上的PhotonicPlug光纤连接器示意图。下)PhotonicPlug光学元件包括单模光纤、偏转镜和扩束镜。当与PhotonicBump光学器件结合使用时,PhotonicPlug光学器件形成自对准光学方案。

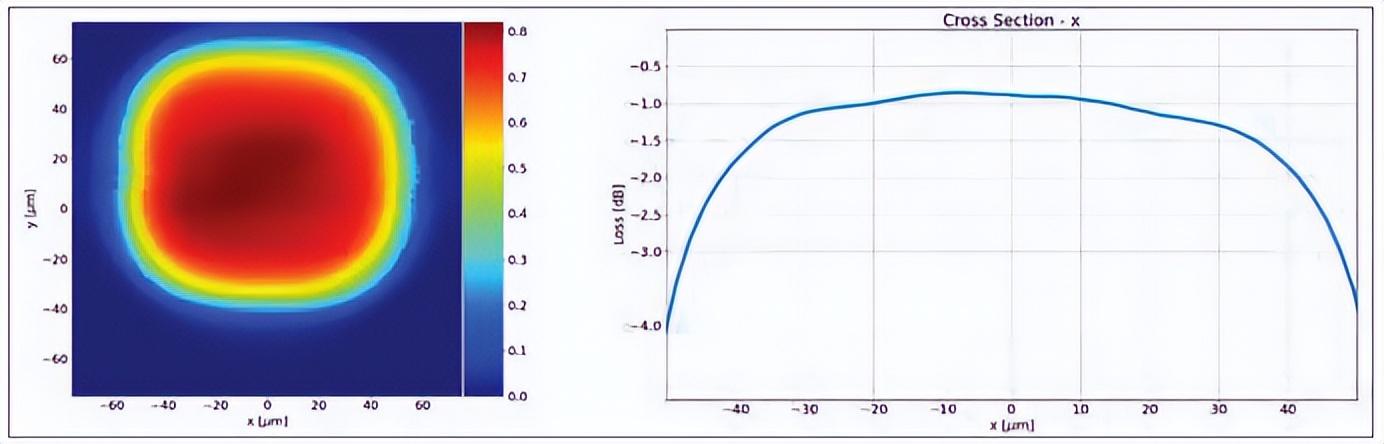

图5显示了与凸点SiPh芯片封装时PhotonicPlug的光耦合性能。图5a显示了XY容差图,图5b显示了具有>±30µm/0.5dB的大装配容差和从光纤到波导的总插入损耗为1dB的x横截面。如此卓越的性能展示了PhotonicPlug和PhotonicBump的能力以及NIL技术执行晶圆级光学元件精确放置的优势。

△图5:a)耦合到SiPh芯片时测得的PhotonicPlug装配容差的XY图。b)PhotonicPlug组件容差的X截面呈现>±30µm/0.5dB,从光纤到波导的总插入损耗为1dB。

NIL与Teramount的PhotonicBump封装技术相结合,使光电子行业的晶圆级封装成为可能,这可能对降低封装和整体产品成本产生深远影响。尽管封装在CMOS总生产成本中所占份额仍然相对较小(但仍在增长),但它占光子制造总成本的大部分,而光子制造仍然依赖于单一器件封装方案。由NIL和PhotonicBump封装实现的晶圆级集成光子学有可能颠覆这种情况。通过NIL工艺和创新光学元件的这种结合,SiPh封装的瓶颈正在转移到光学设计而不是光纤组装容差。

NILPhotonics能力中心:灵活的合作模式

作为EVG与Teramount联合合作的一部分,EVG通过其NILPhotonics能力中心提供NIL工艺开发和原型设计服务,以及CMOS和光子制造方面的专业知识,以协助Teramount加速其PhotonicPlug技术的开发和产品化。

EVG的NILPhotonics能力中心为整个NIL供应链中的客户和合作伙伴提供开放式创新孵化器,以协作缩短创新光子器件和应用的开发周期和上市时间。

该中心高度灵活,能够适应客户的不同需求,同时确保为开发的各个方面提供最高水平的知识产权保护。无尘室旨在满足最严格的客户要求,并允许采用虚拟生产线概念,将晶圆重新引入客户晶圆厂进行进一步的工艺过程。

致谢

作者感谢Teramount的Hesham Taha为撰写本文所提供的帮助。

参考文献

1. “Photonic plug for scalable silicon photonics packaging”, A. Israel et al. Proc.SPIE 11286,Optical Interconnects XX,1128607(28 February 2020);doi:10.1117/12.2543490

线上会议

NI专题讲座,免费学习课件:《如何助力克服无线通讯测试挑战》,报告将详解无线通讯测试挑战、测试方法上的对策、最新射频仪器选择。欢迎点击链接:

http://apply.actintl.net/entry/sisc/20230228

苏州会议

雅时国际(ACT International)将于2023年5月,在苏州组织举办主题为“2023-半导体先进技术创新发展和机遇大会”。会议包括两个专题:半导体制造与封装、化合物半导体先进技术及应用。分别以“CHIP China晶芯研讨会”和“化合物半导体先进技术及应用大会”两场论坛的形式同时进行。详情点击链接查看:https://w.lwc.cn/s/7jmaMn

审核编辑黄宇

-

芯片

+关注

关注

454文章

50488浏览量

422234 -

晶圆

+关注

关注

52文章

4856浏览量

127839 -

封装

+关注

关注

126文章

7808浏览量

142766

发布评论请先 登录

相关推荐

用于创新PIC封装的晶圆级纳米压印技术

用于创新PIC封装的晶圆级纳米压印技术

评论