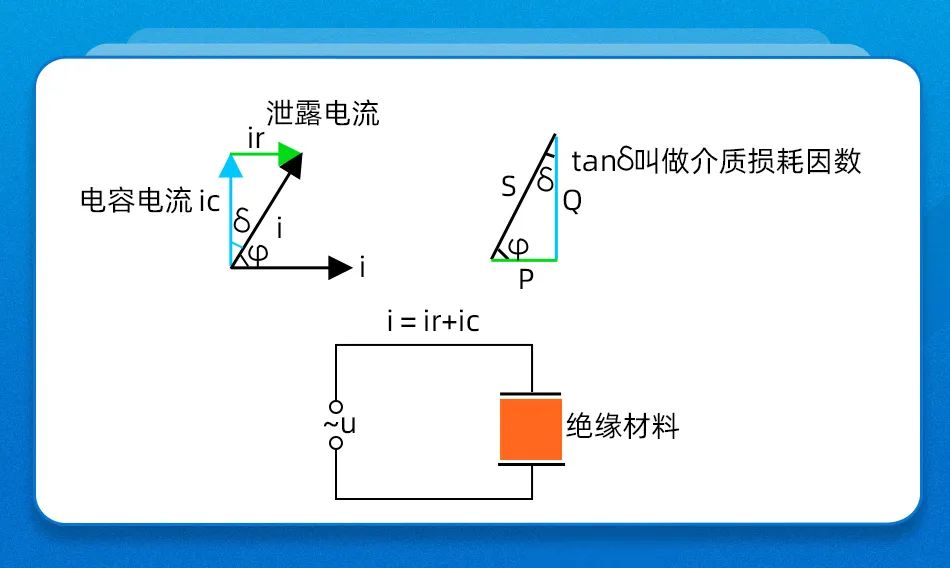

由于T507有漏电保护功能,在T507核心板未上电工作时,如果检测到存在漏电现象则DCDC1就输出异常。在复位重启的时候底板有器件未完全断电会导致核心板的GPIO有漏电,致使核心板存在因漏电保护而无法启动的风险,故需要在底板增加漏电保护电路。

具体实现有以下2个方案:

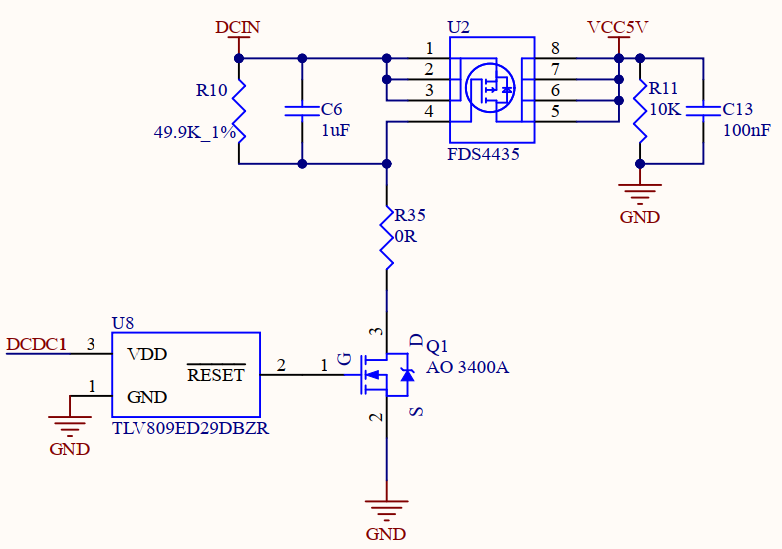

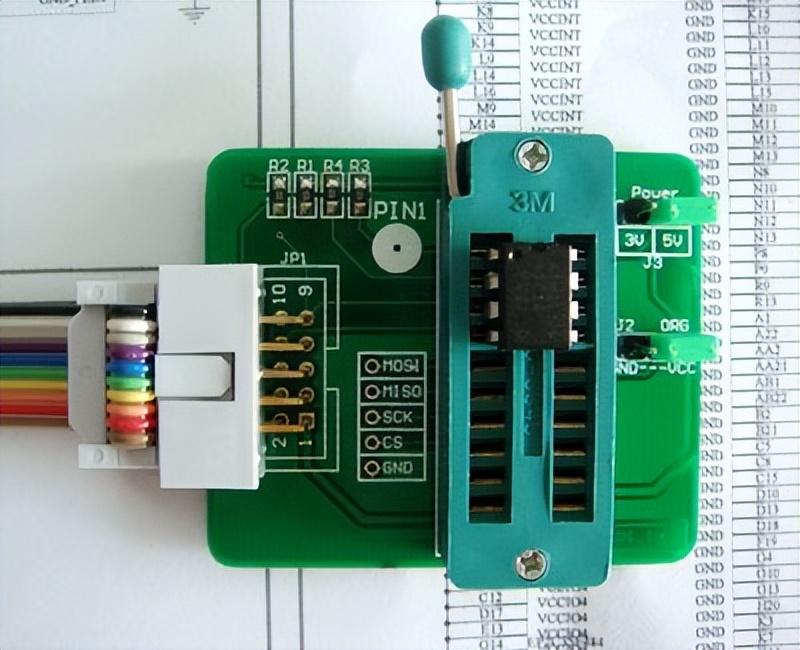

方法1:参考以下电路图,利用TLV809ED29DBZR复位芯片,当出现漏电时,DCDC1输出的电压不足3V,所以TLV809ED29DBZR的2引脚会输出低电平导致Q1关闭,FDS4435因为4引脚电平为高,所以FDS4435管子关闭不输出电压而达到断电的目的,如图下图所示:

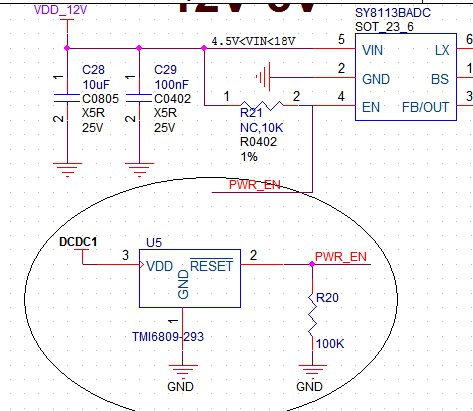

方法2:参考以下图,利用U5复位芯片,当板子出现漏电时,DCDC1输出的电压不足3V,所以U5会输出的低电平将LDO芯片关闭(U5的输出引脚接LDO电源芯片的使能引脚),如图下图所示:

注意,U5的输出引脚需要接下拉电阻R20,且不能低于30K不能大于100K,不然会导致板子无法实现漏电保护功能。

审核编辑黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

456文章

50910浏览量

424512 -

控制板

+关注

关注

5文章

254浏览量

31224 -

漏电保护

+关注

关注

1文章

99浏览量

17172

发布评论请先 登录

相关推荐

全志T507-H国产平台Ubuntu系统正式发布,让您的应用开发更便捷!

本文通过创龙科技TLT507-EVM工业评估板(基于全志T507-H)的硬件平台进行演示。为了简化描述,本文仅摘录部分内容。使用Type-C线将TLT507-EVM评估板的

发表于 10-29 09:39

数字电源的低压调试和高压调试

数字电源的低压调试和高压调试是电力系统中非常关键的部分,它们直接关系到设备的稳定运行和电能供应的质量。以下是对这两种调试方法的详细解析:

实测14us,Linux-RT实时性能及开发案例分享—基于全志T507-H国产平台

本帖最后由 Tronlong创龙科技 于 2024-7-26 08:55 编辑

本文带来的是基于全志T507-H(硬件平台:创龙科技TLT507-EVM评估板),Linux-RT内核的硬

发表于 07-25 15:58

基于全志T507-H的Linux-RT + Igh EtherCAT主站案例分享

的延迟。基于全志T507-H(硬件平台:创龙科技TLT507-EVM评估板),按照创龙科技提供的案例用户手册进行操作,使用Cyclictest程序测试系统实时性,得出如下测试结果。图1

发表于 07-17 11:18

国产!全志科技T507-H工业核心板( 4核ARM Cortex-A5)规格书

核心板斜视图 图 4 核心板侧视图

2 典型应用领域

工业控制

工业网关

能源电力

轨道交通

仪器仪表

3 软硬件参数

硬件框图

图 5 核心板硬件框图

图 6

发表于 07-12 17:26

基于全志T507-H的Igh EtherCAT主站案例分享

基于全志T507-H的Linux-RT + IgH EtherCAT主站演示

下文主要介绍基于全志T507-H(硬件平台:创龙科技TLT507-EVM评估板)案例,按照创龙科技提供的案

发表于 06-03 09:59

基于全志T507-H的Linux-RT实时性测试案例分享

。Cyclictest反复测量并精确统计线程的实际唤醒时间,以提供有关系统的延迟信息。它可测量由硬件、固件和操作系统引起的实时系统的延迟。

基于全志T507-H(硬件平台:创龙科技TLT507

发表于 06-03 09:50

芯海通用 MCU 应用笔记: CS32F03x 系列硬件设计指南

本技术说明文档提供关于 CS32F03x 系列 MCU 的电源,启动引导配置,应用注意事项的说明,旨在帮助用户更好地使用 CS32F03x 系列 MCU,进行芯海科技 CS32F03x 系列 MCU 应用产品的设计、开发和调试。*附件:应用

发表于 05-16 11:32

实测14us,Linux-RT实时性能及开发案例分享—基于全志T507-H国产平台

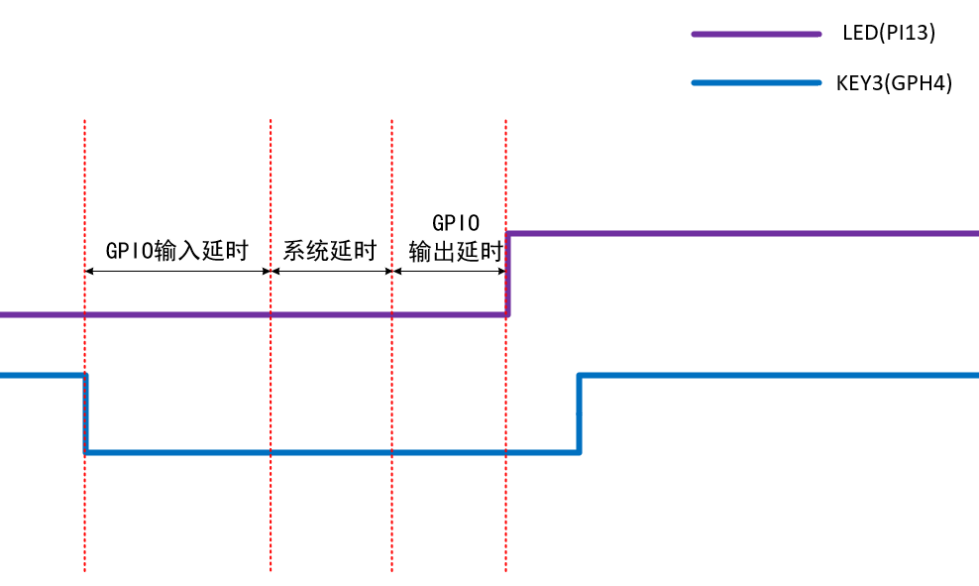

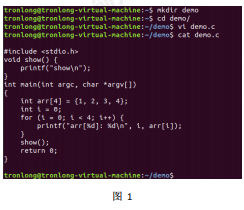

本文带来的是基于全志T507-H(硬件平台:创龙科技TLT507-EVM评估板),Linux-RT内核的硬件GPIO输入和输出实时性测试及应用开发案例的分享。本次演示的开发环境如下:

发表于 04-18 10:21

实测14us,Linux-RT实时性能及开发案例分享—基于全志T507-H国产平台

本文带来的是基于全志T507-H(硬件平台:创龙科技TLT507-EVM评估板),Linux-RT内核的硬件GPIO输入和输出实时性测试及应用开发案例的分享。本次演示的开发环境如下:

Android发布,全志T507四核A53@1.4GHz工业平台,含税仅168元起!

近年来,Android系统在工业自动化、仪器仪表、医疗、安防等工业领域的使用日趋广泛。为了满足广大工业用户的需求,创龙科技针对全志T507-H工业平台进行了Android系统适配。 创龙科技

开关电源调试内容与四大调试方法分享

开关电源调试是指根据设计的输入输出规格对其电器性能、保护功能等进行调试。调试开关电源主要调试低压高压工作状态、输出电压是否稳定、带载能力等。

硬件调试笔记--T507电源防漏电设计

硬件调试笔记--T507电源防漏电设计

评论