引言

这些高选择性蚀刻工具能够在不损坏设备其他部分的情况下沿任何方向(各向同性)去除材料。在某些情况下,高选择性蚀刻工具还可以在一个方向(各向异性)去除材料。今天,一些现有的蚀刻工具可以在一定程度上执行选择性蚀刻,但它们在这方面的能力有限,无法在高级节点上创建新的器件结构。

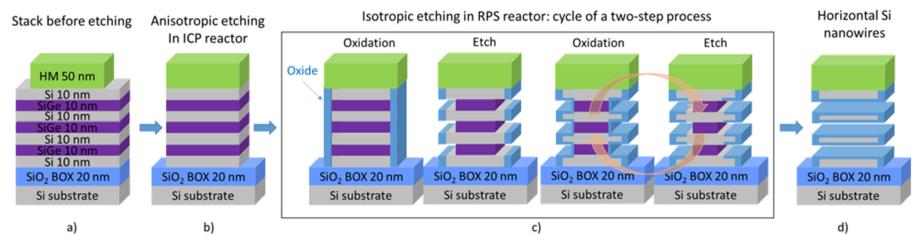

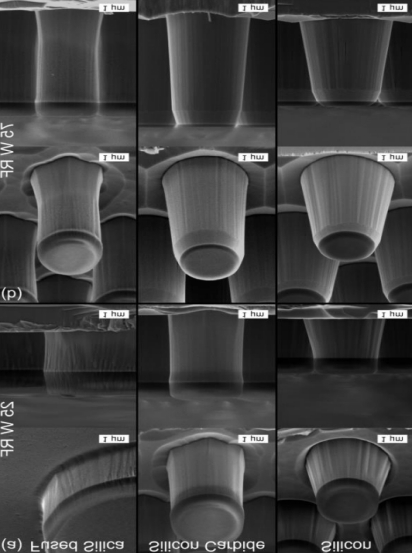

图 1:从 finFET 到 GAA 的过渡推动了关键的各向同性选择性蚀刻要求

蚀刻是晶圆厂中必不可少的工艺。在一个简单的工艺流程中,系统将二氧化硅材料沉积在晶圆上。然后光刻系统在晶圆上每个芯片的材料上绘制微小特征,蚀刻工具去除每个芯片上不需要的材料以创建各种结构,目标是埃级精度(1Å = 0.1nm)。(江苏英思特半导体科技有限公司)

基本上,先进的蚀刻工具是带有腔室的独立系统。在操作中,晶片被插入腔室中。在一种类型的蚀刻中,等离子体——一种电离气体——在腔室中产生。“首先,我们制造等离子体。电子撞击气体分子,这会产生离子和更多的电子。它们还会产生自由基。自由基成为在等离子蚀刻系统中执行化学蚀刻的物质。这些自由基扩散到晶圆表面。它可能会与一种材料发生反应,但不会与另一种材料发生反应。最后,你有一个蚀刻。结果是各向同性过程。 如果化学成分合适,它可以具有很高的选择性。基本上,自由基是一个原子、分子或离子。并非所有芯片工艺都需要高选择性蚀刻。在芯片生产中,许多蚀刻步骤都很简单,并且使用现有的蚀刻工具。对于要求更高的芯片工艺,蚀刻供应商提供了涉及更复杂工具的各种选项。高选择性蚀刻就是这样一种选择。使用专有的化学物质,具有这些功能的蚀刻工具可以去除目标材料,而无需修改或去除周围的层。(江苏英思特半导体科技有限公司)

蚀刻模式

在 IC 行业的早期,芯片制造商自己制造设备。在那些日子里,蚀刻工艺是在通风罩下的水槽中进行的。基本上,将晶圆浸入装满化学蚀刻剂的水槽中,然后进行冲洗。这去除了晶圆上的材料。

早期,蚀刻技术演变为两个部分——湿法蚀刻和干法蚀刻。在一个系统中,湿法蚀刻通过将晶圆浸没在液体溶液中来去除材料。

干法蚀刻是两个市场中较大的一个,广泛用于当今芯片的生产。干法蚀刻分为三个部分或模式——等离子蚀刻、反应离子蚀刻 (RIE) 和溅射蚀刻(又名离子束蚀刻)。每种模式用于不同的应用。

从技术上讲,选择性蚀刻是一种应用,而不是一个单独的类别。它适合湿法和干法蚀刻类别。在所有情况下,目标都是在晶圆上执行具有良好均匀性的精确蚀刻。

图2:各向同性或多向蚀刻(顶部)与各向异性或定向蚀刻

ALE 与选择性蚀刻

许多高级芯片都需要高度选择性蚀刻。多年来,半导体行业为存储器和逻辑开发了新的复杂设备。从 2011 年开始,一些代工供应商开始提供使用最先进的finFET晶体管的先进工艺。IC 供应商围绕 finFET 开发了芯片。如今,代工客户正在运送采用 16 纳米/14 纳米、7 纳米和 5 纳米工艺节点的 finFET 的芯片。3nm finFET 正在研发中。此外,在 3nm 和/或 2nm,一些代工厂将迁移到环栅,这是比 finFET 功耗更低的更快晶体管。但 GAA FET 也更昂贵且更难制造。

图3:Lam 的 Selis-Prevos 系统在纳米片 FET 和其他工艺中蚀刻 SiGe/Si 堆栈__。__

应用

高选择性蚀刻有多种应用。例如,使用各向异性高选择性蚀刻形成自对准触点。在芯片中,触点是将晶体管与设备中的第一层铜互连连接起来的微小结构。基本上,蚀刻工具修整薄膜或材料以形成所需的结构形状。该工艺可用于 finFET 和 GAA。GAA 中还使用了其他选择性蚀刻工艺。在 3nm 和/或 2nm 工艺节点,领先的代工厂及其客户最终将迁移到称为纳米片 FET的 GAA 晶体管类型。纳米片FET是旋转90度的 finFET,产生水平堆叠的鳍片,每个鳍片之间有垂直栅极材料。每个类似于薄片的鳍都是一个通道。(江苏英思特半导体科技有限公司)

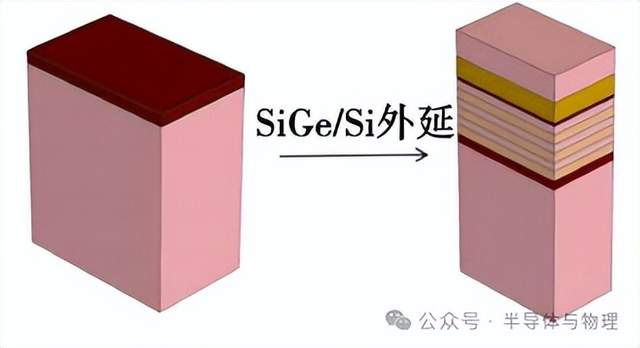

为了在晶圆厂制造纳米片,外延工具在基板上沉积超薄的硅锗 (SiGe) 和硅交替层,形成超晶格结构。这种结构可能具有三层、五层或更多层的每种材料。

在超晶格结构中图案化和蚀刻微小的垂直鳍。然后,形成内间隔物。为此,超晶格结构中 SiGe 层的外部凹陷,然后填充介电材料。接下来,形成源极/漏极。然后,去除超晶格结构中的 SiGe 层,留下构成通道的硅基层或片。最后,通过沉积高k电介质和金属栅极材料形成栅极。每一步都会带来一些挑战,尤其是内部垫片和通道释放过程。(江苏英思特半导体科技有限公司)

审核编辑 黄宇

-

芯片

+关注

关注

458文章

51479浏览量

429288 -

半导体

+关注

关注

335文章

27926浏览量

224868 -

晶圆

+关注

关注

52文章

5015浏览量

128567 -

蚀刻

+关注

关注

9文章

421浏览量

15605

发布评论请先 登录

相关推荐

远程等离子体选择性蚀刻的新途径

高通下一代顶级SoC骁龙855,以打造下一代5G设备

【MPS电源评估板试用申请】下一代接入网的芯片研究

Qualcomm 推出下一代物联网专用蜂窝技术芯片组!精选资料分享

中兴选择Tundra公司PCI Express产品创建下一代

苹果为下一代芯片做技术准备

东芝推出支持下一代内容安全技术SeeQVault™的桥接芯片

SiGe与Si选择性刻蚀技术

为下一代芯片推出高选择性蚀刻

为下一代芯片推出高选择性蚀刻

评论