如今,传统IDM晶圆厂模式越来越不吃香了,新方案不断涌现,高效又环保。

比利时微电子研究中心(imec)展示最新先进IC图形化工艺的环境影响量化评估方案。 imec 藉由在 imec.netzero 模拟平台开发虚拟晶圆厂,利用分析结果,与其伙伴评估现有制程,识别开发重点领域、推算未来数据,并在实体晶圆厂探索高影响力的环境友善制程,包含减少使用含氟的蚀刻气体,致力于极紫外光(EUV) 曝光机的产量最大化,以及减少氢气用量与用水。

imec指出,IC制造衍生的二氧化碳排放量预计在未来10年增长4倍,一来是先进制程技术渐趋复杂,二来晶圆总产量增加; 为逆转未来局势,领先业界的半导体大厂已承诺在2030至2050年前达到碳中和或净零。

有鉴于此,imec启动可持续半导体技术与系统(Sustainable Semiconductor Technologies and Systems)研究计划,广邀半导体供应链以芯片制造的净零碳排为发展目标,其中一项目标是提供业界一套独到的由下而上(bottom-up)设计方法,提供可付诸行动的高度细化资料, 以便在制程与流程开发阶段进行影响评估。

imec.netzero 模拟平台是这项计划的产物,imec 与其伙伴合作,利用该平台首次量化不同逻辑芯片世代的图形化工艺所带来的环境影响;imec 技术研究主任 Emily Gallagher 解释,透过应用虚拟晶圆厂可展示生产 3 nm逻辑晶圆的光刻与蚀刻制程,在范畴 1(自有或自行操作资产的直接碳排)与范畴 2(外购电力的间接碳排) 的碳排占比共达 45%。

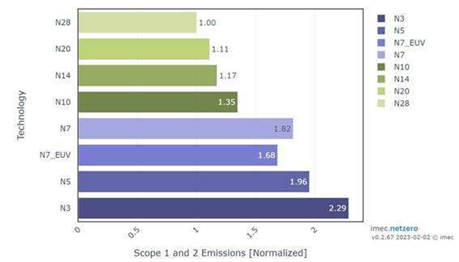

imec.netzero模拟平台针对不同逻辑芯片世代的每片晶圆碳排量进行分析的结果。值得注意的是,7nm制程引进EUV技术,透过精简多道制程步骤,成功减少碳排。

另外,该模拟工具还能在晶圆厂实际操作实验时量化收益,如减少10%的EUV光刻剂量,相当于每片晶圆减少0.4kg的二氧化碳排放量,能为大型晶圆厂省下每月40吨的二氧化碳排放量,等同于美国旧金山与波特兰来回飞行100趟的碳排量。

imec也将自有的实体晶圆厂作为试验环境,从而探索高影响力领域的制程与设计方针。Emily Gallagher表示,我们与爱德华先进科技(Edwards)合作,近期在我们的12英寸晶圆厂无尘室架设了一套EUV蚀刻的氢气回收系统,最多能回收与再利用70%的氢气。

此外,imec也专注在开发数值孔径为0.33与0.55的低剂量EUV蚀刻解决方案,借此降低蚀刻成本,为强化永续发展,也指明蚀刻技术的未来动向,目前焦点放在降低传统蚀刻气体的整体消耗量,未来将携手合作伙伴来量化分析上述解决方案对半导体制程完整流程的影响。

imec先进图形化制程与材料研究计划的研发VP Steven Scheer表示,过去开发的图形化技术是掀起半导体革命的主要成因,为赶上对运算效能不断升级的需求成长幅度,持续改良至关重要。

在 imec.netzero 模拟平台上开发的模型经由设备与材料厂商不断进行基准测试与验证。这些厂商扮演关键要角,除了推行SSTS先导计划,还能强化可行的图形化解决方案,以减少全球半导体业的碳足迹与环境影响。

Steven Scheer 补充,我们注意到碳排当量 (carbon equivalent emissision) 的计算方法并不包含碳排对环境的所有影响。例如,排放气体可能是有害空气污染物(HAPS),而光阻剂与抗反射镀膜(ARC)皆含有全氟与多氟烷基物质(PFAS)。

这些物质的碳氟键结强度提供化学放大阻剂 (chemically amplifiedresist) 优异的光刻特性,包含发展成熟的光学光刻光阻剂与持续发展的 EUV 光阻剂。然而,由于其潜在的生物累积特性,社会因此亟欲禁用 PFAS。除了直接降低碳排,禁用 PFAS 的研究计划也应纳入考虑。

审核编辑 :李倩

-

晶圆厂

+关注

关注

7文章

633浏览量

38078 -

芯片制造

+关注

关注

10文章

645浏览量

29067 -

IC制造

+关注

关注

2文章

32浏览量

16355

原文标题:Imec开发虚拟晶圆厂

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Littelfuse收购Elmos多特蒙德晶圆厂

Imec牵头启动汽车芯粒计划

IMEC组建汽车Chiplet联盟

imec主导汽车Chiplet计划,多家巨头企业加入

什么是虚拟机?什么是虚拟化?

imec实现硅基量子点创纪录低电荷噪声

什么是虚拟机?虚拟机真的那么好用吗?

英特尔以色列晶圆厂扩建计划暂停

阿斯麦和IMEC联合光刻实验室启用

使用OpenUSD和NVIDIA Omniverse开发虚拟工厂解决方案

imec CEO建议台积电分散设厂降低风险

IMEC推出针对N2节点的设计探路PDK

Imec开发虚拟晶圆厂

Imec开发虚拟晶圆厂

评论