如果火车8点开,你住在离车站20分钟的路程,你什么时候“触发”?如果你在7点40分后出发,你就会错过火车。如果你在7:40之前出发,你应该有足够的时间进入车站。(Setup time是20分钟!).

你的朋友需要5分钟帮助搬运行李,你到站后需要待多久?最早是8点05分。没有你5分钟的搬运行李时间,你的朋友就不能上车,你同样会错过火车。(Hold time是5分钟!)

每个触发器在有效时钟边沿都有一个时序范围,在该范围内数据不应该变化。如果数据在期间变化,输出就是不可预测的,这对数字电路来说非常可怕。

现在,我们来看一下时序电路中不同类型的延迟。

**最大逻辑传播延迟:

**

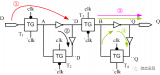

第一个FF输入和输出是D1和Q1,第二个FF的输入和输出是D2和Q2,两个触发器之间有一些逻辑延迟tpd。时钟周期应该满足

Tclock ≥ Tcq + Tpd(max) + Tsetup

**最小逻辑传播延迟:

**

时序电路还需要满足最恶劣情况下的hold要求。

Thold ≤ Tcq + Tpd(min)

**考虑Clock skew的最大逻辑传播延迟:

**

Clock skew是指时钟边沿没有同时到达所有的FFs。

Tskew = Tcapture - Tlaunch

正Clock skew增加了到达右侧FF的时间,可以支持更大的Tpd(max),负Clock skew相反。

Tclock + Tskew = Tcq + Tpd(max) + Tsetup

**考虑Clock skew的最小逻辑传播延迟:

**

正Clock skew增加了到达右侧FF的时间,支持更小的Tpd(max),负Clock skew相反。

Thold +Tskew= tcq + tpd(min)

假设Tcq = 1ns,Thold=0ns,Tsetup=3ns,Tskew =+2ns.Tclock=16ns.

Tpd(min) = Thold + Tskew - Tcq = 0 + 2 - 1 = 1 ns;

Tpd(max) = Tclock + Tskew - Tsetup - Tcq = 16 + 2 - 3 - 1 = 14ns

-

数字电路

+关注

关注

193文章

1608浏览量

80689 -

触发器

+关注

关注

14文章

2000浏览量

61224

发布评论请先 登录

相关推荐

Setup/Hold Time Problem

解释下setup和hold time

什么是Setup和Hold时间

JK触发器,JK触发器是什么意思

施密特触发器,施密特触发器是什么意思

通过解剖一个边沿触发器简要说明setup和hold产生原因

解析触发器的setup、hold、skew属性

解析触发器的setup、hold、skew属性

评论