UVM中类的例化用new和create有什么不同?什么时候可以用new?什么时候该用create?

new是OOP自带属性,create是UVM override属性,可以理解成create比new更进阶~

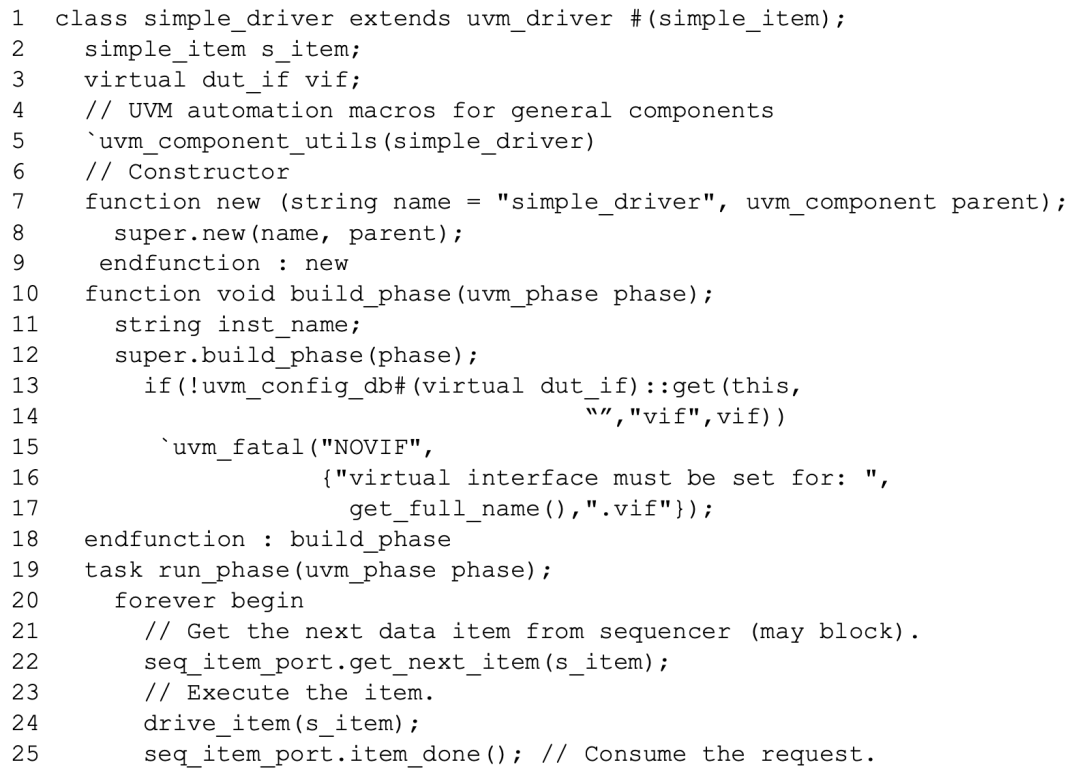

create是用factory模式来construct对象,在factory中注册过的uvm_object扩展类或是uvm_component 扩展类都可以用create,这样做的好处是在testcase里面可以override. new是什么时候都可以用的。

只有与UVM基本类相关的类才可以使用create方法,相当于在UVM这个大树上面挂了个号,具体号码就是通过static function type_id来分配的,UVM的其他地方可以通过号码来对使用create的这个类进行factory机制可以实现的有关功能,override是比较常用的一个功能。

new是一个class创建一个对象的方式,是在运行内存下面挂个号,分配空间,是sv的语法,与UVM无关。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

UVM

+关注

关注

0文章

182浏览量

19283 -

OOP

+关注

关注

0文章

14浏览量

8828

发布评论请先 登录

相关推荐

SystemVerilog中的类构造函数new

在systemverilog中,如果一个类没有显式地声明构造函数(new()),那么编译仿真工具会自动提供一个隐式的new()函数。这个new

发表于 11-16 09:58

•3789次阅读

IC验证"一个简单的UVM验证平台"是如何搭建的(六)

的计算功能,完成scoreboard的比较功能。类中可以有成员变量,这些成员变量可以控制类 的行为,如控制driver的行为等。当要实现一个功能时,首先应该想到的是从UVM的某个

发表于 12-04 15:48

IC验证"UVM验证平台加入factory机制"(六)

平台,因为UVM的特性几乎一 点都没有用到。像上节中my_driver的实例化及drv.main_phase的显式调用,即使不使用UVM,只使用简单的SystemVerilog也可以完 成。本节将会

发表于 12-08 12:07

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

工程师只需要将代码写入适当的phase当中,平台运行时,会按照phase的执行流程来自动执行验证工程师的代码。uvm提供了一系列的基类,验证工程师需要根据实际的情况扩展出合适的类来构建自己的验证平台

发表于 01-21 16:00

什么是uvm?uvm的特点有哪些呢

直观的印象,就是uvm验证平台,它是分层的结构。图中的每一个巨型框都代表着平台的一个构成元素。这些元素呢,我们称为平台组建,下面来简单的分析一下。从最底层上来看,agent 中包含了driver,monitor和sequencer,其中driver ,monitor

发表于 02-14 06:46

请问一下在UVM中的UVMsequences是什么意思啊

在UVM方法学中,UVMsequences 是寿命有限的对象。UVM sequences从uvm_sequence_item基类扩展得到,

发表于 04-11 16:43

深入了解Factory机制的实现方式

。uvm_factory中定义了一系列纯虚函数,主要包括以下几种功能:重载、创建、查找、调试等。这些函数根据参数可以分为基于名字(name-based)和基于类型(type-based)两类接口。也就是说,每一种

发表于 09-16 14:35

谈谈UVM中的uvm_info打印

uvm_report_enabled(xxx)中,会分析传过来的severity和id的配置verbosity要大于传过来的verbosity,(get_report_verbosity_level(severity, id

发表于 03-17 16:41

UVM中seq.start()和default_sequence执行顺序

下src/base/uvm_task_phase.svh文件。为方便分析,我截图如下。在uvm_task_phase类里execute(xxx)函数的第148行和150行确定了seq1和seq2的执行

发表于 04-04 17:15

UVM中uvm_config_db机制背后的大功臣

本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。

UVM中类的例化用new还是create

UVM中类的例化用new还是create

评论