什么是UVM environment?

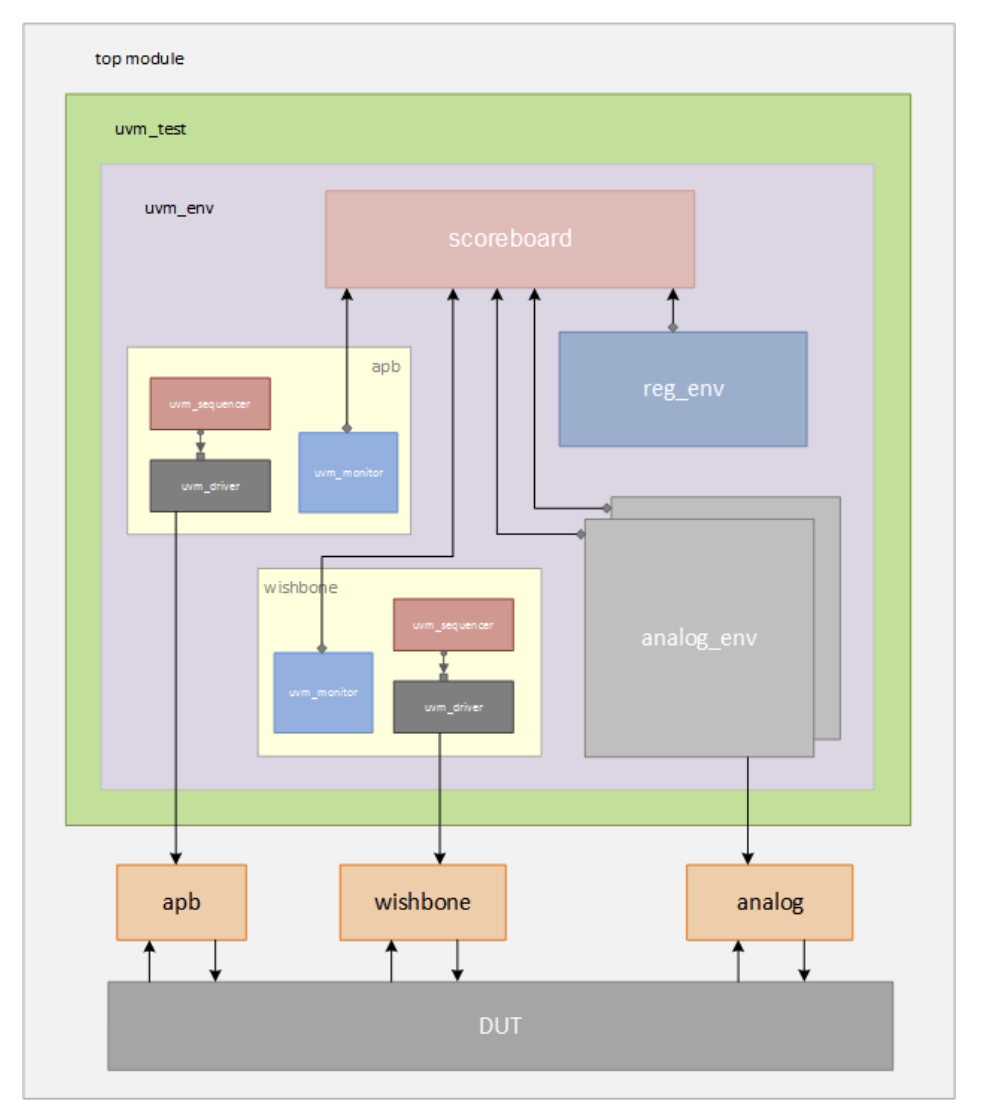

UVM environment包含多个可重用的验证组件,并根据test case的需求进行相应的配置。例如,UVM environment可能具有多个agent(对应不同的interface)、scoreboard、functional coverage collector和一些checker。

对于一个复杂的数字系统,UVM environment可能还集成其他一些较小的UVM environment,这些相对较小的验证环境用于对各个子系统/模块进行验证。所以,被集成的子模块/系统验证环境中的很多组件和sequence都是可以复用的。

为什么验证组件不直接放在test case中?

从技术上讲,一些验证组件可以直接在用户定义的testcase(uvm_test类)中实例化。

class base_test extends uvm_test;`uvm_component_utils(base_test)apb_agent m_apb_agent;spi_agent m_spi_agent;base_scoreboard m_base_scbd;virtual function void build_phase(uvm_phase phase);// Instantiate agents and scoreboardendfunctionendclass

但是,不建议这样做:test case不能够复用,因为它们依赖于特定的验证环境,针对每个testcase都开发一个uvm environment比较低效。 简单来说,uvm environment存在的意义就是不同的testcase都使用同一套验证环境代码 ,是为了验证环境的复用性考虑的。

因此,始终建议开发一个比较通用的,适用所有test case的验证环境, 然后在多个test case中实例化该验证环境类uvm environment。此外,不同的testcase可以配置、启动、禁用验证环境中的各种配置,可能是激励的随机机制、agent的active/passive模式,也可能是scoreboard的开关。

创建 UVM environment的步骤

- 创建一个继承自uvm_env的自定义类,注册到工厂,并调用 new函数

// my_env is user-given name for this class that has been derived from "uvm_env"class my_env extends uvm_env;// [Recommended] Makes this driver more re-usable`uvm_component_utils (my_env)// This is standard code for all componentsfunction new (string name = "my_env", uvm_component parent = null);super.new (name, parent);endfunction// Code for rest of the steps come hereendclass

声明和构建验证环境中各个验证组件

// apb_agnt and other components are assumed to be user-defined classes that already exist in TBapb_agnt m_apb_agnt;func_cov m_func_cov;scbd m_scbd;env_cfg m_env_cfg;// Build components within the "build_phase"virtual function void build_phase (uvm_phase phase);super.build_phase (phase);m_apb_agnt = apb_agnt::type_id::create ("m_apb_agnt", this);m_func_cov = func_cov::type_id::create ("m_func_cov", this);m_scbd = scbd::type_id::create ("m_scbd", this);// [Optional] Collect configuration objects from the test class if applicableif (uvm_config_db #(env_cfg)::get(this, "", "env_cfg", m_env_cfg))`uvm_fatal ("build_phase", "Did not get a configuration object for env")// [Optional] Pass other configuration objects to sub-components via uvm_config_dbendfunction

在自定义uvm_env类的connect_phase中根据需要连接各个验证组件

virtual function void connect_phase (uvm_phase phase); // A few examples:// Connect analysis ports from agent to the scoreboard// Connect functional coverage component analysis ports// ...endfunction

UVM Environment 示例(对应上面提到的的验证环境图)

class my_top_env extends uvm_env;`uvm_component_utils (my_env)agent_apb m_apb_agt;agent_wishbone m_wb_agt;env_register m_reg_env;env_analog m_analog_env [2];scoreboard m_scbd;function new (string name = "my_env", uvm_component parent);super.new (name, parent);endfunctionvirtual function void build_phase (uvm_phase phase);super.build_phase (phase);// Instantiate different agents and environments herem_apb_agt = agent_apb::type_id::create ("m_apb_agt", this);m_wb_agt = agent_wishbone::type_id::create ("m_wb_agt", this);m_reg_env = env_register::type_id::create ("m_reg_env", this);foreach (m_analog_env[i])m_analog_env[i] = env_analog::type_id::create ($sformatf("m_analog_env%0d",m_analog_env[i]), this);m_scbd = scoreboard::type_id::create ("m_scbd", this);endfunctionvirtual function void connect_phase (uvm_phase phase);// Connect between different environments, agents, analysis ports, and scoreboard hereendfunctionendclass

其中env_analog或env_register中也可以有一些agent和scoreboard。 可以看到UVM在可重用性方面很强大,主要取决于这种分层结构和TLM连接。 也正是因为这种复用,可以分别独立验证env_analog和env_register,而在更加上层的验证环境my_top_env中,可能只需要关注子系统之间的交互。

-

UVM

+关注

关注

0文章

183浏览量

20108 -

代码

+关注

关注

30文章

4977浏览量

74420 -

数字系统

+关注

关注

0文章

165浏览量

21635

发布评论请先 登录

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

什么是uvm?uvm的特点有哪些呢

谈谈UVM中的uvm_info打印

UVM中seq.start()和default_sequence执行顺序

The Java Language Environment

Creating An Efficient Verification Environment using Synopsy

Agilent Environment and Social

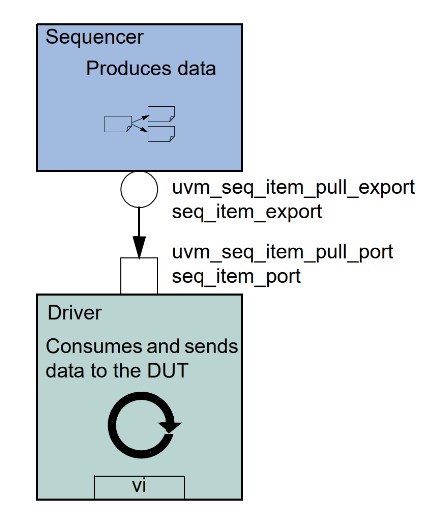

UVM driver和sequencer的通信

UVM中uvm_config_db机制背后的大功臣

UVM中uvm_config_db机制背后的大功臣

一文详解UVM设计模式

什么是UVM environment?

什么是UVM environment?

评论