SRAM也是易失性存储器,但是,与DRAM相比,只要设备连接到电源,信息就被存储,一旦设备断开电源,就会失去信息。

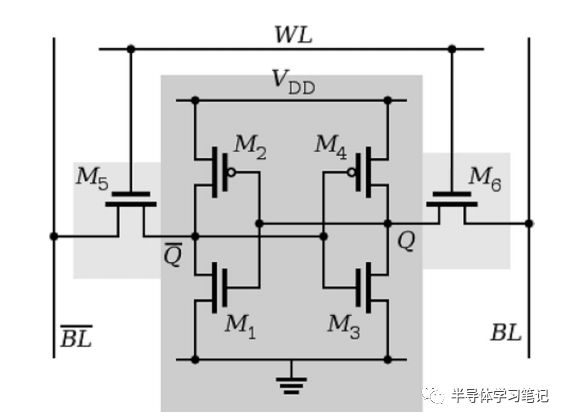

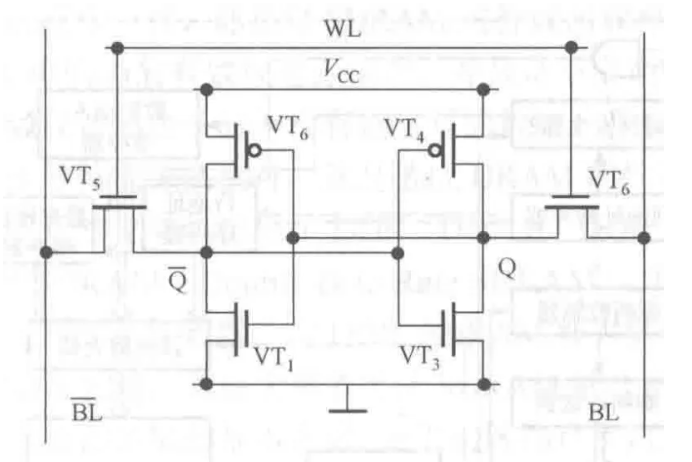

这个设备比DRAM要复杂得多,它一般由6个晶体管组成,因此被称为6T存储器(如图1)。

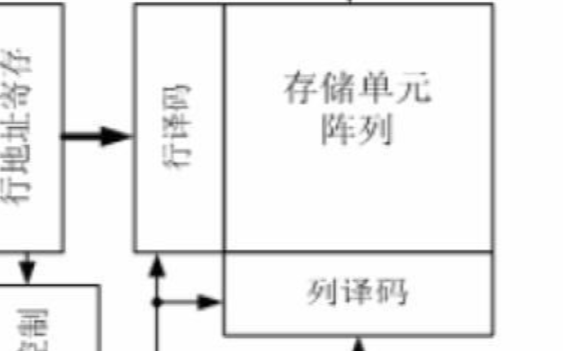

SRAM的每一bit存储在由4个场效应管M1,M2,M3,M4构成的两个交叉耦合的反相器(如图1中深灰色的部分)中。另外两个场效应管(M5,M6)是存储基本单元到用于读写的位线(Bit Line)的控制开关。这种设置,是典型的CMOS工艺,相当于一个“RS锁存器”电路(如图2),只要系统是稳定的供电状态,可以存储信息‘0’或‘1’(即:逻辑等效的低或高电压)。

图1 6晶体管SRAM存储器的功能图

图2 SRAM存储器的等效电路图

根据上图可以看出,一个6晶体管SRAM存储器包括由交叉逆变器M1-M2和M3-M4构成的锁存器和两个存取晶体管M5和M6。M1-M2逆变器的输入信号Q与M3-M4逆变器的输出相连接,M3-M4逆变器的输入信号Q_与M1-M2逆变器的输出反向连接。M5和M6晶体管类似于由字线WL驱动的两个开关,该开关同时使这些晶体管的栅极极化,并允许两位线BL读取存储的信息。

存储在锁存器中的两个二进制信号Q和Q_(‘0’和‘1’或‘1’和‘0’)通过两个存取晶体管M5和M6(浅灰色区域)传输到两个位线(B_L_和BL),M5和M6(浅灰色区域)由连接到M5和M6的每个栅极的字线WL打开或关闭。

存储器的操作可以概括为三个功能:备用、读、写或擦。

备用功能对应于锁存器中信息‘0’或‘1’的保持,是通过字线(WL)在两个N型MOSFET M5和M6的栅极处施加负电压或低电压,使它们不导电的状态,相当于将锁存器与两个位线(BL)隔离。这就实现了锁存器里面的信号不变的状态。

而另一方面,读取操作则是通过将锁存器与两个位线(BL)通信来获得的。连接到两个位线BL的感测放大器(不在这里进行阐述)识别哪一行具有更强的信号,从而读取由位线BL携带的初始信息。感测放大器是连接到两个互补的位线(‘0’和‘1’)两端的电子器件,其功能是在放大两个位线之间的电压差后,识别其中哪个具有‘0’或‘1’的逻辑状态。

写入和擦除操作则是通过打开晶体管M5和M6的通道和在两个位线BL上施加‘0’和‘1’来实现的。

从实际角度来看,SRAM存储器速度非常快,换相时间只有数十纳秒,这使得它们比DRAM快10倍。对于DRAM来说,循环次数(写——擦除)几乎是无限的(>10 ^16^ )。虽然SRAM在切断电源时是易失信息的,但它不需要定期更新,使它在能耗方面比DRAM更有利。但不幸的是,SRAM的复杂性使得它们的制造成本很高,而且它们的大尺寸(面积>140 F ^2^ )不允许高的集成密度。因此,它们在计算机中的使用仅限于低容量的高速缓存内存,用于高速执行重复操作,从而大大缩短了复杂操作的执行时间。

附加介绍:

CMOS反相器是一种电路器件,其输出是输入的逻辑非,即:它给出与输入信号IN相反的输出信号OUT。对于逻辑数据,是通过输入和输出电压转换成逻辑数据‘0’和‘1’来实现的。因此,输入低的“IN”电压信号(编码‘0’),我们将得到一个强的“输出”电压信号(编码‘1’),并且,如果“IN”是强的(‘1’),则“OUT”是低的(‘0’)。

如图所示,CMOS静态反相器,采用倒置CMOS工艺,由两个互补的MOSFET组成,将N型和P型MOSFET的串联组合,即将P-MOSFET的源与N-MOSFET的漏极连接起来。P-MOSFET的漏极被引入一个电压V DD (逻辑信号‘1’),而N-MOSFET的源被接地(逻辑信号‘0’)。这两个栅极互相连接,输入信号“IN”被应用到它们身上。输出信号‘OUT’分别在P和N-MOSFET的源和漏点测量(如上图)。则当输入低电平,则P沟道场效应管开通,N沟道场效应管关闭,输出高电平;当输入高电平,N沟道场效应管开通,P沟道场效应管关闭,输出低电平。这就实现了“反相”输出。

从象征意义上说,逆变器由(b)表示,其中A是输入信号,A_是输出信号。

CMOS逆变特性

当栅极电压较低(IN=‘0’)时,N和P晶体管的通道分别关闭和打开,这意味着输出信号处于电压V DD ,因此OUT=‘1’(c)。

相反,当栅极电压较高(IN=‘1’)时,P和N晶体管分别为非导电(开)和导电(闭合),从而导致输出直接接地,从而使输出。

-

DRAM

+关注

关注

41文章

2406浏览量

189721 -

存储器

+关注

关注

39文章

7769浏览量

172396 -

sram

+关注

关注

6文章

843浏览量

117768

发布评论请先 登录

SRAM的工作原理及其使用方法了解

如何选择最适用的sram存储器

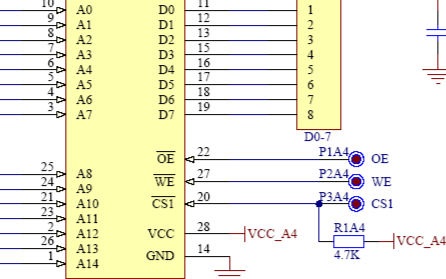

浅谈异步SRAM存储器接口电路图

SRAM随机存储器的特点及结构

SRAM随机存储器的特点及结构

SRAM存储器的工作原理

SRAM存储器的工作原理

评论