上一篇文章提到了DLL的谐波问题,解决该问题的有效措施是对Vcont进行复位上拉。

01 DLL的一种应用场景:面对谐波锁定的风险

本篇文章是对DLL的谐波锁定问题做进一步的探讨。我们考虑下面这样一种应用情景:一款带Vcont复位上拉的DLL电路,在复位结束之后,参考时钟在很长一段时间之后才到来。请问,这时候该DLL有没有可能发生谐波锁定问题?

答案是有可能。在复位结束之后,Vcont虽然为VDD,如果这时候DLL还没有参考时钟输入,Vcont将很难保持VDD大小的电压,这是因为即使电荷泵的上下通路为高阻抗,还是会存在一定的电荷泄露,随着时间的加长,Vcont电压会逐渐减小。此外,没有参考时钟输入,UP和DN的状态并不确定,Vcont的初值还面对着可能被放电路径释放的风险(如果DN刚好有效)。这种情况下,假设参考时钟在很长一段时间后才来到,那么此时的Vcont已经降低到0~VDD之间的某个中间值,且该值在不同工艺角、温度、供电下是不同的,且难以预测,因此仍然有可能出现谐波锁定现象(详细原因可以看参考帖)。

这就像是,虽然我们增加了Vcont赋初值的预防措施,但仍然会有一些特殊的场景使初值存在的作用失效。

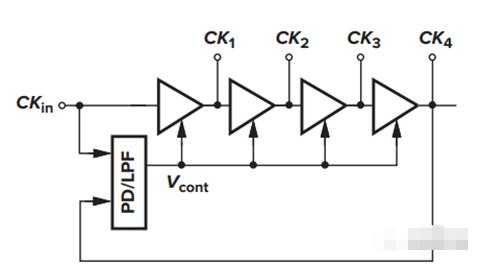

图1 DLL典型结构

02 VCDL时钟检测电路解决问题

我们思考一下,上述问题的关键是在参考时钟到来之前Vcont的电压漂移问题。因此在参考时钟给到之前,我们只要保证Vcont即使在复位释放之后仍然能保持在VDD大小,那么该问题就得到了解决。基于这个思路,下图所示的电路在工程实践上得到了广泛的应用。

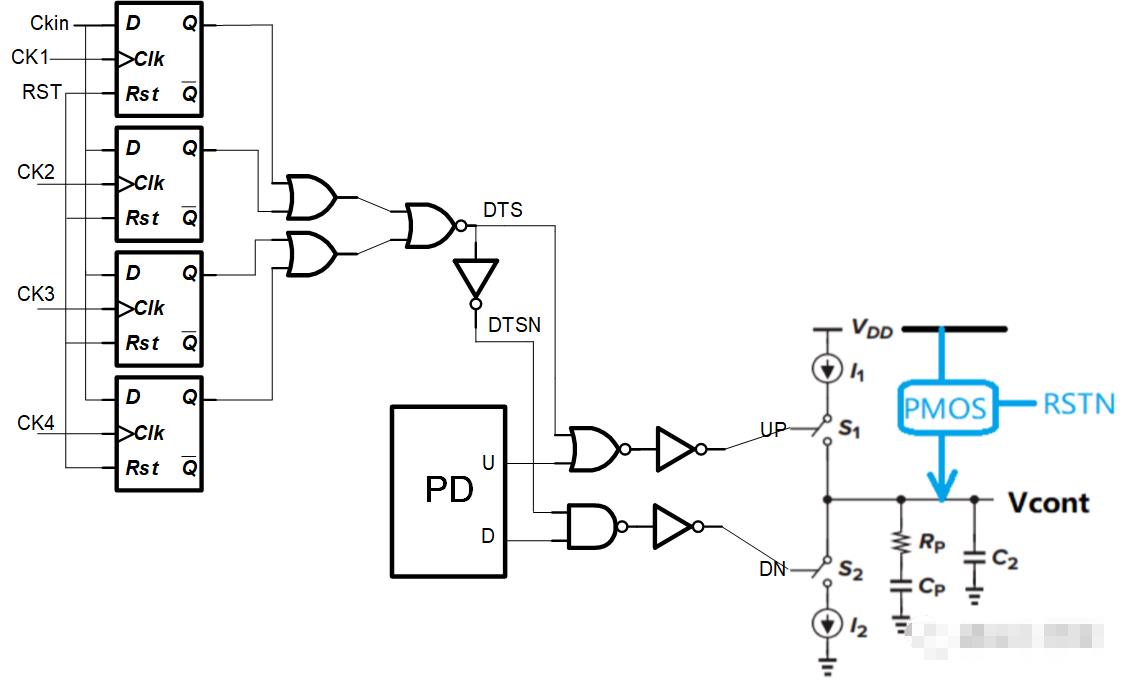

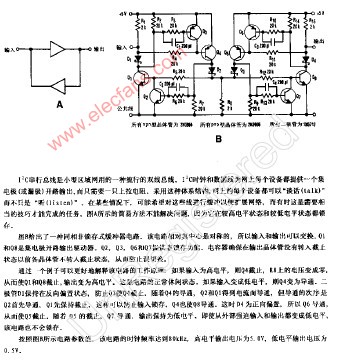

图2 增加时钟检测电路后的电路

该电路利用多个DFF设计了一个VCDL时钟检测电路,CKin连接到DFF的数据端,从上到下每个DFF的时钟端从VCDL引出,且每个DFF被同步复位。在没有参考时钟时,VCDL也无法输出时钟。在复位期间,RST=1,一方面,RSTN=0,Vcont被上拉到VDD;另一方面,时钟检测电路中,所有DFF被复位,Q=0,DTS=1,DTSN=0,此时S1=1,S2=0,充电电流源打开,放电电流源关闭,Vcont的电位被进一步加强,使其保持VDD大小。

我们再回顾一下前文提到的应用场景,再看看这时候DLL会如何反应:当复位释放之后,假设CKin仍然没有到来,所有的DFF的时钟端不会出现边沿跳变,作为边沿触发型的DFF,其Q端维持之前的值,因此DTS仍等于1,所以S1仍然打开,S2仍然关闭,Vcont端被充电,其始终维持VDD电位不变。当CKin一旦到来,CK1~CK4自然会有时钟输出,DFF会有采样输出,只要有一路Q=1,DTS就跳变为0,关闭对PD输出状态的控制。此后,Loop将在负反馈作用下进入锁相过程。

总结:

和前一篇帖子的核心点一致:保证Vcont赋初值。本篇针对一种特殊的、但并不是不常见的应用场景进行了分析,指出了该场景下DLL面对的谐波锁定风险,并给出了解决方案。解决的办法需要增加额外的电路,即VCDL时钟检测电路。

-

检测电路

+关注

关注

13文章

308浏览量

58192 -

dll

+关注

关注

0文章

115浏览量

45445 -

谐波

+关注

关注

7文章

828浏览量

41819 -

时钟

+关注

关注

11文章

1735浏览量

131567 -

VDD

+关注

关注

1文章

312浏览量

33283

发布评论请先 登录

相关推荐

三级放大电路噪音问题(解决问题可发红包)急!!

基于SOC的血沉仪时钟及温度检测系统

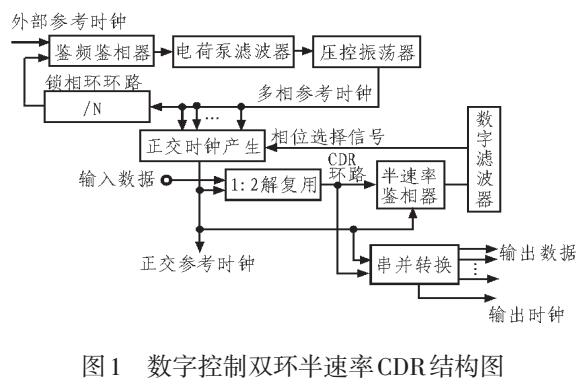

基于高速CMOS时钟的数据恢复电路设计与仿真

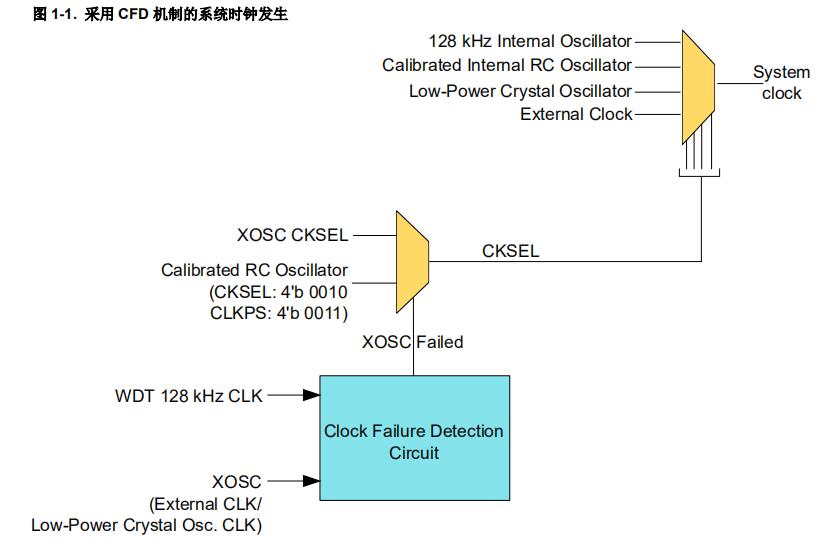

使用ATmega328PB的时钟故障检测

VCDL时钟检测电路解决问题

VCDL时钟检测电路解决问题

评论