大多数数字系统中,除了需要具有逻辑运算和算数功能的组合逻辑电路外,还需要具有存储功能的电路,组合逻辑与时序逻辑可构成时序逻辑电路,简称时序电路。现在讨论实现存储功能的两种逻辑单元电路,即锁存器和触发器。

双稳态:电子电路中。其双稳态电路的特点是:在没有外来触发信号的作用下,电路始终处于原来的稳定状态。在外加输入触发信号作用下,双稳态电路从一个稳定状态翻转到另一个稳定状态。由于它具有两个稳定状态,故称为双稳态电路。

单稳态电路只有一种稳定状态,受到触发以后,会自动转到稳定状态。双稳态电路就两种稳定状态,受到触发发后,就稳定在那种状态,受到下一次触发以后,再翻转。

商店的弹簧门,就是一种“单稳态”。人一推开门后,处在一种不稳定状态,人一进入后就会自动回复到关门这种稳定状态。家中的普通门,就是“双稳态”,门一被打开,就停在那里了,是一种稳态;将它关上了,又是一种稳态。

锁存器:

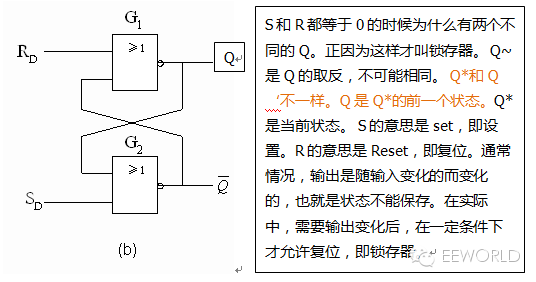

锁存器是构成各种时序电路的基本元件,它的特点是具有0和1两种稳定的状态,一旦状态被确定,就能自行保持,即长期存储1位的二进制码,直到有外部信号作用时才有可能改变。锁存器是一种对电平敏感的存储单元电路,它们可以在特定输入电平作用下改变状态。

锁存器的当前状态与前一个状态有关。 当R为1,输出被复位,即Q为0。不论前一个状态是什么,即不论Q的值是1还是0。 当S为1,R为0的情况下,Q即为0。不论前一个状态是什么,即不论Q的值是1还是0, 当S和R状态相同时(不论是1还是0),Q的值为Q的值。即,保持状态,锁存器。

代码见1_latch

D锁存器

逻辑门控D锁存器: 由于当R、S为1的时候,锁存状态不确定,故为了消除SR锁存器的不确定状态,可在电路的S和R输入端连接一个非门G5从而保证S和R不同时为1的条件。此外还有传输门控D锁存器,

触发器

RS触发器(RS (Reset-Set) flip-flop)

RS触发器是双稳态触发器,俩个与非门交叉耦合构成。由表可知它具有置“0”、置“1”和 “保持”三种功能。即在CP产生上升沿时才进行数据变化。RS触发器分为上升沿触发和下降沿触发。注意Rd、Sd都是低电平有效。但我们到不需要注意这些,只需明白,cp上升沿时,R为0复位,这时输出只和置位的S有关。如果R为1,则输出均为0,根据电路结构可知。当RS均为1时会出现混乱,所以需要有约束条件来限制。

代码见RS_regist

JK触发器(JK (Jump-Key)flip-flop )

JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

D触发器(data flip-flop)

D触发器可以说是最常用的了。在写Verilog时,触发器均为D触发器。双稳态多谐振荡器(Bistable Multivibrator),是一种应用在数字电路上具有记忆功能的循序逻辑组件,可记录二进位制数字信号“1”和“0”。触发器是构成时序逻辑电路以及各种复杂数字系统的基本逻辑单元。触发器的线路图由逻辑门组合而成,其结构均由SR锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时钟频率之间的相互影响。

代码:D_flip_flop

T触发器 T (Toggle flip-flop)

T触发器是一种使用较多的触发器,将JK触发器的J、K输入端相连,接成一个输入端T,即J = K = T,组成的触发器就称为T触发器。图5.5.1为T触发器逻辑符号。在JK触发器的基础上可以得出T触发器的特性方程为

当T=0时,由其特性方程可得,即在时钟信号的作用下,输出端的状态保持不变。

当T=1时,由其特性方程可得,即在时钟信号下降沿的作用下,输出端的状态翻转为相反的状态。在这种条件下,也称为触发器

代码:T_flop_flip

-

二进制

+关注

关注

2文章

801浏览量

41782 -

时序电路

+关注

关注

1文章

114浏览量

21753 -

锁存器

+关注

关注

8文章

916浏览量

41691 -

触发器

+关注

关注

14文章

2019浏览量

61399 -

单元电路

+关注

关注

4文章

32浏览量

19493

发布评论请先 登录

相关推荐

FPGA学习之触发器和锁存器

FPGA学习之触发器和锁存器

评论