数字仿真器(Simulator)是一种大型EDA工业软件,是数字验证领域的基础工具之一,也是为数不多的签核(sign-off)级工具。其实历史上第一款 EDA 软件SPICE,就是从仿真开始的。可以说,EDA软件从诞生之日起,就带着强烈的仿真基因。因此,如果没有一款独立自主的数字仿真器,国产EDA实现对国外工具垄断的打破就无从谈起。

目前,行业主流的仿真器,诸如VCS,Xcelium, Questa等,都是国外EDA大厂花了数十年的时间开发、迭代而来的。这些软件内部设计极其复杂、代码量巨大,单单维护的团队人数就可达数百人甚至上千人。由此可见,数字仿真器技术开发难度之大。

合抱之木,生于毫末;九层之台,起于累土。2021年11月,国内系统级验证EDA解决方案提供商芯华章发布了首款数字仿真器产品穹鼎GalaxSim,并得到中科院半导体、芯来科技等用户一线项目部署。GalaxSim在开发过程中,结合国产EDA的迫切需求,选择了合适的技术路线、开发模式,依托研发团队的丰富EDA经验及高效的工作,站在更高的技术起点上,用几年的时间正在追赶国外几十年的路。

现在我们梳理实践所得和浅见,希望与行业同仁进行分享交流,帮助志在推动国内EDA数字仿真器进步的有志之士,提供一些可能的启发和参考,共同建立良好的EDA发展生态。

本篇我们将以穹鼎GalaxSim为例,展示一款商用级别的数字仿真器从0到1的开发过程,包括商用仿真器的技术指标、开发模式、技术路线等方面。

1. 数字仿真器的技术要求

数字仿真器在验证中发挥着举足轻重的作用。判断一款国产仿真器是否能真的商用,甚至可以与国际主流选择的仿真器并驾齐驱, 一般要看它是否满足以下四点硬性要求:

1

全面的SystemVerilog语法覆盖

SystemVerilog可以说是最复杂的语言之一,而数字仿真器又是EDA工具中对SystemVerilog支持最全面的工具。

2

仿真器相对其他验证工具,是sign-off级别的,因此要求仿真器必须严格按照事件驱动型的算法进行仿真调度,符合IEEE1800等标准。

3

高性能

仿真器的性能直接决定了用户在验证上的成本。假如某个优化可以使仿真速度提高2x, 那可以使原本一个月完成的回归测试缩短到二周,从而给客户省掉很大的验证支出。

4

高可靠性

作为大型工业软件,仿真器的设计极其复杂。一款大型软件,涉及到的模块非常多,参与的开发者也非常多。如何确保软件质量可控,在客户的超大设计上能跑几十小时,甚至几周不出现故障,是考验一个仿真器能否真正商用的重要指标之一。因此,作为用户sign-off 的工具,仿真器的故障率必须极低。即使出现故障,也能在很短的时间内排查并修复。

2.开发模式的选择:瀑布式开发VS敏捷开发

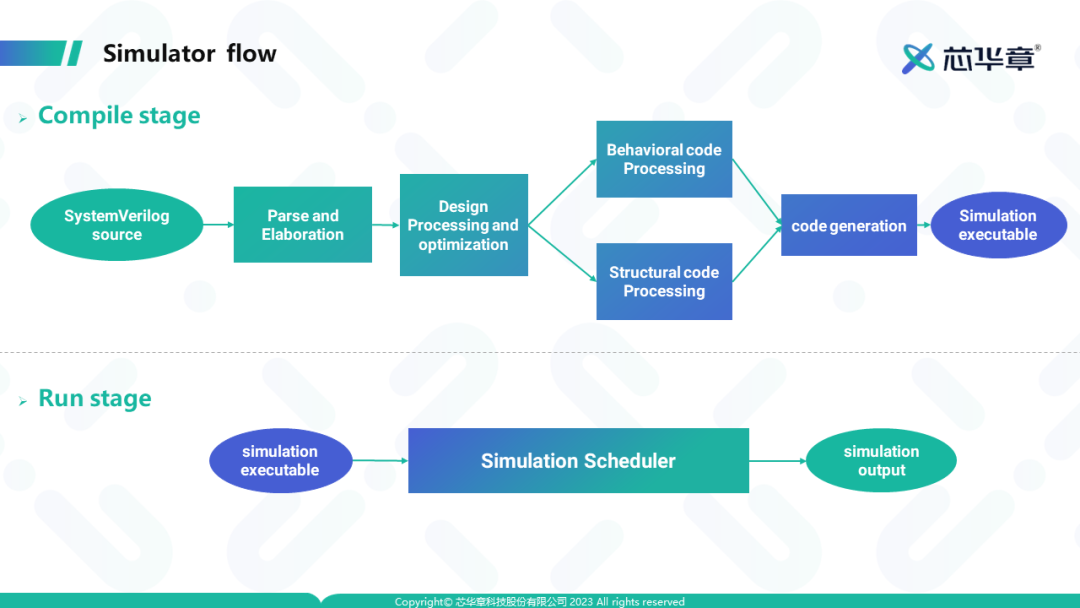

编译型数字仿真器的原理如上图所示,它从verilog source到最终机器码生成,中间经历了多个环节。它既具备了Compiler的特点,同时又是一个数字电路仿真器。它集成了多种底层技术,涉及编译、算法、图论等知识。

尽管从概念上,我们可以把这个过程分解成不同的阶段,但是在实际实现上,我们其实很难单独把某一块抽出来。以parser/elaboration阶段为例,这个阶段需要把RTL的语法解析出来。从功能上,它和后面的阶段是不同的。然而,如果把它作为一个模块独立开发,就会面临无法测试的困难。因为有些elaboration的结果,需要到了runtime阶段才可能测出是否正确。

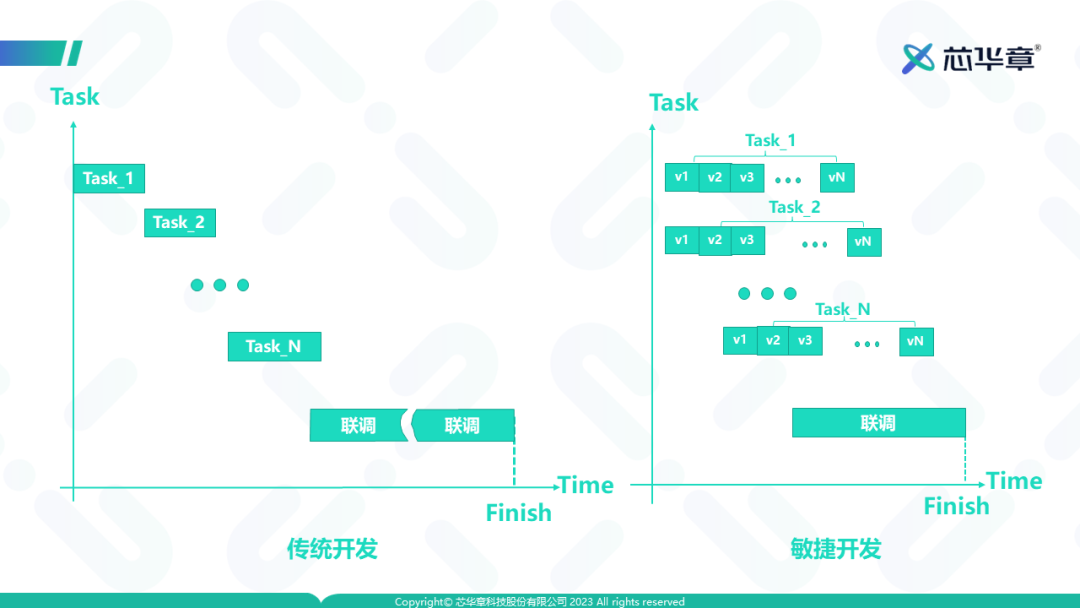

软件开发有两种模式,一种是传统的瀑布式模式,把一个软件划分成若干模块。每个模块都定义好spec,然后分配给各个团队开发;到了一定节点,再进行联调。另一种是敏捷开发,就是快速将flow打通,进行不停地迭代,就像生物界胚胎的成长一样,逐步将软件迭代成熟。

上图给出了两种不同模式的区别。由于Simulator涉及到的环节非常多,有很多任务是有依赖关系的,只能串行开展。如果按照传统的模式,不仅完成所有任务的总时间会变得很长,它还会导致最后联调的时间非常的不确定。因为很多模块的耦合性很强,很多问题需要等到最后所有模块放在一起后才能发现。

基于此,为了降低研发风险,提高开发效率,GalaxSim的开发采用了敏捷开发模式。在敏捷开发模式下,每个任务可以不用一步到位,而是可以先做一个比较初级的版本,从v1开始进行迭代,直到vN。完成每个迭代的时间,是大大短于完成整个任务的时间的。这样,依赖于该任务的其他任务就可以提前开展了。联调阶段的不确定也会大大降低,因为很多问题都可以在前期阶段暴露出来。通过敏捷开发,芯华章的GalaxSim可以更合理地调配资源,并通过大量迭代,使得产品能达到商用要求。

3. 技术路线的选择:守正、创新

从0到1,开发一款具备国产自主知识产权的仿真器,肯定不能仅仅做一个me too的产品,需要有创新、超越。我们面临的问题是,做一个怎样的仿真器,能在解决国产替代的基础上,实现最终的超越?这里面既要守正,也要创新。

何谓守正?创新的前提首先要先解决有无的问题。上文提到,不管采用什么技术,仿真器都必须满足四个指标:SystemVerilog、精度、性能、可靠性。因此,任何研发路线与技术的选择,都必须满足以上4个约束条件。

与此同时,我们吸取主流数字仿真器的历史研发教训,针对国内使用环境进行客制化创新。比如在SystemVerilog方面,很多主流仿真器的支持其实并不是一步到位完成的,而是在一系列并购后集成进来的。GalaxSim在这方面,可以发挥后发优势,采用全新的设计框架,更好实现SystemVerilog的丰富语法,让整个compile flow无缝对接,避免不断“打补丁”带来的技术冗余与滞涩,提供更完整、一体化的验证解决方案。

以性能为例,runtime是仿真器的一项重要技术指标。大多数国际主流仿真器在过去数十年都做了大量的工作。然而,compile time 也是性能的一部分。近5-10年,随着设计规模越来越大,compile time 也日益成为性能瓶颈。而且,compile time 和 run time常常是矛盾的。GalaxSim使用创新底层架构,在提高runtime性能的同时,兼顾了compile time的控制。

4. “蝶变”:GalaxSim的迭代历程

敏捷开发意味着快速的软件迭代。

GalaxSim 的迭代历程,比较类似于一个胚胎的成长过程。胚胎每一步的变化并不大(比如细胞分裂),然而,经过足够的变化,最终就会由量变到质变,就像蝶变一样。

如何确保GalaxSim的迭代是按照我们设计的方向,而不会走偏呢?这里面,软件的迭代又非常像生物的进化,我们需要设计好一个目标(生存条件),以及一个进化环境。根据前文所述,GalaxSim从0到1的第一阶段目标,是要演变成一个至少满足4个约束条件的仿真器。

4.1

以终为始,设计迭代目标

第一阶段我们会以终为始,根据上文提到的四点对仿真器的硬性要求,分别制定多维度可量化的迭代目标,通过不断的调试达成各项指标。

4.2

进化环境的搭建

如何确保软件向着我们设置的目标进化,而不是走偏,进化环境至关重要。芯华章的研发团队为此专门搭建了一套内部CICD flow, 包含了回归测试系统,这个系统包含了大量的测试用例,各种测试基准(benchmark)。GalaxSim在这些用例中的表现结果会被实时监控。尤其是性能方面,我们的系统引入了类似银行的记账功能。每个研发环节导致的slowdown都会被记录备案,每一笔帐都可以追溯。这些严苛的环境,确保了软件最终的性能及质量。

值得一提的是,这套系统是我们在第一天就开始着手搭建的,与GalaxSim的核心代码是同步开发的。

4.3

Galaxsim的主要迭代节点:

5. 现状:已获得一线项目部署

目前GalaxSim已经在中科院半导体所、芯来科技等若干客户的一线项目中得到应用,性能符合客户预期。

6. 总结

在未来,GalaxSim的进化还会继续,并拥抱更多的创新,最终实现国产数字仿真器的超越。

审核编辑:刘清

-

仿真器

+关注

关注

14文章

1020浏览量

84150 -

EDA技术

+关注

关注

12文章

173浏览量

37093 -

SPICE

+关注

关注

6文章

189浏览量

42936 -

VCS

+关注

关注

0文章

80浏览量

9697

原文标题:解码国产EDA数字仿真器系列之一 | 从零到一 如何构建一款先进的数字仿真器

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电气系统中,如何选择一款最为适配的数字隔离芯片?

从零到一如何构建一款先进的数字仿真器呢?

从零到一如何构建一款先进的数字仿真器呢?

评论