Cortex-M0处理器允许两种形式的中断请求:电平触发和脉冲输入。

电平触发是外设的中断请求有持续的电平信号,若电平信号在处理器从ISR返回之前没有被取消,则中断返回后将再次触发已经服务过的中断。

脉冲中断是在信号的上升沿同步采样的中断信号,为了确保NVIC检测到中断,外设必须维持中断信号至少一个时钟周期,在此期间,NVIC检测脉冲和锁存中断。后续的脉冲可以将暂挂状态加到活动中断中,使状态为中断活动且挂起。然而,在有限周期内发生的多个脉冲只登记作为中断调度的单个事件。

哪些中断是电平触发的,哪些是脉冲触发的,具体选择哪一种是根据芯片设计来决定,不过大多数的外设使用电平触发中断输出。

一、电平触发和脉冲输入

Cortex-M0处理器锁存所有中断,外围中断成为等待其中一个原因是:

NVIC检测到中断信号的上升沿

软件写入相应的中断集挂起寄存器位

挂起的中断将一直挂起,直到下列情况之一发生:

处理器为中断进入ISR,这将改变中断的状态等待活跃:

对于电平触发型中断,当处理器从ISR返回时,NVIC采样中断信号。如果中断信号仍然有效,表示中断的状态更改为pending,这可能会导致处理器立即重新进入ISR。否则,中断的状态将变为非活动状态。

对于脉冲触发型中断,NVIC继续监视中断信号,如果这样触发时,中断状态变为挂起和活动状态。在这种情况下,当处理器从ISR返回中断状态时,中断状态变为挂起状态可能会导致处理器立即重新进入ISR。如果中断信号不是脉冲而处理器是在ISR,当处理器从ISR返回中断状态变为非活动状态。

软件写入相应的中断清除寄存器位。

对于电平触发型中断,如果中断信号仍然有效,则中断的状态中断不会改变。否则,中断的状态将变为非活动状态。

对于脉冲中断,中断状态变为:

inactive,如果状态是pending

active,如果状态是活动的和挂起的

二、中断处理

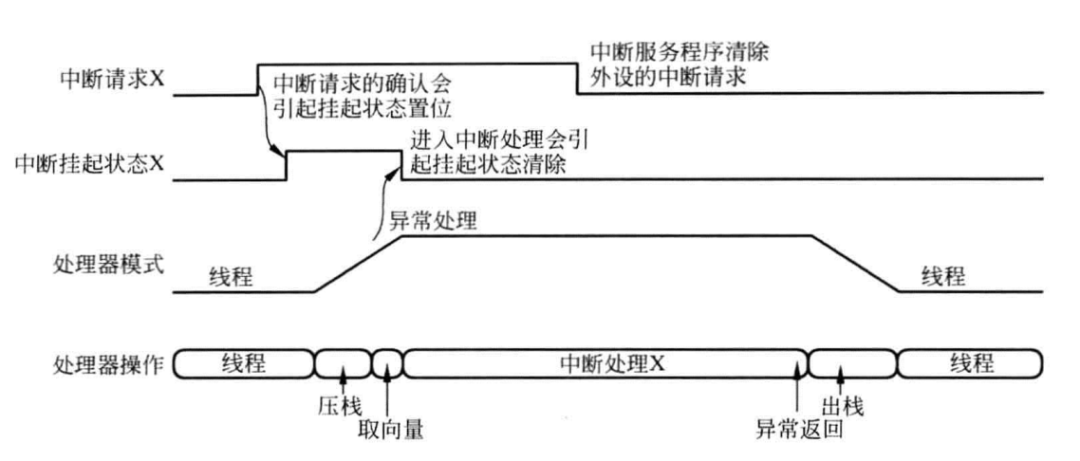

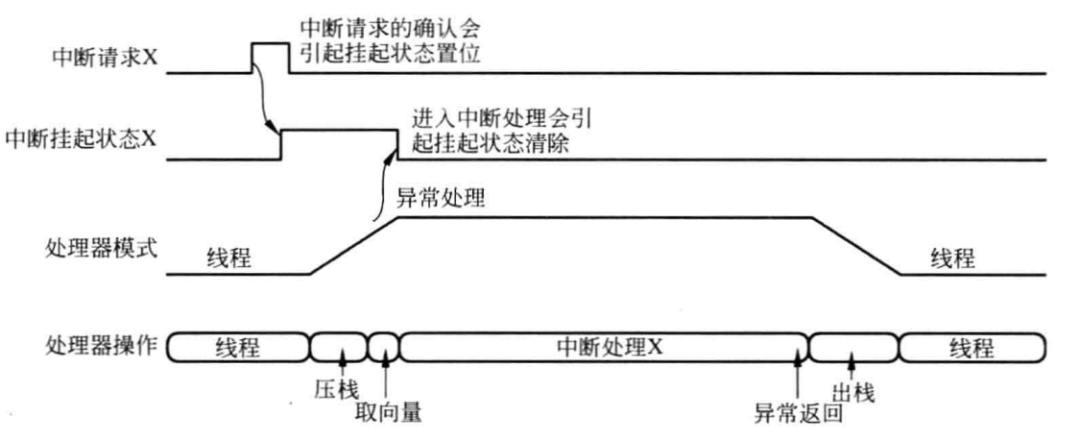

当中断事件发生时,由于外设连接到了NVIC上,中断信号就会得到确认。在处理器执行中断服务并且没有清除外设的中断的信号以前,该信号会保持高电平。在NVIC内部,当检测到有中断发生时,该中断的挂起状态会被置位,当处理器接受该中断并且开始执行中断服务后,挂起状态就会被清除。

针对脉冲输入的中断请求,这种情况下,在中断得到服务之前,挂起状态寄存器将会一直保持该请求。

如果中断请求没有立即执行,并且在确认之前被软件清除了,处理器将会忽略掉本次请求,并且不会执行中断处理。

如果在软件清除挂起状态时,外设仍然保持着中断请求,挂起状态寄存器还会立即生成。

三、中断等待

通常情况下,处理器的中断等待时间为16个周期,这个等待时间从中断确认的处理器时钟周期开始,一直到中断处理开始执行结束。

计算中断等待需具备以下前提:

该中断使能并没有PRIMASK或者其他正在执行的异常处理所屏蔽1

存储器系统没有任何等待状态,在中断处理、压栈、取向量表或者中断处理开始时取指都会用到总线传输,如果存储器系统需要等待,那么总线传输时产生的等待状态则可能使得中断延迟。

下面几种情况可能会导致不同的中断等待:

中断的咬尾连锁,如果一个中断返回时立即产生另外一个中断请求,处理器就会跳过出栈和压栈时间,减少了中断等待时间。

延迟到达,如果中断发生时,另外一个低优先级中断正在进行压栈处理,由于延迟到达,高优先级的中断就会立即执行,这样会导致高优先级的中断等待时间减少。

四、异常屏蔽寄存器PRIMASK

有些对时间敏感的应用,需要在短时间内禁止响应所有的中断,对于这种应用,处理器不是直接使用中断使能、禁止控制寄存器来禁止所有中断再恢复,而是一个单独的特殊寄存器 - PRIMASK,通过它可以屏蔽掉除了NMI和HardFault异常的其他的所有的中断和系统异常。

PRIMASK寄存器只有1位有效,并且在复位后默认为0。该寄存器为0时,所有的中断和异常都处于允许状态,设置为1后,只有NMI和HardFault处于使能状态。

MOVSR0,#0x1;//中断#2 MSRPRIMASK,R0;//将R0的值送到PRIMASK

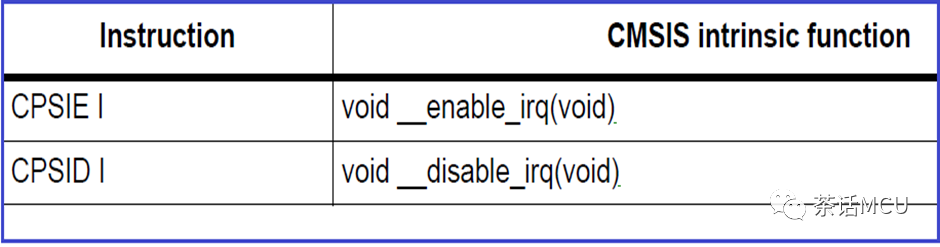

NVIC编程提示软件使用CPSIE i和CPSID i指令来启用和禁用中断。

CPSIEi;//清除PRIMASK(使能中断) CPSIDi;//设置PRIMASK(不响应中断)

CMSIS设备驱动库提供了C语言的实现函数,用户可以直接使用函数来设置和清除PRIMASK寄存器:

void__disable_irq(void)//不响应中断 void__enable_irq(void)//启用中断

在对时间敏感的程序完成后,应该清除PRIMASK。要不然即使在中断处理中使用__disable_irq()函数,处理器将停止接受新的中断请求。主要原因是PRIMASK寄存器和Xpsr是相互独立的,因此异常返回不会影响中断屏蔽状态。

五、NVIC使用提示

确保软件使用正确对齐的寄存器访问,处理器不支持对 NVIC 寄存器的未对齐访问。

即使中断被禁用,它也可以进入挂起状态。

禁用中断只能防止处理器处理中断。

在对中断向量表重定义之前,必须包含所有的异常中断,例如 NMI、HardFault 和外设中断等。

审核编辑:刘清

-

处理器

+关注

关注

68文章

19291浏览量

229907 -

Cortex-M0

+关注

关注

4文章

124浏览量

38695 -

ISR

+关注

关注

0文章

38浏览量

14437 -

NVIC

+关注

关注

0文章

35浏览量

11703 -

中断控制

+关注

关注

0文章

26浏览量

8870

原文标题:Cortex-M0中断控制和系统控制(三)

文章出处:【微信号:Ithingedu,微信公众号:安芯教育科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cortex-M0中断控制和系统控制之异常屏蔽寄存器PRIMASK

Cortex-M0中断控制和系统控制之异常屏蔽寄存器PRIMASK

评论