根据摩尔定律的发展,晶体管的Poly的最小栅极长度已经到达了1nm甚至更小,集成电路的规模越来越大,集成度越来越高。因而,设计者已经无法像最原始的手动将HDL(Verilog/VHDL)等描述语言转化为电路图并描述元件间互联来产生一个门级网表。所以各种用于ASIC设计的EDA工具(DC,Genus等)也应运而生。

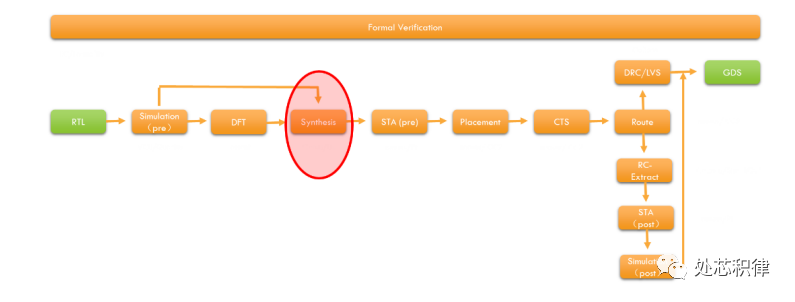

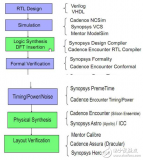

图1 逻辑综合在整个IC设计流程RTL2GDS之间的位置

在整个ASIC设计的流程中,需要前端设计工程师完成可实现功能的RTL代码,最后到用于流片的GDSII则是包含芯片制造厂家的工艺信息,这中间逻辑综合起到了很重要的桥接作用。综合工具会根据我们使用的芯片厂商提供的标准单元库文件的信息,将HDL的RTL代码转化为带工艺信息的门级电路网表(netlist),进行formal形式验证,确保综合过后与RTL阶段功能逻辑一致后,综合阶段时序没风险后再交付给后端工程师来进行布局布线。

小编以S家的DC为例子分享一些在设计过程中需要进行的时钟结构分析(以经典的reg2reg为例子),约束设置,逻辑综合。

首先作为一个优秀的逻辑综合工程师,SDC约束/UPF/CPF约束是少不了写的,尤其是对一些端口和Critical path,一个“干净”的网表是后端的完美开局!约束包括环境约束和设计约束,设计约束又分 为时序约束和设计规则约束。整个综合的过程,最关键的部分就是制定一个正确的约束,特别是时序约束。约束定义的好坏影响到综合结果的优劣。

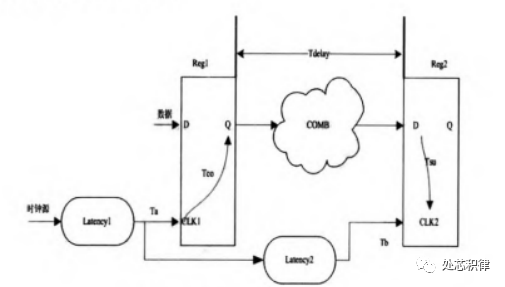

图2 Reg2Reg的经典STA路径

我们以对Clock的约束为例子, Clock latency通常指的就是从Clock pin(source)或IO pad中传递到sink点CP端的延迟,在综合阶段由于是未传播的,因此Skew的值通常是前后两级寄存器对应的source到CP端的Cell Delay或单纯Net delay计算的差值,并包含在uncertainty内。

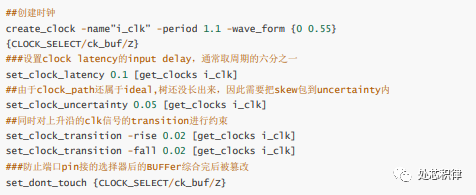

Clock_transiton的值要根据工艺来进行调整,通常在28nm以下的工艺,Clock_transition的值要取在对应时钟周期的十分之一内,具体情况要根据lib内的查找表来定。下面简单写下在SDC中对input clock—i_clk时需要注意的约束:

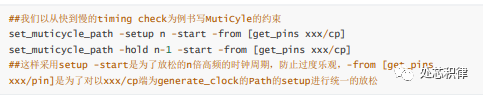

同时,异步复位信号造成网表内的部分寄存器的Q—>rstn端发生setup Violation也是一个逻辑综合工程师会经常遇到的问题,这种异步的复位端时序检查我们需要添加MutiCyle来进行检查上的放松。MutiCyle的放松约束包括:同频时钟,快到慢,慢到快等等,不同情况MutiCyle的约束书写也不尽相同:

介绍完综合工程师需要掌握的部分重要约束的书写,ICer们再跟着小编来看看逻辑综合的每个阶段,到底在干什么吧!

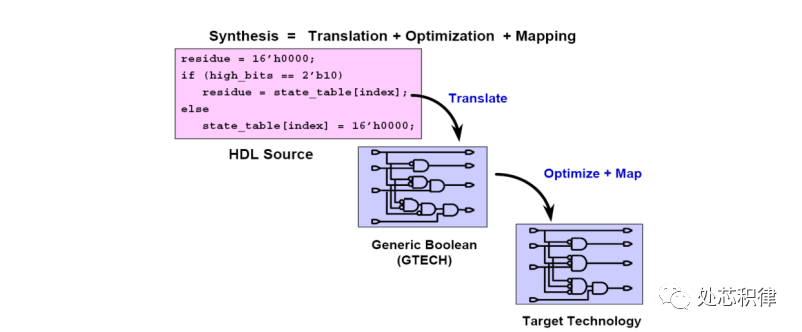

电路的综合一般分为三个步骤,分别是转化(Translation)、逻辑优化(Logic Optimizaion)和映射(Mapping)。

转化(Translation):把描述RTL级的HDL语言(verilog),在约束下转化成综合工具内部的统一用门级描述的电路(Generic Boolean Gates),即HDL—>netlist

逻辑优化(Logic Optimization):把统一用门级描述的电路进行优化,改善路径和门。

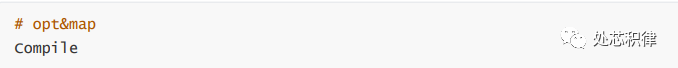

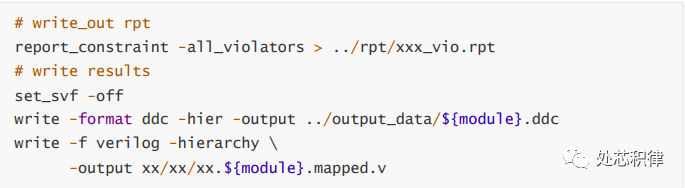

映射(Mapping):把优化了的统一门级描述。以DC为例,DC使用工艺库(lib库)将电路映射出来,得到.ddc文件,该文件包含如映射的门电路信息与网表,.v格式的网表,延时信息(sdf)【sdf文件主要包括cell, net delay信息和cell的hold,setup,recover,removel等边沿应该满足的要求等信息】,工作约束(sdc)【包含clk的信息,以及驱动,输入输出延时,最大最小延迟约束,特殊路径等】等信息。.ddc中包含的网表是实际意义上的综合过后的网表文件(类似PT中的session,innovus内的enc),.v的网表是用于进行后仿的文件。

在上面的过程中,约束对于综合而言非常重要,如果不施加约束,综合工具会产生非优化(no-opt)的网表,无法满足要求。综合是约束驱动(Constraint driven)的,给定的约束是综合的目标,约束一般是在对整个系统进行时序分析得到的,综合工具会对电路进行优化以满足约束的要求。综合以时序路径为基础进行优化。

综合的具体过程

1. 准备RTL代码,经过前端仿真后才能用于综合;

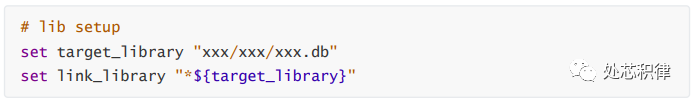

2. 定义库,设定好所需要用到的综合库等多种库;

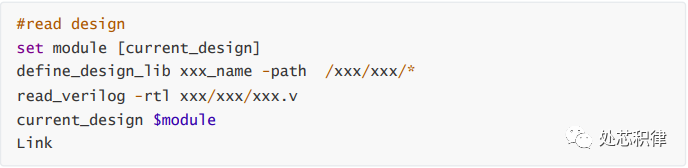

3. 读入设计,综合工具读入RTL代码并进行分析;

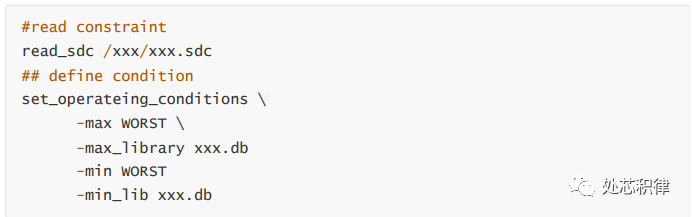

4. 定义设计环境,设定设计的工作环境、端口的驱动和负载、线负载模型等;

5. 设置设计约束(关键),主要是定义时钟和I/O的约束,约束要适当,只有正确的约束才能得到正确的结果;

6. 设置综合策略,top-down和bottom-up两种策略(就是文件目录顺序不一样),根据需求进行选择;

7. 优化设计,综合工具可以根据约束对电路进行优化,也可认为加入命令改变优化方法;

8. 分析和解决设计的问题,在设计综合后,根据报告分析设计中出现的问题,并修订问题;

9. 保存设计数据,综合结束后,保存各种数据以供后续布局布线使用(需先通过formal验证)

好了,今天这期的逻辑综合内容小编就介绍到这里了,下期小编将会以一个带载入UPF流程的Genus的SYN Flow为切入点,进行实战中的综合Flow的解析!

审核编辑:刘清

-

IC设计

+关注

关注

38文章

1296浏览量

103940 -

EDA工具

+关注

关注

4文章

267浏览量

31793 -

HDL

+关注

关注

8文章

327浏览量

47382 -

ASIC技术

+关注

关注

0文章

19浏览量

7575 -

UPF

+关注

关注

0文章

50浏览量

13507

原文标题:搞芯片,不懂逻辑综合是啥?

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IC设计流程简介

IC设计流程介绍

IC验证在现代IC设计流程中的位置和作用

基于google skywater 130nm opensource PDK的快捷方法

DC逻辑综合

全定制和半定制简易IC设计流程介绍

逻辑综合在整个IC设计流程RTL2GDS中的位置

逻辑综合在整个IC设计流程RTL2GDS中的位置

评论