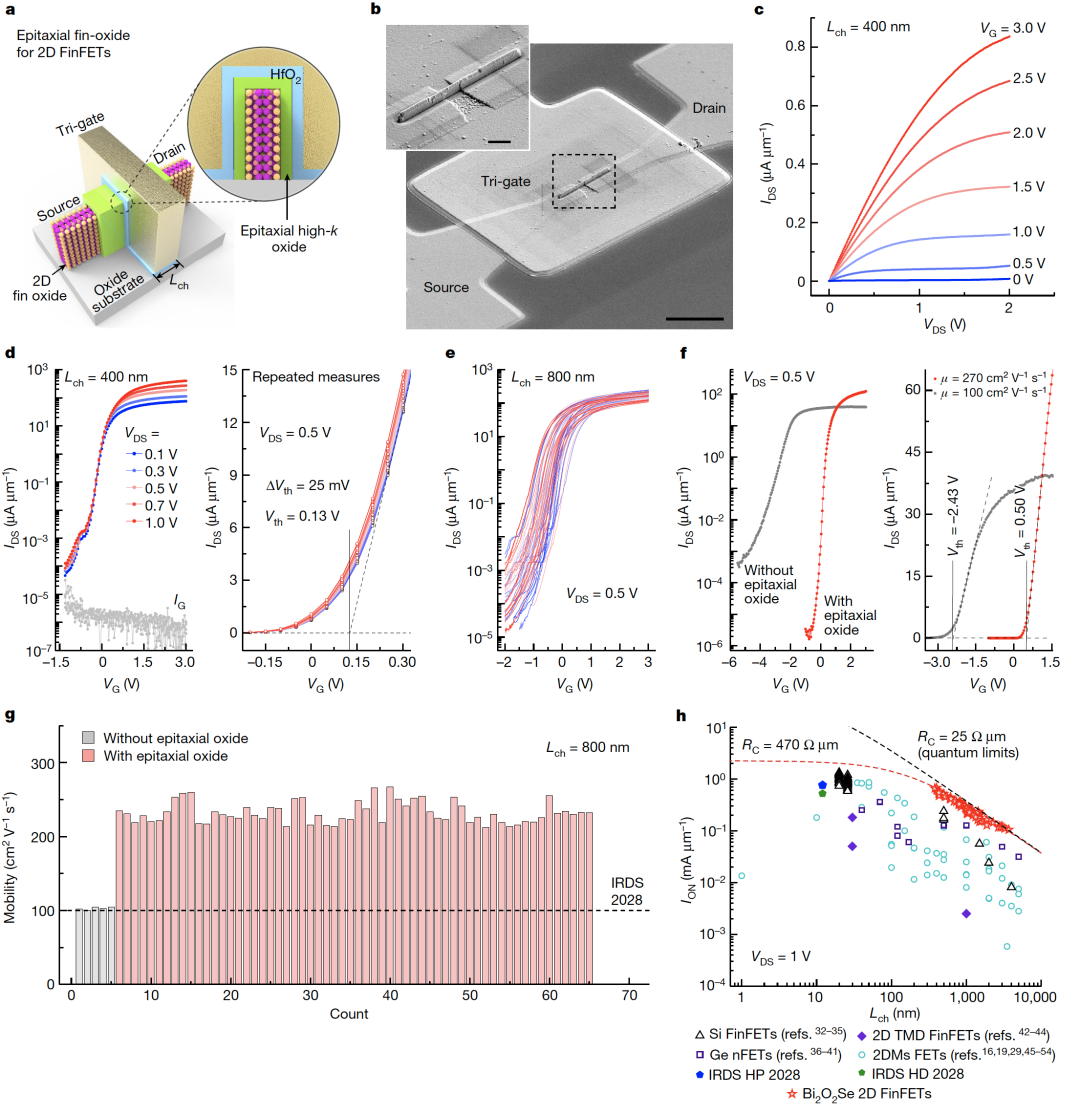

2023年3月22日,北京大学彭海琳教授课题组在《自然》(Nature)期刊上发表题为“2D fin field-effect transistors integrated with epitaxial high-κ gate oxide”的研究论文。该研究报道了一种全新二维半导体垂直鳍片/高介电自氧化物外延集成架构(2D fin/oxide Bi2O2Se/Bi2SeO5),并研制了高性能二维鳍式场效应晶体管(2D FinFET)。二维半导体鳍片/自氧化物外延异质结构具有原子级平整界面和超薄的鳍片厚度(可达一个单胞厚度,~1.2 nm),并实现了晶圆级单一定向阵列制备以及定点、高密度生长。基于Bi2O2Se/Bi2SeO5外延异质结的二维鳍式场效应晶体管具有高达270 cm2/Vs的电子迁移率、极低的关态电流(~1 pA/μm)和很高的开/关态电流比(108),沟道长度为400 nm时开态电流密度高达830 μA/μm,满足国际器件与系统路线图(IRDS)的2028年低功耗器件目标要求。该原创性工作突破了后摩尔时代高速低功耗芯片的关键新材料与新架构三维异质集成瓶颈,为开发突破硅基晶体管极限的未来芯片技术带来新机遇。论文通讯作者是彭海琳教授,并列第一作者是谭聪伟、于梦诗、唐浚川、高啸寅。

研究背景

晶体管作为芯片的核心元器件,通过尺寸微缩、材料多功能集成和架构优化等方式,不断提高芯片集成度,进而提升能效和算力。摩尔定律的推动下,目前传统硅基芯片已成功迭代至5 nm制程节点。随着集成电路制程向亚3纳米技术节点迈进,芯片尺寸微缩逼近硅基材料物理极限,短沟道效应和热效应日趋显著,新材料、新架构和新器件的探索与研究迫在眉睫。

一代制程,一代材料,一代架构。集成电路过去70多年发展中,高迁移率应变硅的应用、高介电常数(κ)氧化物与半导体沟道的异质集成、垂直鳍片架构的开发都为推动现代芯片产业发展做出了划时代的贡献。后摩尔时代,高迁移率二维半导体因其表面无悬挂键、原子级厚度和高迁移率等特性,可实现出色的栅控和高驱动电流,抑制短沟道效应,因此被作为“后硅”延续时代晶体管尺寸微缩的重要材料之一。垂直鳍片(Fin)架构通过增加沟道栅控面积,协同高κ氧化物与鳍片沟道异质集成,大大增强器件栅控能力,抑制短沟道效应,并降低亚阈值漏电流,进一步突破芯片算力、能效和集成瓶颈。以垂直鳍片(Fin)硅基沟道架构和三栅极围绕结构的鳍式场效应晶体管(FinFET)技术在2011年商业化量产于22 nm制程工艺,主导了现代晶体管微缩制程工艺,也是当前最先进的商用5 nm制程集成电路的主流沟道架构。

工艺技术节点进入亚3 nm以后,垂直鳍片沟道架构的新器件开发仍备受关注,人们正在考虑制造基于垂直鳍式结构开发垂直围栅器件(VGAA)或垂直传输场效应晶体管(VTFET),以满足“后摩尔时代”芯片的更高集成度、高性能和低功耗发展要求,世界著名集成电路制造龙头公司IBM和三星已进行相关研发。由此,实现全新架构高迁移率二维层状半导体垂直鳍片/高介电(κ)氧化物异质结的异质集成,开发二维鳍式场效应晶体管(2D FinFET)及二维围栅器件(2D GAA)等新架构器件,有望突破传统硅基半导体亚5 nm厚度量子限域效应的材料限制,将让芯片迭代进入一个崭新的时代,被认为是向下一代晶体管迈进的一个里程碑,属于世界科技前沿的热点和新兴领域。然而,全新架构二维垂直鳍片/高κ氧化物的三维异质集成一直是尚未解决的难题,尚属于空白,亟待突破。

近年来,北京大学彭海琳教授课题组主要从事二维材料物理化学与表界面调控研究,致力于解决新型高迁移率二维材料(金属硫氧族材料、石墨烯等)的表界面生长控制及结构与性能调控中具有挑战性的国际前沿科学问题,创制了全新二维半导体芯片材料Bi2O2Se,受到国内外同行的广泛关注和追踪,开启了二维半导体Bi2O2Se的研究序幕(Nature Nanotechnol.2017, 12, 530;Acc. Mater. Res.2021, 2, 842.),并开发了二维半导体Bi2O2Se的超薄高κ自然氧化物栅介质Bi2SeO5及高性能二维晶体管(Nature Electron.2020, 3, 473;Nature Electron.2022, 5, 643;Nature Mater.2023)。

研究内容与图文

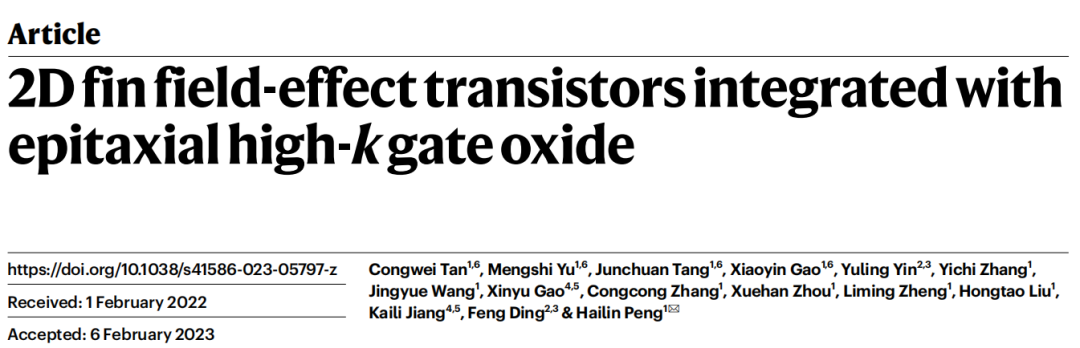

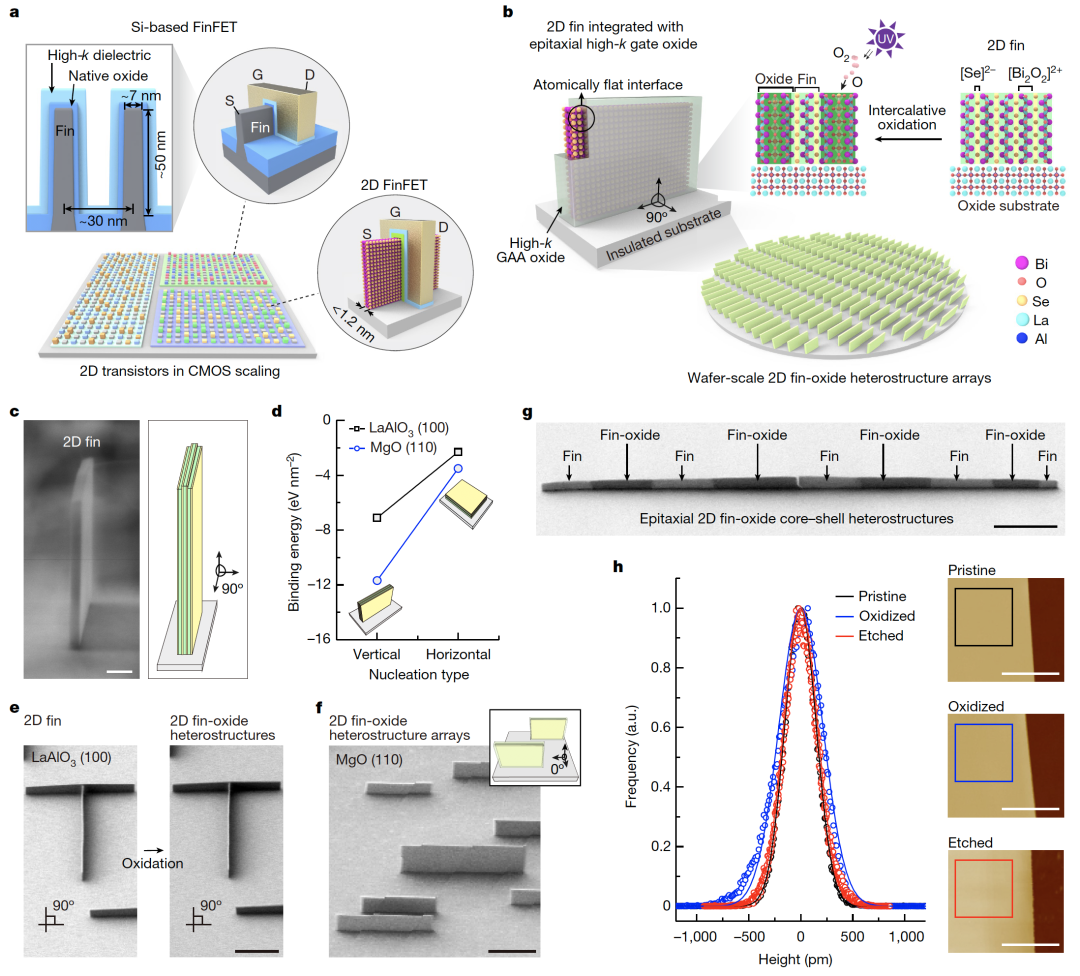

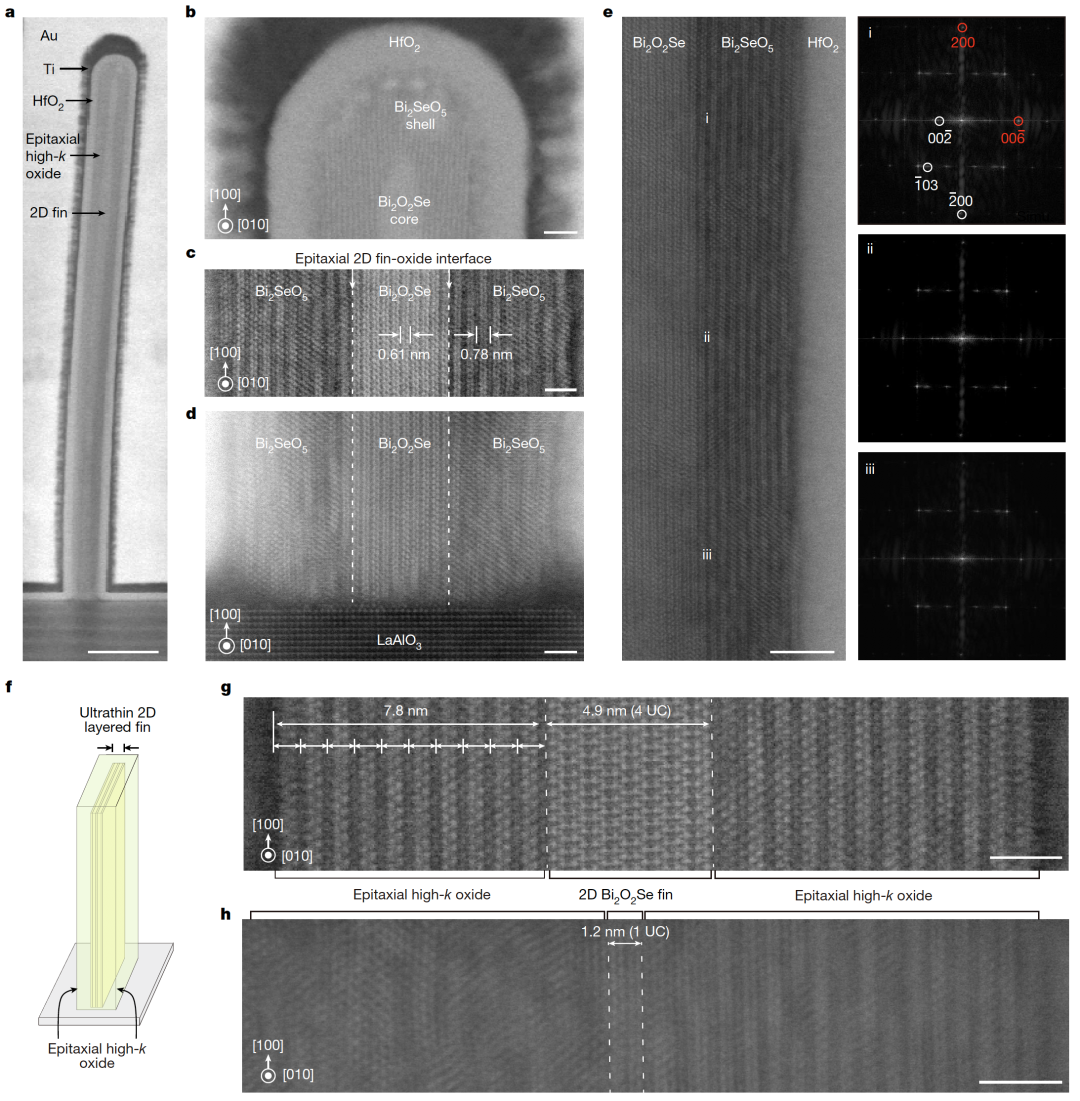

针对全新三维架构中二维沟道材料与介电质集成这一科学难题和实际应用需求,最近,北京大学彭海琳教授课题组独辟蹊径,基于自主研发的新型二维铋基材料体系,实现了自支撑高迁移率二维半导体Bi2O2Se垂直鳍片的精准合成。同时,结合可控氧化手段,实现了晶圆级二维Bi2O2Se垂直鳍片/高κ自氧化物Bi2SeO5的异质集成。值得强调的是,二维Bi2O2Se可被逐层可控插层氧化减薄至1个单胞厚度(1.2纳米),并与高κ自氧化物Bi2SeO5形成原子级平整、晶格匹配的高质量半导体/介电层界面。结合微纳加工及刻蚀技术,精确控制异质架构的成核过程,实现了单一取向的二维垂直鳍片/高κ自氧化物异质结阵列的定点和定向外延。并在此基础上首次实现了沟道厚度约6纳米的高性能二维垂直鳍式晶体管(2D FinFET)的研制。二维FinFET在迁移率(270 cm2/Vs)、关态电流(1 pA/μm)和开关比(108)等性能满足业界高性能低功耗器件要求的同时,相对于商用Si、Ge及过渡金属硫化物等沟道材料,在开态电流密度方面展现出二维FinFET电子学的优势。

图1:二维层状半导体鳍式阵列与高κ全环绕氧化物栅介质集成。

图2:二维层状半导体鳍片/氧化物外延异质结的结构表征。

图3:定向二维鳍片/氧化物异质结阵列的精确集成。

图4:二维鳍片/氧化物异质结制备的二维FinFET电学性能。

该项研究成果实现了“从0到1”的创新突破,首次创制了一类全新架构的高迁移率二维半导体垂直鳍片/高κ自氧化物异质结,并在国际上率先研制了高性能二维鳍式场效应晶体管(2D FinFET),在二维材料表界面生长控制、低维材料结构与性能调控、新原理器件开发、新架构器件三维异质集成、高算力低功耗集成电路芯片等领域具有开拓性意义。该研究成果得到国家自然科学基金委、科技部、北京分子科学国家研究中心、腾讯基金会、北京大学博雅博士后、北京分子科学国家研究中心博士后项目(BMS Junior Fellow)等机构和项目的资助,并得到了北京大学化学与分子工程学院分子材料与纳米加工实验室(MMNL)仪器平台的支持。

审核编辑 :李倩

-

半导体

+关注

关注

335文章

27844浏览量

223981 -

元器件

+关注

关注

113文章

4754浏览量

92994 -

场效应晶体管

+关注

关注

6文章

367浏览量

19627

原文标题:Nature:从0到1!北京大学彭海琳教授课题组报道外延高κ栅介质集成型二维鳍式晶体管

文章出处:【微信号:DT-Semiconductor,微信公众号:DT半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

利用液态金属镓剥离制备二维纳米片(2D NSs)的方法

金属氧化物和柔性石墨烯MOS的区别

半导体研究所在量子点异质外延技术上取得重大突破

二维材料 ALD 的晶圆级集成变化

带有集成金属氧化物半导体场效应晶体管(MOSFET) 的非同步降压稳压器数据表

带有集成金属氧化物半导体场效应晶体管 (MOSFET) 的非同步降压稳压器TPS5403数据表

带有集成金属氧化物半导体场效应晶体管TPS65270数据表

带有集成金属氧化物半导体场效应晶体管 (MOSFET) 的非同步降压稳压器TPS5405数据表

上海合晶挂牌上市,深耕半导体硅外延片领域

半导体衬底和外延有什么区别?

全新二维半导体垂直鳍片/高介电自氧化物外延集成架构

全新二维半导体垂直鳍片/高介电自氧化物外延集成架构

评论