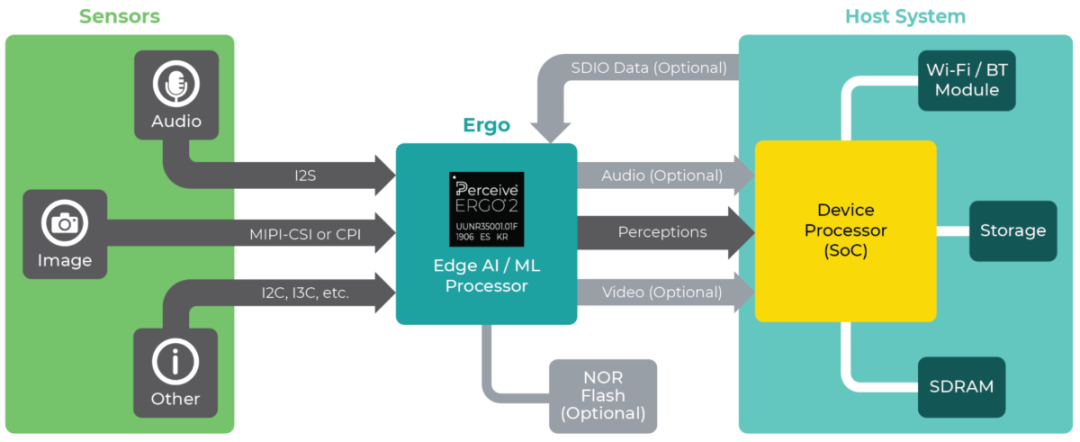

随着越来越多的不同应用对AI处理的需求增长,包括在消费级和企业级设备中对低功耗芯片应用的广泛需求,边缘AI推断正受到越来越多的关注。大部分注意力都集中在优化这些较小部件的神经网络处理引擎及其运行所需的模型上,但优化在许多情况下具有更广泛的意义。在图像识别用例中,图像必须来自某个地方,通常来自具有MIPI接口的传感器。因此,Perceive公司将来自Mixel的低功耗MIPI D-PHY IP集成到最新的Ergo 2 Edge AI处理器上,为AI推理带来片上图像是有道理的。

分辨率和帧速率呈上升趋势

人工智能处理器已经得到了增强,6现在可以通过高分辨率传感器以较高的帧速率处理更大的图像。能够在场景实时变化之前快速推断和做出决定是至关重要的。鉴于此,Ergo 2中的图像处理模块受到了极大重视。

Ergo 2 Edge AI处理器系统示意图,由Perceive提供

具有大量像素的大图像对设备开发人员来说是一个巨大的挑战。在某种意义上,图像识别这一说法并不恰当。AI推理增加价值的大多数用例都要求查看一个感兴趣的区域,或者其中的几个区域,其中相对较少的像素包裹在一个充满大多数无趣像素的大得多的图像中。更快更准确地发现那些感兴趣的区域将决定应用程序的运行状况。

Ergo 2图像处理单元具有双重同时管道,可以隔离感兴趣的像素,使AI模型更容易处理感知。第一个管道支持4个感兴趣的区域,最大图像大小为4672 x 3506像素,每秒24帧(fps)。第二个管道可以以60 fps的速度在2048 x 1536像素的图像中瞄准单个区域。IPU还可以处理图像范围内的任务,如缩放、范围压缩、旋转、失真和镜头阴影校正等。

丢失的帧会影响感知

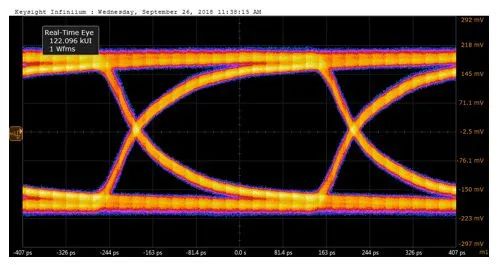

在这些快速、高分辨率的图像中,过多的噪声或抖动会由于数据错误而导致帧丢失。图像流中丢失的帧可能会影响推断操作的准确性,导致错过或不正确的感知。在具有挑战性的环境中,可靠的图像传输是在边缘进行准确感知的必要条件。

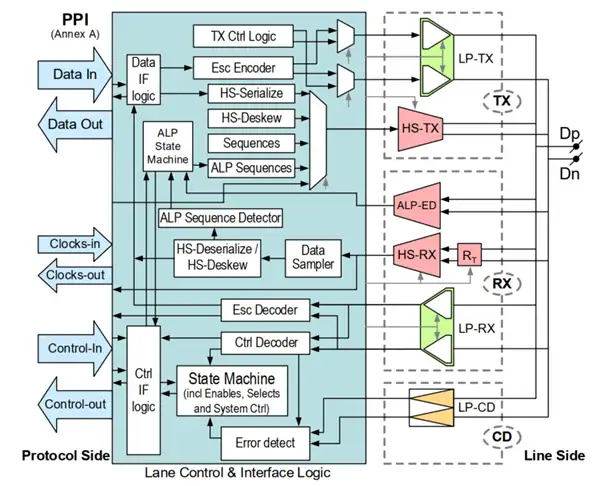

Mixel MIPI D-PHY IP的一个典型特征是其时钟转发同步链路,提供高抗干扰性和高抖动容忍度。在Ergo 2中,有三种不同的MIPI IP解决方案在工作:四通道CSI-2 TX、两通道CSI-2 RX和四通道CSI-2 RX。每个IP块集成了一个发射器或接收器和一个32位的CSI-2控制器核心。链接速度高达2.5 Gbps,下面是典型的眼图。

第一步成功与否是关键

在大型SoC中出现缺陷是很严重的,重新设计可能代价非常高。然而,更大的SoC项目往往有更大的设计团队,更长的时间表和更高的预算。在一个较小的芯片上,一个失败可以扼杀一个项目,调试和重新启动的成本迅速上升到超过最初的开发成本。

尽管在半导体行业中,首次成功并不是必然的,但Perceive能够通过Mixel IP实现这一目标。Mixel支持Perceive的合规性测试,使完整的集成设计能够在SoC转向大批量生产之前承受严格的MIPI接口表征。Mixel MIPI D-PHY IP包含驱动前和驱动后环回和内置的自检功能,用于测试发送和接收接口。

Perceive集成Mixel的MIPI D-PHY IP的结果是达到了Ergo 2的功率、性能和成本目标。反过来,Perceive的客户可以在更小的、功耗有限的设备上实现Ergo 2,其中电池寿命是一个关键指标,但AI推理性能必须不受影响。这是一个很好的例子,通过精心设计的集成,将图像放在芯片上用于AI推理,有助于在小系统级别上节省成本。

审核编辑 :李倩

-

传感器

+关注

关注

2550文章

50944浏览量

752801 -

处理器

+关注

关注

68文章

19229浏览量

229541 -

分辨率

+关注

关注

2文章

1057浏览量

41907 -

人工智能

+关注

关注

1791文章

47072浏览量

238054

原文标题:MIPI D-PHY IP为AI推理带来片上图像

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MIPI D-PHY V3.1问题的解决办法?

Gowin MIPI D-PHY RX TX Advance用户使用指南

Gowin MIPI DPHY的用户指南

对于MIPI系列之“D-PHY”的性能分析和介绍以及应用

MIPI D-PHY的静噪措施

第二代MIPI D-PHY v1.1 IP推出,用于可穿戴设备和物联网显示屏

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

IP_数据表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

IP_数据表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

Arasan宣布立即推出第二代MIPI D-PHY

IP_数据表(I-27):MIPI D-PHY Tx/Rx for TSMC 40nm LP

IP_数据表(I-18):MIPI D-PHY Receiver for TSMC 40nm LP

IP_数据表(I-28):MIPI D-PHY Tx/Rx for Samsung 28nm

MIPI CSI-2 RX Subsystem IP介绍和PHY实现浅谈

聚焦MIPI 系列之四:一文盘点D-PHY/C-PHY/M-PHY之架构与测试解决方案

MIPI D-PHY IP为AI推理带来片上图像

MIPI D-PHY IP为AI推理带来片上图像

评论