创建尽可能灵活的小芯片已经吸引了半导体生态系统的想象力,但来自不同代工厂的小芯片的异构集成将如何发挥作用仍不清楚。

半导体生态系统中的许多公司仍在弄清楚他们将如何适应这个异构的小芯片世界以及他们需要解决哪些问题。虽然几乎每个人都同意小芯片是未来设计的重要组成部分,但仍有许多障碍需要克服。

Rambus产品管理高级总监 Frank Ferro 表示:“大公司一直在使用自己的定制解决方案在内部开展此类技术。” “他们早期意识到的一些优势现在正在引起其他没有资源自己做的公司的兴趣。”

小芯片的优势之一是能够将使用不同制造工艺开发的技术融合在一起。“例如,一个 I/O 芯片可以由一个代工厂制造,核心处理器可以由另一个代工厂制造,然后这些可以放在一个小芯片中,”Ferro 说。“所以从这个意义上说,混合和匹配技术具有潜力。你可以说,‘我从 Foundry A 那里得到了一个很好的价格,我必须与 Foundry B 打交道,但现在我可以将它们混合在一起,’因为小芯片几乎可以被认为是独立的芯片。”

然而,今天,它并不是那么简单。如果多个芯片来自多个地方,第一步是确定每个芯片的引脚间距。

Cadence的 IC 封装和跨平台解决方案产品管理组总监 John Park 表示:“标准封装有一个选项,它具有倒装芯片 125 微米或 130 微米的引脚间距,而不是内插器上的东西。” . “这可能低至 35 微米间距。这是挑战之一。如果引脚间距降至 40 微米或 50 微米,我必须使用硅中介层或某种互连桥来做到这一点。这会增加成本,这也是为什么有标准封装版本的原因,因为如果你把所有东西都放在 125 微米左右的倒装芯片间距上,你可以在传统的层压封装上做到这一点,这比去硅中介层或嵌入式桥接技术。”

Park 说,一旦互连被整理出来,并且封装类型已经确定,放下互连就不是很有挑战性了,因为它类似于需要 45º 角的 PCB 和层压型布线的封装风格。“在某些情况下,需要所有角度。在金属进入焊盘的地方需要圆角。在 [相位] 控制中,差分对必须相互匹配。还需要屏蔽。这些都是 PCB 工具已经完成的事情,而不是做这些巨大的金属片,我们要缩小到一两微米。PCB 工具可以对其进行扩展,因此布线的最大挑战就是所需的时间。在封装中,我们习惯于处理几千个信号连接,尽管电源和地线连接的数量要多得多。

混合晶圆chiplet 生态系统

Synopsys科学家 Mike Borza认为,从长远来看,将会有一个 mixed-foundry chiplet 生态系统。“在那之前,大部分集成系统将由一家供应商提供,而该供应商既是小芯片的制造商,也是整个封装的集成商。”

可能有一些来自外部供应商的具有小功能甚至大功能的特定小芯片。“如果外部小芯片供应商之间存在竞争,则需要对接口进行标准化,或者集成商需要能够处理提供相同接口的不同封装。人们这样做,但这并不方便。为标准功能提供标准引脚输出要方便得多,而且您可以为每个供应商使用相同的节点,”Borza 说。

这就是为什么如此关注 UCIe 标准的原因。“无论您是 Foundry A 还是 Foundry B,都必须遵守封装技术要求,”Synopsys IP 产品线高级组总监 Mick Posner 说。“假设您正在进行基于中介层的高级设计。中介层是连接两个芯片的基板,通常定义特定的引脚间距。如果它们要跨恰好在上面的基板进行封装,那么两个芯片都必须从根本上遵守这一点。也就是说,从理论上讲,没有什么能阻止客户在台积电开发芯片并在另一家代工厂开发芯片,从另一家代工厂拉货并将所有这些封装在一起。这是多管芯系统的主要优势之一。虽然今天大部分工作都是由单一供应商完成的,

Chiplet 封装技术要求

Posner 说,另外一个 chiplet 要求来自封装技术。“有一种有机基质,是的。另一端是中介层。然后中间有一大堆新的封装技术,包括 InFO(TSMC 的集成扇出)、RDL(再分布层)扇出等,所有这些都有自己的路径要求。”

正在开发多线程路由器来应对这些更大的挑战,Cadence 的 Park 指出,进行此类设计的工程团队通常使用 PCB 式路由器进行信号路由。“然后,在许多情况下,如果设计具有复杂的电源结构,就像您在 IC 工具中看到的那样,他们实际上会将这些结构混合在一起,从 IC 工具中获取电源和接地布线,并将其与信号合并路由。因此,这实际上是系统世界和 IC 的融合——它们融合在一起,其中包括您需要的工具和专业知识。但总的来说,布局是由习惯于进行这种样式路由的系统人员完成的。只是现在连接多了很多。这意味着路由方面存在更多瓶颈。”

小芯片还有其他好处。Imperas Software的 CEO Simon Davidmann 说:“如果这些芯片又大又贵,它就可以消除其中一些芯片的风险。”. “说处理器搞砸了。把它取下来,再装一个。这真是一个好处。如果您有 SoC,则无法更改处理器。如果你有一个小芯片,你可以用所有其他块构建一个新的小芯片,它就像印刷电路板一样。如果印刷电路板上有 1,000 个元件,其中一个坏了,你松开它,插入另一个,它就可以工作了。即使在现场出现故障,更换小芯片中的一个芯片仍然比扔掉电路板并重新设计一块新电路板更便宜,如果我所做的只是重新设计那一点点的话。由于小芯片基本上是硬 IP 的大块,所以发生的情况是,如果我正在构建芯片,而不是获得处理器的版本 3,获得芯片,然后必须等待一年并在版本 4 出现时制作新芯片出来,我可以改变小芯片,当一个新块出现时,我可以使用我仍然拥有的所有其余部分。我只是将 chiplet 处理器从 3 更改为 4,然后继续前进。”

至于物理问题,除了需要进行更多模拟和验证之外,Davidmann 认为没有任何实际影响。

新的小芯片挑战

目前,AMD 和英特尔等大公司使用内部设计的小芯片,基本上将 SoC 或 ASIC 分解为不同的功能。

西门子高级封装解决方案总监 Tony Mastroianni 表示:“要做到这一点,由于没有小芯片生态系统,他们需要同时进行多个芯片设计,因为所有这些芯片都需要设计为协同工作以构建一个完整的系统。”数字产业软件. “如果它是一个大型 ASIC,你将它分解成分层块。可重复使用的 IP 主要用于您的模拟和高速 I/O。使用 chiplet,现在您可以将“超级 ASIC”分解为更小的 chiplet,但您不一定必须使用相同的过程,您可以利用它来发挥自己的优势。如果你有一个大处理器,你可以使用 5nm 或 3nm 工艺。如果你有模拟/混合信号,你可以使用一个更便宜的过程,在这方面效果更好。也可能有专门的 IP 只能在非常昂贵的节点中使用。如果你只需要一个接口,为什么不把它构建到一个小芯片中呢?”

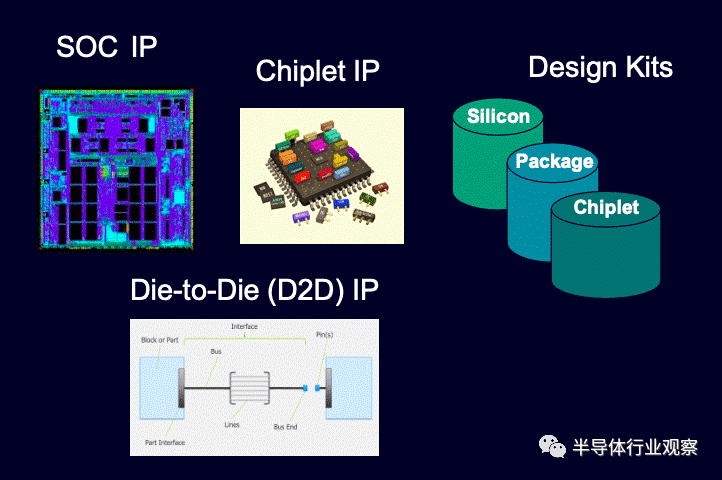

图 1:chiplet 生态系统中的 IP

但当涉及到由不同代工厂开发的小芯片时,情况就大不相同了。“你必须考虑这些标准,并确保获得所有正确的电压,”Mastroianni 说。“即使它来自同一个代工厂,你也必须担心这一点,因为它们的批次不同,所以根据定义,它们是两种不同的芯片。这意味着有不同的角落,无论如何你都必须处理它。如果它们是在不同的工艺上制造的,那将使其更具挑战性。其中很多是通过 die-to-die 接口处理的——几乎就像一个 SerDes 接口——将它解耦,这些接口被设计成那样。它更多的是其他信号的问题,比如可能需要一些连接的低速 I/O,所以你必须担心它。但通常,这些接口并不那么重要。这些标准协议涵盖了高速 I/O。”

虽然 3D 设计有很多进展,但尚不清楚这对商业小芯片是否有意义。“在 3D 中,布局布线工具将能够支持不同的技术,”他说。“他们将处理这个问题,这是一个非常 IC、以布局布线为中心的流程。无论您是否甚至需要为将要放在一起的每个小芯片建立模型,它们实际上都将作为一个整体设计在一起。你可能有一个可以作为小芯片出售的标准,但那将是个例外。”

今天,今天大多数小芯片活动都在2.5D中。“你可能在中介层和其他 ASIC 上有多个 3D 芯片,因为同样,即使你有 3D,由于热限制,你可以堆叠的数量也有实际限制,”Mastroianni 说。“当你把它们叠起来时,你不得不担心热量。这是更大的挑战之一,同时受制于十字线尺寸。然而,您可以使用中介层或有机基板超越这一点。”

芯片/小芯片/系统架构师如何与封装技术团队和 ASIC 设计团队合作,以确定不同技术中可用的 IP 是小芯片设计的另一个重要方面。

“与 ASIC 设计相比,需要更多的架构规划,一旦你有了 ASIC 和规格,你只需转动曲柄,就可以做你的芯片了。小芯片不同。那里还涉及其他步骤。尽管如此,一旦你设计了 3D 芯片,它仍然可以作为小芯片重新使用。它只是一个三高或四高的小芯片,就像在 HBM 中一样。在那里,您将需要将所有内容集成到一个封装中,”他说。

Chiplet 通信

一个 chiplet 究竟如何与另一个 chiplet 通信是另一个需要解决的挑战,尤其是对于由多个代工厂开发的 chiplet。这是许多标准工作的重点所在。

Intrinsic ID 的首席执行官 Pim Tuyls 说:“如果你不能与来自其他地方的小芯片进行通信,你就无法对它做任何事情。”“然后你需要另一个芯片,将一种类型的通信转换为另一种通信,这只会让它变得更加复杂。它并没有因此变得不那么复杂。与此相关的是安全。如果没有钩子和角,就无法保证安全。例如,如果小芯片没有公钥加密机制,您将无能为力。有时您可以使用软件进行修复,但您必须为此做好准备。小芯片的通信和安全级别的标准化将变得非常非常重要。”

是德科技首席应用开发工程师兼科学家 Matthew Ozalas表示,理想情况下,每个小芯片都被视为对物理封装不敏感的独立块。然而,这并不总是一种选择。

“例如,彼此靠近的小芯片可能会以热、电磁或其他物理方式相互作用,”Ozalas 解释道。“要对此类交互进行建模,您需要对小芯片内部的布局结构进行分析。代工厂已经在创建复杂的封装模型,但这些封装流程目前基于所有 IP 都包含在代工厂的“保护伞”中的假设。如果有来自多个代工厂的小芯片,更高级别的组装和分析可能成为主要的绊脚石。电路、布局和基板的复杂模型都被认为是敏感的。因此,标准化需要在小芯片内实现低层结构的协同仿真,同时通过适当的加密保护每个代工厂的个人 IP。除了这些 IP 和多物理问题之外,还有更传统的基于布局的组装挑战,例如不同的堆叠、连接和跨小芯片的验证,这些问题也必须以标准化的方式处理。”

但多代工厂方法的开发速度还有待观察。Flex Logix首席执行官 Geoff Tate对生态系统充满信心,但表示最初的实施将主要来自同一代工厂。“他们将采用不同的KGD方法,机械规格将不同,如果多小芯片设备上有一个,谁愿意自己弄清楚问题是什么,”他说。“很可能小芯片目前只会在一个代工厂的生态系统中使用。台积电可能愿意混合来自多个工艺节点的自己设计/工艺的小芯片,因为他们了解即将到来的元素并希望最终客户的业务。”

Tate补充说,这一切都不会在一夜之间发生。“没有一套标准的小芯片可用于标准化接口,”他说。没有标准化的方法来测试和保证 chiplet 的制造可靠性(高温和低温测试已在芯片中得到验证,但正在为 chiplet 开发)。没有一套经过验证的自动化设计工具可以将小芯片集成到基板上。没有一个供应商生态系统可以集成来自多个供应商的小芯片。一个供应商不信任另一个供应商的流程。来自不同工艺的小芯片将具有不同的热膨胀系数,从而导致机械可靠性问题/担忧。如果组装好的基板不起作用,谁拥有问题?在经过验证的生态系统发展起来并且基板成本下降之前,小芯片对于主流来说是不实用的,”Tate 补充道。

结论

小芯片即将到来。问题是小芯片的采购速度有多快、范围有多广,以及理想的应用是什么。

可以肯定的是,设计和制造的各种过程中并没有解决所有问题,使公司能够从选项菜单中进行选择,将这些设备集成到系统中,并确信它会按预期工作。这需要时间。但这个方向已经牢牢确立——并被一些最大的芯片制造商证明是行之有效的——即使尚不清楚半导体行业的其他公司何时或如何到达那里,以及在此过程中会遇到什么样的问题。

审核编辑 :李倩

-

封装技术

+关注

关注

12文章

547浏览量

67981 -

生态系统

+关注

关注

0文章

702浏览量

20723 -

chiplet

+关注

关注

6文章

430浏览量

12582

原文标题:Chiplet的新竞赛

文章出处:【微信号:光刻人的世界,微信公众号:光刻人的世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cadence推出基于Arm的系统Chiplet

Chiplet技术有哪些优势

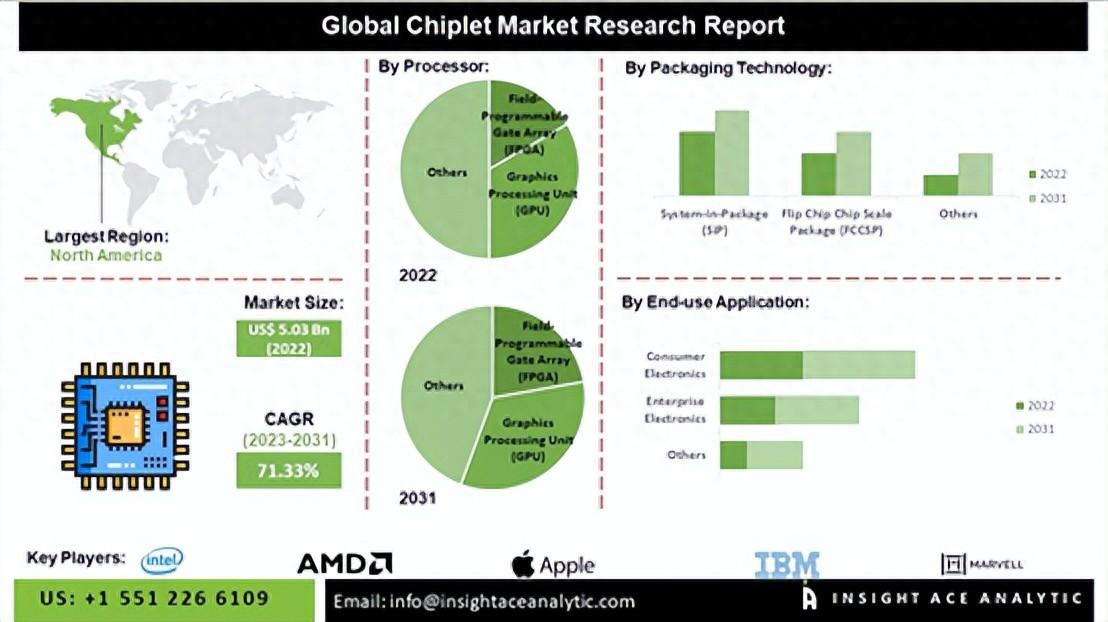

2035年Chiplet市场规模将超4110亿美元

IMEC组建汽车Chiplet联盟

Primemas选择Achronix eFPGA技术用于Chiplet平台

2031年全球Chiplet市场预测

前景一片大好的Chiplet,依然存在门槛问题

Chiplet是否也走上了集成竞赛的道路?

什么是Chiplet技术?

Chiplet技术对英特尔和台积电有哪些影响呢?

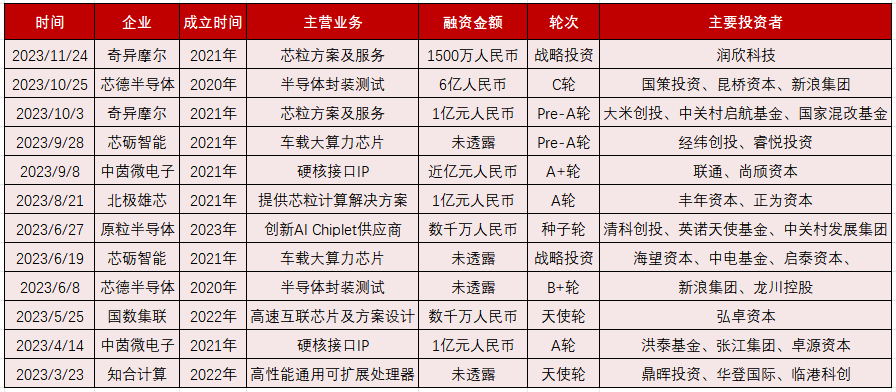

2023年Chiplet发展进入新阶段,半导体封测、IP企业多次融资

Chiplet的新竞赛

Chiplet的新竞赛

评论