一博高速先生成员:刘春

在进行PCB设计时,相信有经验的工程师都遇到过这种情况,在布线过程中,有时候由于电路结构或空间限制,需要中途某段走线变粗或变细,如串接电阻电容、下孔、BGA出线区域或走线密集区域等,但这样做的结果就导致信号走线阻抗不连续,严重的甚至会影响信号的质量。那么当面临这类情况时,我们该如何更好的去把控好设计以避免或减小对信号质量造成影响呢?

本文将利用SIGRITY仿真软件对信号在传输线上出现一段串联走线阻抗突变的情况进行仿真分析,了解串联走线阻抗突变的情况是如何影响信号质量的,方便我们在设计中遇到类似阻抗突变时能游刃有余的顺利完成设计。

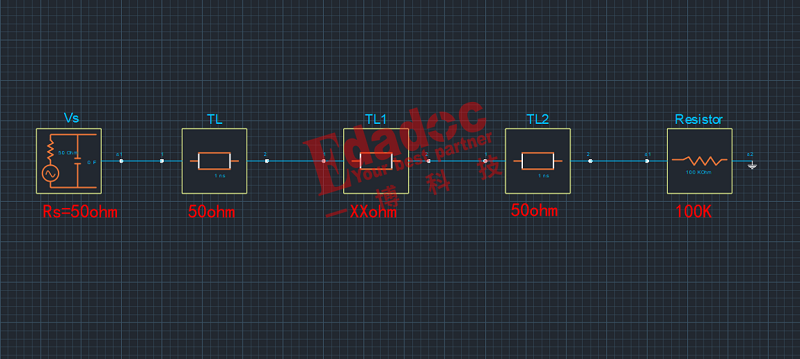

搭建简易的仿真拓扑如下图所示:

其中激励源Vs的内阻为50ohm,TL,TL2均为50ohm阻抗,延时1ns的均匀传输线,TL1作为变量,模拟在PCB布线时发生阻抗突变的线段,负载Resistor为100K的电阻相当于开路端接。

为了让我们更直观的了解在传输线路中串联走线阻抗突变对信号的影响,基于上面搭建的仿真拓扑设置如下:

激励源Vs设置幅度为1V的理想方波;

TL1设置阻抗为30ohm,延时0.2ns;

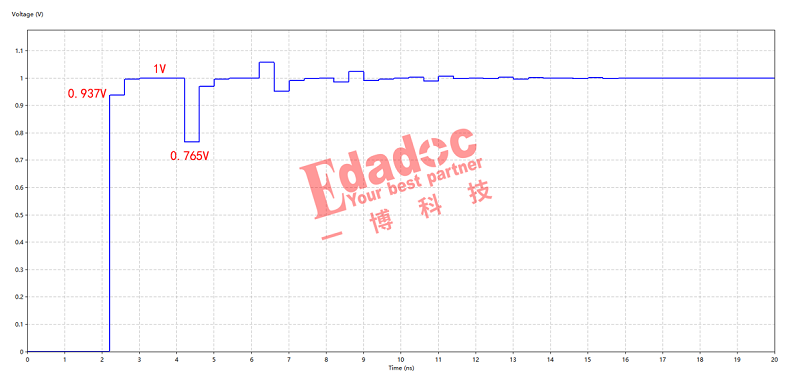

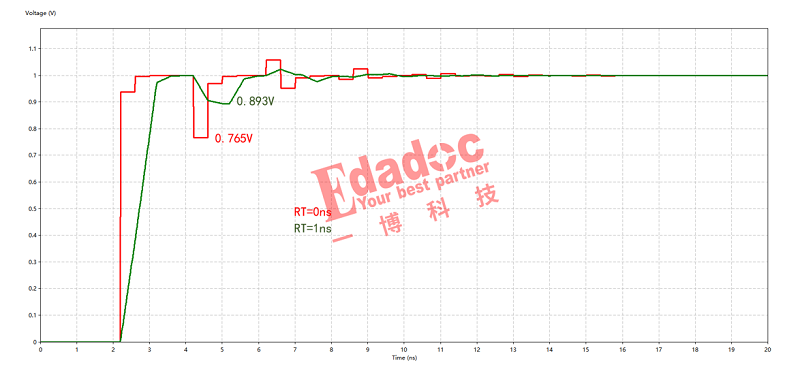

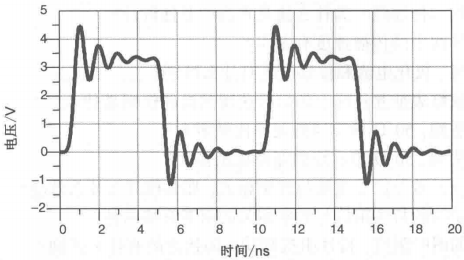

仿真结果:

根据仿真结果我们可以看到,在当前模型配置下,信号最差时电平幅度跌到了0.765V,已经严重影响了信号的质量。为了更方便大家理解该突变对信号的影响,我们还可以用反射原理进行计算分析,看是否和我们的仿真结果相吻合。这里关于反射理论的知识就不再阐述,感兴趣的朋友可以关注高速先生前几期的文章,里面有详细的描述哈!

分析如下:

0ns:

第一次反射,激励源内阻分压,A点电压0.5V;

1ns:

第二次反射,B点分界,反射系数-0.25,TL1传输线上电压0.375V;

1.2ns:

第三次反射,C点分界,反射系数0.25,TL2传输线上电压0.46875V;

2.2ns:

第四次反射,D点分界,反射系数1,负载接受电压电压0.937V;

4.2ns:

由负载反射回去的电压在C点分界再反射回来,受反射的影响,此时负载接收到的电压变为0.765V;

……

可见仿真结果与我们计算分析结果是相吻合的。

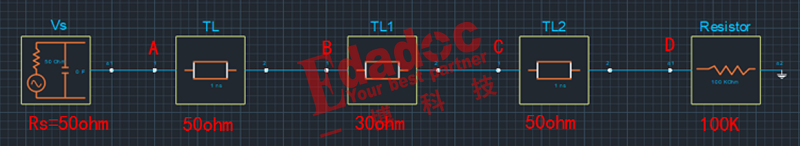

通过上面的仿真例子和分析,相信大家对传输线中串联走线阻抗突变是如何影响信号质量的原理都有一定的了解了哈!下面我们再来仿真一下其他阻抗突变的情况,观察是否能发现一些有价值的规律。同样基于搭建的仿真拓扑设置如下:

激励源Vs设置幅度为1V的理想方波;

TL1设置阻抗分别为30,40,50,60,70ohm,延时0.2ns;

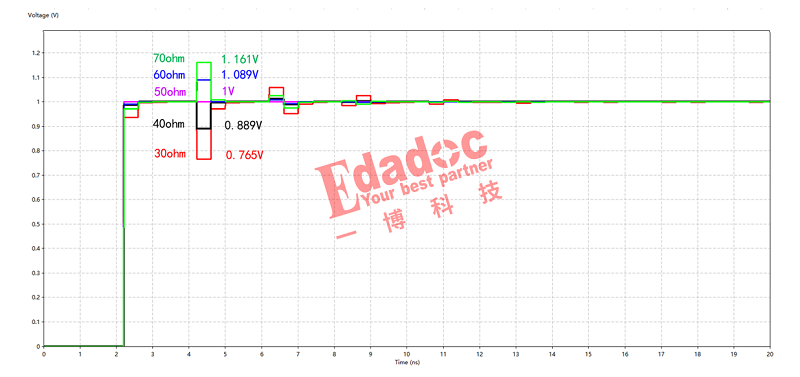

仿真结果:

从仿真结果来看,我们可以知道当串联走线阻抗突变越大,对信号质量的影响也就越大。因此在PCB布线时,要尽可能的保证传输线阻抗连续或减小阻抗的突变程度。

当然,上面的仿真研究都是基于不存于现实的理想方波的,接下来我们来看看信号上升时间不为0时又是怎样的?同样基于搭建的仿真拓扑设置如下:

激励源Vs设置幅度为1V,上升时间RT=1ns的脉冲;

TL1设置阻抗为30ohm,延时0.2ns;

仿真结果与理想方波仿真结果比较:

根据仿真结果可知,当信号上升时间为1ns时,最差的信号电平为0.893V,信号质量相较于理想方波的0.765V有了明显的改善,那是否可认为传输线上串联走线阻抗突变对信号质量的影响和信号的上升边有关呢?接下来我们继续做进一步仿真验证,观察之间是否存在关联。同样基于搭建的仿真拓扑设置如下:

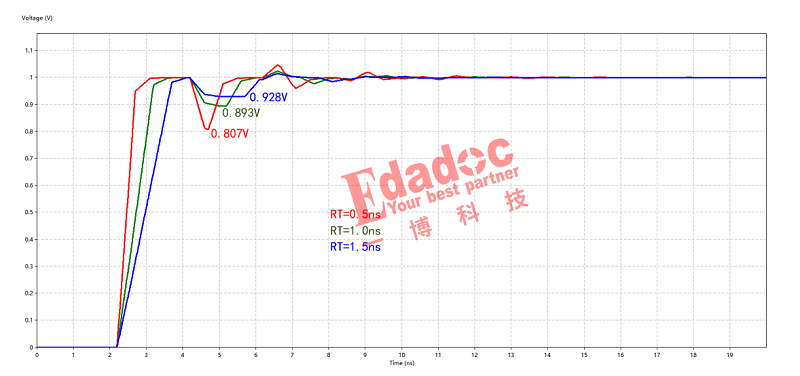

激励源Vs设置幅度为1V,上升时间RT分别设置为0.5ns,1ns,1.5ns的脉冲;

TL1设置阻抗为30ohm,延时0.2ns;

仿真结果:

仿真结果显示,

RT=0.5ns时,信号最差电平0.807V;

RT=1.0ns时,信号最差电平0.893V;

RT=1.5ns时,信号最差电平0.928V。

可知,当信号的上升时间越长,串联走线阻抗突变段对信号质量的影响越小,信号质量就越好。因为阻抗突变段前后分界的反射是大小相等,方向相反的,在经历两倍的突变延时后会相互抵消,可是在没抵消之前这两倍的延时内信号质量受反射影响会变差,但如果信号的上升时间足够大,就能够把该影响给减弱甚至几乎完全掩盖掉。

然而在实际设计中,我们信号的上升时间基本都是固定的,除了减小阻抗的突变之外还有哪些因素可以帮助我们去改善突变线段对信号质量的影响呢?

相信大家都已经猜到了哈!那就是我们阻抗突变段的长度,即信号在阻抗突变段传输时的延时大小。话不多说,我们直接来看仿真验证吧!同样基于搭建的仿真拓扑设置如下:

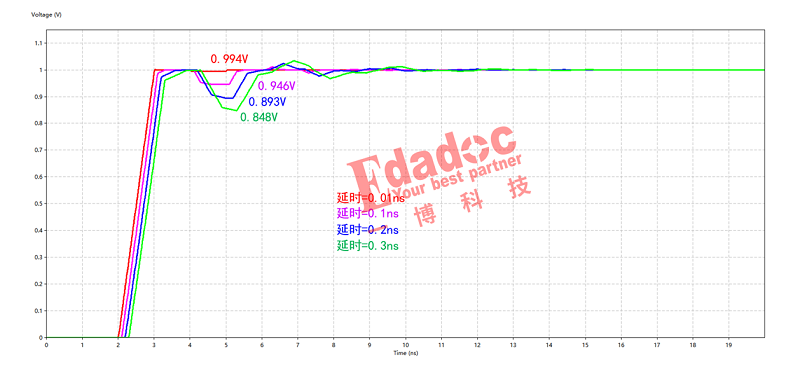

激励源Vs设置幅度为1V,上升时间RT=1ns的脉冲;

TL1设置阻抗为30ohm,延时分别为0.01ns,0.1ns,0.2n,0.3ns;

仿真结果:

仿真结果显示,

延时=0.01ns时,信号最差电平0.994V;

延时=0.1ns时,信号最差电平0.946V;

延时=0.2ns时,信号最差电平0.893V;

延时=0.3ns时,信号最差电平0.848V。

说明,阻抗突变段的长度越长,串联走线阻抗突变段对信号质量的影响越大,当突变长度足够短时,影响可以忽略不计。这与信号上升时间越大,串联走线阻抗突变段对信号质量的影响越小是同样的原理。

最后,综合上面的仿真结果和分析,我们可以对串联走线阻抗突变对信号质量的影响做如下总结:

(1)串联走线阻抗突变越大,对信号质量的影响也就越大。因此在进行PCB布线设计时,我们的串联走线阻抗突变应尽可能的小;

(2)信号的上升时间越长,串联走线阻抗突变段对信号质量的影响越小,即信号质量就越好。

(3)阻抗突变段的长度越长,串联走线阻抗突变段对信号质量的影响越大,当突变长度足够短时,影响可以忽略不计。因此在进行布线设计时,我们应该把走线的阻抗突变段尽可能的控制在较短的长度内,当然,具体的长度还要结合对应信号的上升时间进行评估。

审核编辑:汤梓红

-

电路板

+关注

关注

140文章

5009浏览量

99316 -

阻抗

+关注

关注

17文章

961浏览量

46359 -

仿真

+关注

关注

50文章

4136浏览量

134185 -

信号

+关注

关注

11文章

2812浏览量

77230 -

PCB

+关注

关注

1文章

1835浏览量

13204

发布评论请先 登录

相关推荐

链路上小段线的阻抗突变到底会不会影响信号质量?

链路上小段线的阻抗突变到底会不会影响信号质量?

评论