1、什么是嵌入式

IEEE(Institute of Electrical and Electronics Engineers,美国电气和电子工程师协会)对嵌入式系统的定义:“用于控制、监视或者辅助操作机器和设备的装置”。原文为:Devices Used to Control,Monitor or Assist the Operation of Equipment,Machinery or Plants)。

嵌入式系统是一种专用的计算机系统,作为装置或设备的一部分。通常,嵌入式系统是一个控制程序存储在ROM中的嵌入式处理器控制板。事实上,所有带有数字接口的设备,如手表、微波炉、录像机、汽车等,都使用嵌入式系统,有些嵌入式系统还包含操作系统,但大多数嵌入式系统都是由单个程序实现整个控制逻辑。

从应用对象上加以定义,嵌入式系统是软件和硬件的综合体,还可以涵盖机械等附属装置。国内普遍认同的嵌入式系统定义为:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗等严格要求的专用计算机系统。

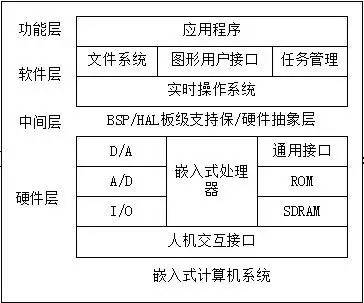

一个嵌入式系统装置一般都由嵌入式计算机系统和执行装置组成,嵌入式计算机系统是整个嵌入式系统的核心,由硬件层、中间层、系统软件层和应用软件层组成。执行装置也称为被控对象,它可以接受嵌入式计算机系统发出的控制命令,执行所规定的操作或任务。执行装置可以很简单,如手机上的一个微小型的电机,当手机处于震动接收状态时打开;也可以很复杂,如SONY 智能机器狗,上面集成了多个微小型控制电机和多种传感器,从而可以执行各种复杂的动作和感受各种状态信息。

2、嵌入式系统的组成

一、 硬件层 硬件层中包含嵌入式微处理器、存储器(SDRAM、ROM、Flash等)、通用设备接口和I/O接口(A/D、D/A、I/O等)。在一嵌入式处理器基础上添加电源电路、时钟电路和存储器电路,就构成了一个嵌入式核心控制模块。其中操作系统和应用程序都可以固化在ROM中.

二、 中间层 硬件层与软件层之间为中间层,也称为硬件抽象层(Hardware Abstract Layer,HAL)或者板级支持包(Board Support Package,BSP),它半系统上层软件与底层硬件分离开来,使系统的底层驱动程序与硬件无关,上层软件开发人员无需关心底层硬件的具体情况,根据BSP层提供的接口即可进行开发。该层一般包含相关底层硬件的初始化、数据的输入/输出操作和硬件设备的配置功能。 实际上,BSP是一个介于操作系统和底层硬件之间的软件层次,包括了系统中大部分与硬件联系紧密的软件模块。设计一个完整的BSP需要完成两部分工作:嵌入工系统的硬件初始化的BSP功能,设计硬件相关的设备驱动。

三、 系统软件层 系统软件层由实时多任务操作系统(Real-time Operation System,RTOS)、文件系统、图形用户接口(Graphic User Interface,GUI)、网络系统及通用组件模块组成。RTOS是嵌入式应用软件的基础和开发平台。

3、实时系统

(1)定义:能在指定或确定的时间内完成系统功能和对外部或内部、同步或异步时间做出响应的系统。

(2)区别:通用系统一般追求的是系统的平均响应时间和用户的使用方便;而实时系统主要考虑的是在最坏情况下的系统行为。

(3)特点:时间约束性、可预测性、可靠性、与外部环境的交互性。

(4)硬实时(强实时):指应用的时间需求应能够得到完全满足,否则就造成重大安全事故,甚至造成重大的生命财产损失和生态破坏,如:航天、军事。

(5)软实时(弱实时):指某些应用虽然提出了时间的要求,但实时任务偶尔违反这种需求对系统运行及环境不会造成严重影响,如:监控系统、实时信息采集系统。

(6)任务的约束包括:时间约束、资源约束、执行顺序约束和性能约束。

5、实时系统的调度

(1)调度:给定一组实时任务和系统资源,确定每个任务何时何地执行的整个过程。

(2)抢占式调度:通常是优先级驱动的调度,如uCOS。优点是实时性好、反应快,调度算法相对简单,可以保证高优先级任务的时间约束;缺点是上下文切换多。

(3)非抢占式调度:通常是按时间片分配的调度,不允许任务在执行期间被中断,任务一旦占用处理器就必须执行完毕或自愿放弃,如WinCE。优点是上下文切换少;缺点是处理器有效资源利用率低,可调度性不好。

(4)静态表驱动策略:系统在运行前根据各任务的时间约束及关联关系,采用某种搜索策略生成一张运行时刻表,指明各任务的起始运行时刻及运行时间。

(5)优先级驱动策略:按照任务优先级的高低确定任务的执行顺序。

(6)实时任务分类:周期任务、偶发任务、非周期任务。

(7)实时系统的通用结构模型:数据采集任务实现传感器数据的采集,数据处理任务处理采集的数据、并将加工后的数据送到执行机构管理任务控制机构执行。

5、嵌入式微处理器体系结构

(1)冯诺依曼结构:程序和数据共用一个存储空间,程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置,采用单一的地址及数据总线,程序和数据的宽度相同。例如:8086、ARM7、MIPS…

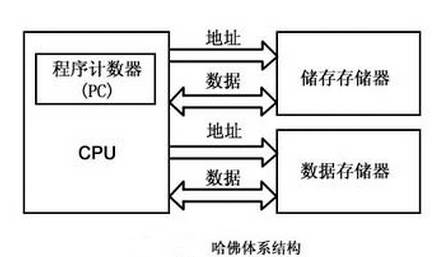

(2)哈佛结构:程序和数据是两个相互独立的存储器,每个存储器独立编址、独立访问,是一种将程序存储和数据存储分开的存储器结构。例如:AVR、ARM9、ARM10…

(3)CISC与RISC的特点比较。

计算机执行程序所需要的时间P可以用下面公式计算:

P=I×CPI×T

I:高级语言程序编译后在机器上运行的指令数。

CPI:为执行每条指令所需要的平均周期数。

T:每个机器周期的时间。

(4)流水线的思想:在CPU中把一条指令的串行执行过程变为若干指令的子过程在CPU中重叠执行。

(5)流水线的指标:

吞吐率:单位时间里流水线处理机流出的结果数。如果流水线的子过程所用时间不一样长,则吞吐率应为最长子过程的倒数。

建立时间:流水线开始工作到达最大吞吐率的时间。若m个子过程所用时间一样,均为t,则建立时间T=mt。

(6)信息存储的字节顺序

A、存储器单位:字节(8位)

B、字长决定了微处理器的寻址能力,即虚拟地址空间的大小。

C、32位微处理器的虚拟地址空间位232,即4GB。

D、小端字节顺序:低字节在内存低地址处,高字节在内存高地址处。

E、大端字节顺序:高字节在内存低地址处,低字节在内存高地址处。

F、网络设备的存储顺序问题取决于OSI模型底层中的数据链路层。

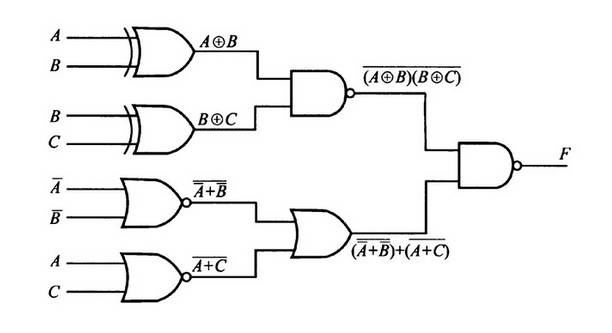

6、逻辑电路基础

(1)根据电路是否具有存储功能,将逻辑电路划分为:组合逻辑电路和时序逻辑电路。

(2)组合逻辑电路:电路在任一时刻的输出,仅取决于该时刻的输入信号,而与输入信号作用前电路的状态无关。常用的逻辑电路有译码器和多路选择器等。

(3)时序逻辑电路:电路任一时刻的输出不仅与该时刻的输入有关,而且还与该时刻电路的状态有关。因此,时序电路中必须包含记忆元件。触发器是构成时序逻辑电路的基础。常用的时序逻辑电路有寄存器和计数器等。

(4)真值表、布尔代数、摩根定律、门电路的概念。

(5)NOR(或非)和NAND(与非)的门电路称为全能门电路,可以实现任何一种逻辑函数。

(6)译码器:多输入多输出的组合逻辑网络。

每输入一个n位的二进制代码,在m个输出端中最多有一个有效。

当m=2n是,为全译码;当m《2n时,为部分译码。

(7)由于集成电路的高电平输出电流小,而低电平输出电流相对比较大,采用集成门电路直接驱动LED时,较多采用低电平驱动方式。液晶七段字符显示器LCD利用液晶有外加电场和无外加电场时不同的光学特性来显示字符。

(8)时钟信号是时序逻辑的基础,它用于决定逻辑单元中的状态合适更新。同步是时钟控制系统中的主要制约条件。

(9)在选用触发器的时候,触发方式是必须考虑的因素。触发方式有两种:

方式1:电平触发方式:具有结构简单的有点,常用来组成暂存器。

方式2:边沿触发方式:具有很强的抗数据端干扰能力,常用来组成寄存器、计数器等。

-

嵌入式系统

+关注

关注

41文章

3839浏览量

134023 -

接口

+关注

关注

33文章

9630浏览量

157762 -

ROM

+关注

关注

4文章

579浏览量

89457 -

计算机系统

+关注

关注

0文章

293浏览量

25366

发布评论请先 登录

嵌入式系统知识和接口技术合集1

嵌入式系统知识和接口技术合集1

评论