UVM中所有的对象都应该在factory 中注册, utility 宏就是用于将对象注册到工厂的。

Utility Macros

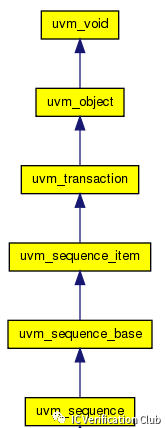

utils宏主要用于将object或 component 注册到工厂,它需要在每个从uvm_object派生的用户定义类中使用,包括所有类型的sequenceitems 和 components 。

ObjectUtility

所有直接从uvm_object或uvm_transaction派生的类都需要使用`uvm_object_utils宏进行注册。对于每个类,都必须显式定义new函数,并将类实例的名称作为参数。

class ABC extends uvm_object;

// Register this user defined class with the factory

`uvm_object_utils(ABC)

function new(string name = "ABC");

super.new(name);

endfunction

endclass

Component Utility

所有直接或间接从uvm_component派生的类都需要使用`uvm_component_utils宏将它们注册到工厂。对于每个直接或间接从uvm_component派生的类,都必须显式定义new函数,并将类实例的名称和实例化此对象的父类的句柄作为参数。

class DEF extends uvm_component;

// Class derived from uvm_component, register with factory

`uvm_component_utils(DEF)

function new(string name = "DEF", uvm_component parent=null);

super.new(name, parent);

endfunction

endclass

factory注册后的类对象创建

建议通过调用type_id::create()方法来创建所有类对象已促进验证平台的灵活性和可重用性。

class ABC extends uvm_object;

`uvm_object_utils(ABC)

function new(string name = "ABC");

super.new(name);

endfunction

endclass

class base_test extends uvm_test;

`uvm_component_utils(base_test)

function new(string name = "base_test", uvm_component parent=null);

super.new(name, parent);

endfunction

virtual function void build_phase(uvm_phase phase);

// An object of class "ABC" is instantiated in UVM by calling

// its "create()" function which has been defined using a macro

// as shown above

ABC abc = ABC::create("abc_inst");

endfunction

endclass

审核编辑:汤梓红

-

函数

+关注

关注

3文章

4345浏览量

62933 -

UVM

+关注

关注

0文章

182浏览量

19225 -

类对象

+关注

关注

0文章

3浏览量

1470

原文标题:UVM中的utility宏

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IC验证之UVM常用宏汇总分析(四)

IC验证"一个简单的UVM验证平台"是如何搭建的(六)

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

数字IC验证之“搭建一个可以运行的uvm测试平台”(5)连载中...

什么是uvm?uvm的特点有哪些呢

谈谈UVM中的uvm_info打印

UVM中seq.start()和default_sequence执行顺序

我的第一个UVM代码——Hello world

UVM中uvm_config_db机制背后的大功臣

如何用Verdi查看UVM环境中的变量?

UVM中的utility宏

UVM中的utility宏

评论