声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

mcu

+关注

关注

146文章

17272浏览量

352093 -

AXI总线

+关注

关注

0文章

66浏览量

14293

原文标题:考考你:AXI3与AXI4写响应的依赖区别

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何使用AXI VIP在AXI4(Full)主接口中执行验证和查找错误

在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在

发表于 07-08 09:31

•3006次阅读

看看在SpinalHDL中AXI4总线互联IP的设计

。writeIssuingCapability:指明AXI4总线写最大同时支持的指令个数。combinedIssuingCapability:其值应不小于前两者,用于在AXI4总线读写地址通道共用的场景

发表于 08-02 14:28

看看Axi4写通道decoder的设计

读写分离的设计在Axi4总线中,读和写通道是完全相互独立,互不干扰。故而无论是在设计Decoder还是Arbiter时,均可以采用读写分离的方式。如前文所述,SpinalHDL在基于Axi4总线

发表于 08-03 14:27

一文详解ZYNQ中的DMA与AXI4总线

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过

何谓 AXI?关于AXI3/AXI4的相关基础知识

新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。 本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。首先,我们将从一些通俗易懂的知识、理论

ZYNQ中DMA与AXI4总线

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的

深入AXI4总线一握手机制

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

发表于 03-17 21:40

•25次下载

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

发表于 06-21 15:21

•2373次阅读

漫谈AMBA总线-AXI4协议的基本介绍

本文主要集中在AMBA协议中的AXI4协议。之所以选择AXI4作为讲解,是因为这个协议在SoC、IC设计中应用比较广泛。

发表于 01-17 12:21

•2481次阅读

SoC设计中总线协议AXI4与AXI3的主要区别详解

AXI4和AXI3是高级扩展接口(Advanced eXtensible Interface)的两个不同版本,它们都是用于SoC(System on Chip)设计中的总线协议,用于处理器和其它外设之间的高速数据传输。

AMBA AXI4接口协议概述

AMBA AXI4(高级可扩展接口 4)是 ARM 推出的第四代 AMBA 接口规范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 凭借半导体产业首个符合 AXI4 标准的

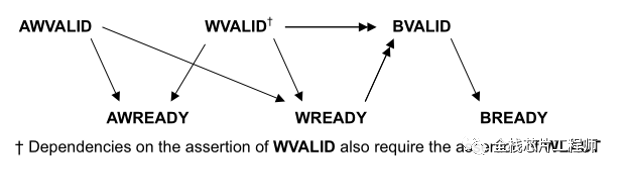

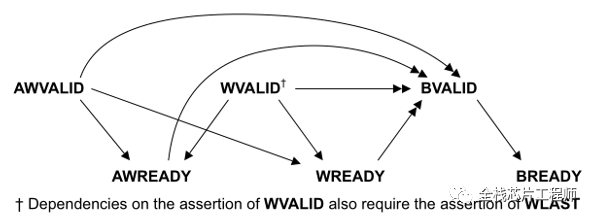

AXI3与AXI4写响应的依赖区别

AXI3与AXI4写响应的依赖区别

评论