在综合和功耗优化过程中,可能会不知不觉地引入许多 CDC 错误。综合过程可能带来的 CDC 问题包括:

• CDC 路径中出现新的易发生毛刺的组合逻辑

• 由于插入电源、测试或安全逻辑而产生的新 CDC路径

• 由于逻辑优化,现有 CDC 同步结构可能会被破坏

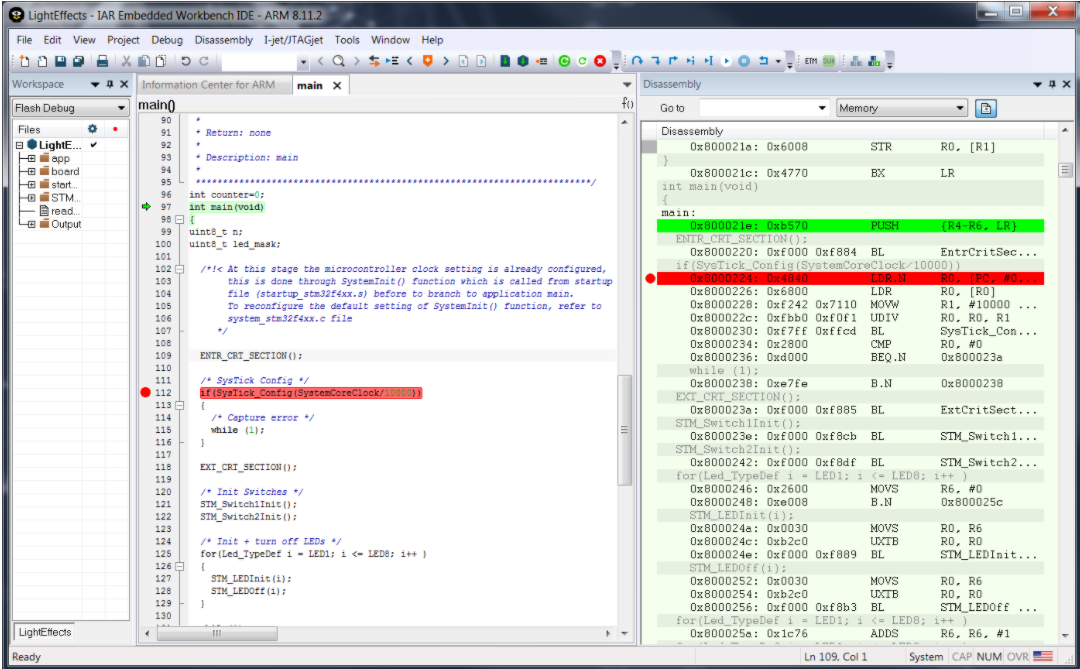

因此,CDC 验证不仅在 RTL 有必要,在门级也必不可少。在 RTL,重点是通过识别 CDC 结构和方案来确定时钟域和 CDC 路径。在门级,具有多路复用器或组合逻辑的 CDC 路径常常容易出现毛刺缺陷,在综合、时序和功耗优化过程中可能会引入这些缺陷。如果仅在 RTL 进行 CDC 验证,则此类毛刺缺陷很容易被遗漏,导致代价高昂的流片后芯片失效。根据我们在客户多个项目中部署 Questa Signoff CDC 的经验,我们了解到:

1. 不同类型的 CDC 路径都可能产生潜在毛刺。必须清楚地识别毛刺,以便能够创建算法来有效地予以分析。

2. 门级 CDC 分析费时很长(从几小时到几天)。如果必须进行细微改进,从最后一步重新开始比从头重新开始效率要高得多。

3. 随着设计复杂性不断增加,支持异构层次化方法至关重要。与此同时,随着内存消耗持续增长,识别进程中的并行性并采取分而治之的策略会很有用。

本文首先说明各种类型 CDC 路径中的毛刺问题,然后概述一种基于形式化的自动毛刺检测方法。该方法利用结构 CDC 分析、表达式分析和形式化方法来消除和证明设计中的真正毛刺。为了处理运行时间更长、更复杂的设计,我们将先前的方法分解为一个更灵活的层次化、多阶段和多处理流程。本文说明了该流程的各个阶段以及如何实现并行处理。

编辑:黄飞

-

RTL

+关注

关注

1文章

385浏览量

59809 -

CDC

+关注

关注

0文章

57浏览量

17815

原文标题:避免 CDC 路径上的毛刺噩梦

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电感元件的各种类型及其常见用法讨论

如何辨别各种类型的接口

C51各种类型的大小

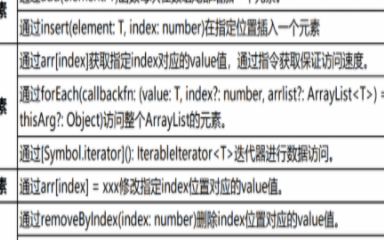

方舟开发框架中容器类的各种类型

各种类型CDC路径中的毛刺问题

各种类型CDC路径中的毛刺问题

评论