串行器-解串器对可减少高带宽、短距离数据通信应用中的互连布线,例如电信和网络设备背板、3G 手机基站机架内连接和数字视频接口。电流模式LVDS信号提供简化的端接、低发射功率和低EMI。

主要的LVDS标准TIA/EIA-644-A规定了信号电平等物理层参数,但没有规定数据速率与电缆长度等互连性能。该标准为用户提供了LVDS信令的基本兼容性,但在高数据速率应用中需要补充有关给定电缆类型和长度可实现的性能的信息。

本文介绍了MAX9205/MAX9207 LVDS串行器和MAX9206/MAX9208解串器在不同数据速率和电缆长度下的误码比(BER)性能的实验室测试结果和分析。本文还将BER与链路眼图上测量的抖动相关联。

Maxim MAX9205/MAX9207 LVDS串行器和MAX9206/MAX9208 LVDS解串器设计用于通过串行点对点链路传输高速数据,具有100Ω差分特性阻抗。MAX160–MAX400对的串行“有效负载”数据速率(不包括开销同步位)为9205Mbps至9206Mbps,MAX400–MAX600对为9207Mbps至9208Mbps。两者具有相同的引脚排列,但每对引脚都针对不同频率范围内的工作进行了优化。研究了使用各种长度的非屏蔽双绞线CAT-5E电缆的BER和眼图抖动。

为了衡量链路的可靠性,误码率测试是最直接和准确的衡量标准。数字通信链路需要非常低的误差率,大约为千亿个接收比特中的一个误差(误码率为10-12) 或更少。

但是,要进行误码率测试,需要高性能信号发生器和专用测试设备,并且误码率测试非常耗时。根据传输速率,传输测试 BER 10 所需的位数可能需要数小时甚至数天-12或更少。由于BER测试的耗时性,通常采用更快的措施来预测链路可靠性。一种是建立产生低 BER 的抖动电平。MAX9205–MAX9206和MAX9207–MAX9208链路的抖动(图3中称为“边际抖动”)由测量结果测量,并与BER相关。误码率测试用于验证数据手册抖动最大值。

测试设置

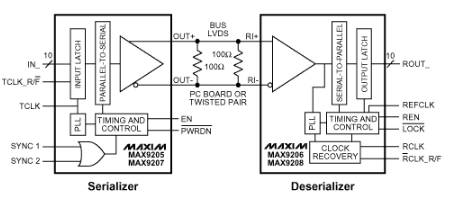

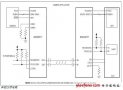

LVDS信号由MAX9205或MAX9207 LVDS串行器传输。串行器在并行数据时钟(TCLK)的上升沿锁存10位并行数据,添加两个开销同步位,并通过单个LVDS输出发送串行化数据。MAX16的并行数据时钟范围为40MHz至9205MHz,MAX40的并行数据时钟范围为60MHz至9207MHz。包括两个同步位后,串行比特率为12 × TCLK。“有效载荷”串行数据速率(串行比特率减去两个同步位)为 10 × TCLK。MAX9205/MAX9207和MAX9206/MAX9208的功能模块如图1所示。

图1.序列化器和解串器功能框图。

在电缆测试设置(图 2)中,二号评估板上的串行器和解串器用于将安捷伦 86130A BER 测试仪的串行 I/O 转换为并行。并行数据应用于第一号电缆测试评估板并从中读取。86130A 输出的串行数据序列长度为 1200 位,由 1000 的 PRBS 中获取 2 位生成10-1 并每 01 个 PRBS 位插入“10”同步位。同步位的插入模拟序列化程序将添加的位。二号板上的解串器去除了同步位,并将PRBS数据与一号板上的电缆测试串行器并行呈现。串行数据序列连续重复。安捷伦 81250 生成所需的参考时钟(串行器的 TCLK 和解串器的 REFCLK)。电缆是以太网 5E 类,AWG24,通用电缆公司制造的非屏蔽双绞线(部件号 2133629H)。

图2.电缆测试设置。

误码率使用5英尺,15英尺,30英尺,60英尺和100英尺的电缆长度进行测试。使用泰克 TDS784C 示波器和泰克 P6247 1.0GHz 差分探头在解串器输入端测量眼图抖动。调整了81250生成的TCLK串行器参考时钟的延迟,以满足数据表中列出的串行器输入设置和保持时间要求。

测量和结果

分别对MAX9205–MAX9206和MAX9207–MAX9208串行器-解串器对进行测试。86130A产生的串行比特率对MAX192–MAX480为9205Mbps–9206Mbps,对MAX480–MAX720为9207Mbps–9208Mbps。

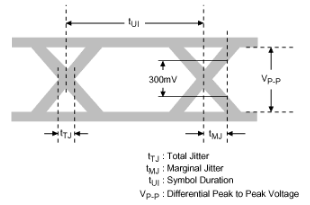

为了定量眼图信号的完整性,定义了两个参数;总抖动tTJ和边缘抖动tMJ。tTJ是在零差分电压下测量的定时抖动的宽度(零差分压力是示波器图中的主要水平栅格)。tMJ是从零差分电压下的抖动中心到300mV峰间差分电压测量的时间(见图3)。可以粗略地假设解串器差分输入在零伏差分下切换,但更保守的是假设附加的差分电压以提供所需的过驱动。tTJ假设在零伏差分下切换,但tMJ要求差分信号在被认为已经切换解串器输入之前达到300mVP-P。因此,tMJ是信号完整性的一个更保守的度量。tUI(也可参见图3)定义为串行位的持续时间(单位间隔)。单位间隔是参考频率的周期除以12。

差分峰间电压表示为VP-P。VP-P是测量点处单端电压差值的两倍,或VP-P例如,在测量点,如果在高状态下VOUT+e1.35V和VOUT-=1.10V相对于地,并且在低状态下VOUT+e1.10V和VOUT-=1.35V相对于地。由于测量是用差分探针(从VOUT+中减去VOUT-)进行的,眼图显示了VP-P。

图3.抖动测量定义。

表 1 显示了 t 的最大值美杰如MAX9206/MAX9208解串器数据资料所示。如果美杰小于或等于列出的最大值。

|

位 速率 (兆字节) |

数据 速率 (兆字节) |

最大 边际 抖动tMJ(ps) |

| 192 | 160 | 1300 |

| 480 | 400 | 720 |

| 720 | 600 | 320 |

试在两种条件下进行。在第一种条件下,在以被测试的串行器-解串器对所允许的最高数据速率对每个电缆长度运行串行测试模式一小时时,测量tTJ和tMJ并计数位错误。在第二种条件下,串行测试数据在高抖动条件下传输超过10小时(传输超过1.73×1013位),从而超过了tMJ的最大数据表值。并且对比特误差进行计数。

表2和表3显示了MAX9205–MAX9206和MAX9207–MAX9208串行器-解串器对的电缆长度从5英尺到60英尺的测试结果。比特率是串行信令速率,数据速率是“有效载荷”串行数据速率(数据速率=(10/12)×比特率)。

表2。MAX9205–MAX9206 tTJ、tMJ、VP-P和位错误(测量一小时)。

|

电缆 长度 (英尺) |

位 速率 (兆字节) |

数据 速率 (兆字节) |

总 抖动 tTJ (ps)* |

边缘的 抖动 tMJ (ps)* |

微分 电压 VP-P(毫伏*) |

错误 计数 (1.728 x 1012位) |

| 5 | 480 | 400 | 200 | 220 | 880 | 无错误 |

| 15 | 480 | 400 | 200 | 260 | 780 | 无错误 |

| 30 | 480 | 400 | 220 | 320 | 636 | 无错误 |

| 60 | 480 | 400 | 360 | 560 | 420 | 无错误 |

| *tTJ的测量分辨率,tTJ 是 10ps。VP-P的测量分辨率为2mV。 | ||||||

|

电缆 长度 (英尺) |

位 速率 (兆字节) |

数据 速率 (兆字节) |

总 抖动 tTJ (ps)* |

边缘的 抖动 tMJ (ps)* |

微分 电压 VP-P(毫伏*) |

错误 计数 (2.592 x 1012位) |

| 5 | 720 | 600 | 180 | 200 | 852 | 无错误 |

| 15 | 720 | 600 | 180 | 230 | 660 | 无错误 |

| 30 | 720 | 600 | 220 | 270 | 556 | 无错误 |

| 60 | 720 | 600 | 320 |

不适用 (五P-P< 300mV) |

292 | 无错误 |

| *tTJ的测量分辨率, tTJ 是 10ps。VP-P的测量分辨率为2mV。 | ||||||

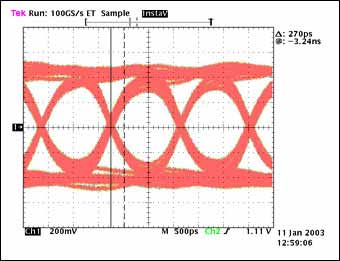

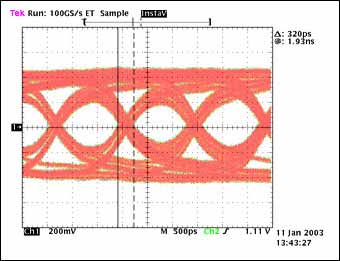

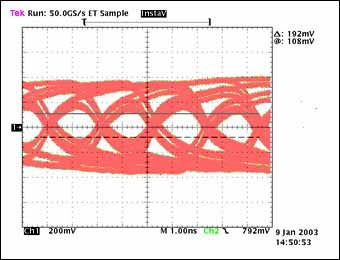

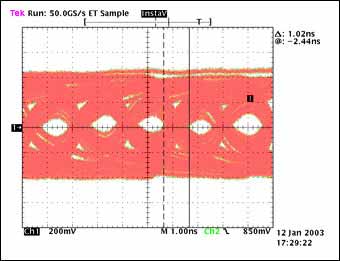

作为测试示例,图4显示了MAX9208解串器输入端30英尺和60英尺电缆后的眼图。

图4a。30英尺电缆的MAX9207–MAX9208眼图。

30英尺,720Mbps,tTJ=220ps,tMJ D270ps,传输2.592×1012位。

没有错误。垂直刻度:200mV/Div。水平比例尺:500ps/分区。

图4b。带60英尺电缆的MAX9207–MAX9208眼图。

60英尺,720Mbps,tTJ=320ps,tMJ PoN/A,传输2.592×1012位。

没有错误。垂直刻度:200mV/Div。水平比例尺:500ps/分区。

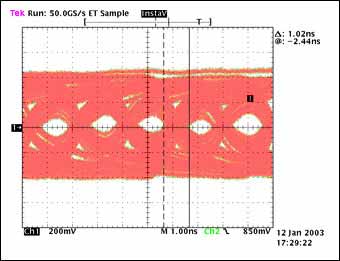

为了演示解串器在信号下降条件下(即抖动裕量小于数据表中指定的抖动裕量)恢复数据的能力,使用100英尺的电缆对两个串行器-解串器对进行了测试。串行测试数据连续传输了10多个小时。表4显示了抖动、峰峰值电压和误差计数的测量结果。图 5 提供了眼图。

|

电缆 长度 (英尺) |

位 速率 (兆字节) |

数据 速率 (兆字节) |

总 抖动 tTJ (ps)* |

边缘的 抖动 tMJ (ps)* |

微分 电压 VP-P(毫伏*) |

错误 计数 (2.592 x 1012位) |

| MAX9205–MAX9206 | ||||||

| 100 | 480 | 400 | 660 | 不适用 | 192 |

传输位: 1.73 x 1013 误差位:0 测试时间: >10小时 |

| MAX9207–MAX9208 | ||||||

| 100 | 520 | 433 | 1020 | 不适用 | 110 |

传输位: 1.87 x 1013 误差位:0 测试时间: >10小时 |

| *t的测量分辨率泰杰, t美杰是 20ps。V 的测量分辨率P-P为2mV。 | ||||||

图5a。100英尺电缆眼图。

100ft,480Mbps,tTJ=660ps,tMJ 2N/A,传输1.73×1013位。

没有错误。垂直刻度:200mV/Div。水平比例尺:1ns/分区。

图5b。100英尺电缆眼图。

100ft,520Mbps,tTJ=1020ps,tMJ PoN/A,传输1.87×1013位。

没有错误。垂直刻度:200mV/Div。水平比例尺:1ns/分区。

在任何测试中都没有记录任何位错误。在以520Mbps的比特率铺设100英尺电缆后,信号的振幅为110mV。这大约是为tMJ指定的300mVP-P振幅的三分之一。此外,对于tTJ E1020ps,超过一半的1923ps单位间隔(tUI E1/520Mbps)是抖动。这些条件下的无误差测试结果提供了数据表规范(表1)中裕度的测量值。

此外,基于测试结果,可以预测BER。假设串行数据序列中任何比特的错误概率是相同的,并且错误事件在比特之间是独立的。如果BER是q,那么串行数据序列可以被建模为具有参数q的伯努利试验。假设n是传输的比特数,那么n比特序列没有错误的概率可以表示为

Pno error = (1 - q)n

在100英尺长的电缆中,传输了超过1.73×1013的电缆,没有出现错误。如果我们假设BER值q小于3.01×10-13,则方程01给出的Pno误差为0.0056。这可以解释为,如果BER的值为3.0×10-13或更大,则观测到的1.73×1013的比特序列不发生错误的概率为0.0056。在统计学方面,如果1.73×1013比特的序列被无差错地传输,则BER<3.0×10-13的假设是99.44%的正确性。由于这种置信度是用100英尺的电缆和较差的信号质量获得的,因此更短的电缆长度和更好的信号质量将产生链路可靠性的更好置信度。

结论

本文利用误码率测试,研究了MAX9205–MAX9206和MAX9207–MAX9208串行器-解串器对在各种长度的低成本CAT-5E电缆上的可靠性。结果表明,即使在信号严重下降的情况下,链路误码率也小于 3.0 × 10-13置信度超过99%。结果还表明,数据手册的抖动最大限值对于高链路可靠性是足够且保守的。由于测量是在典型条件下进行的,因此建议将表1中的标准用于实际应用。这为补偿制造、电源电压和温度的变化提供了裕量。

审核编辑:郭婷

-

lvds

+关注

关注

2文章

1043浏览量

65795 -

信号发生器

+关注

关注

28文章

1472浏览量

108739 -

解串器

+关注

关注

1文章

106浏览量

13237

发布评论请先 登录

相关推荐

英特尔在14nm制程技术上推出32 Gbps串行解串器

探讨串行解串器的技术及其应用

LVDS串行-解串器在双绞线电缆数据传输中的性能分析

LVDS串行-解串器在双绞线电缆数据传输中的性能分析

MAX9259/MAX9260吉比特串行器/解串器芯片组(M

Maxim推出高速LVDS串行器/解串器MAX9263/MAX9265/MAX9264

MAX9272 28位GMSL解串器为同轴电缆或STP电缆

LVDS串行器-解串器在双绞线电缆上的性能

LVDS串行器-解串器在双绞线电缆上的性能

评论