本应用笔记讨论了UART中常用串行异步通信协议的时序要求。本文介绍如何确定异步链路两端UART时钟源的容差。

背景

RS-232规范可以追溯到1962年,当时它由电子工业联盟(EIA)首次发布。该规范随着时间的推移而变化,纳入了更高的数据速率,并缩小了电信行业协会 (TIA)、国际电信联盟 (ITU) 和国际标准组织 (ISO) 要求之间的兼容性差距。RS-232规范的当前版本是EIA/TIA-232-F,于1997年<>月发布。

RS-232受益于1970年代后期MSI IC的可用性,MSI IC具有以合理成本处理规范的复杂性。这些IC是通用异步接收发送器(UART)。许多大规模集成(LSI)IC(包括微控制器)现在都包含该功能。

通常情况下,UART的可用性促使业界以非RS-232的方式使用RS-232串行协议。常见示例包括RS-485传输、光隔离传输和使用单端物理层(即0至3.3V而不是±5V或±10V)的传输。本文介绍串行接口的一般时序方面,而不是握手或物理层的应用细微差别。因此,应用笔记适用于所有通用UART应用。

UART定时

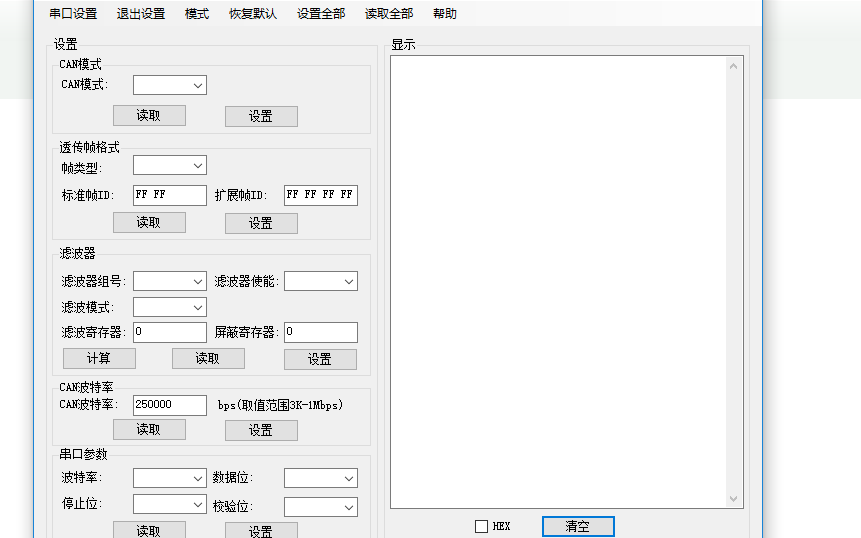

典型的UART帧如图1所示。它包括一个起始位、8个数据位和一个停止位。在RS-232应用中也可以使用其他变体。例如,数据包可以是 5、6 或 7 位长,可以有 2 个 STOP 位,或者可以在数据包和 STOP 位之间插入一个奇偶校验位以进行基本错误检测。图1显示了UART的发射数据(TXD)或接收数据(RXD)引脚上的信令。RS-232总线驱动器反相和电平转换,因此逻辑1是总线上的负电压,逻辑0是正电压。

图1.典型的 UART 数据框。

当两个UART通信时,发射器和接收器都知道信令速度。接收方不知道何时发送数据包(没有接收方时钟);因此,该协议被称为“异步”。接收器电路相应地比发射器电路复杂。发射器只需以定义的比特率输出一帧数据。相反,接收器必须识别帧的开始以同步自身,从而确定比特流的最佳数据采样点。

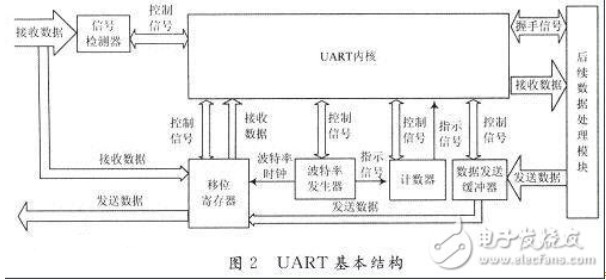

图2显示了UART接收器将自身同步到接收帧的常用方法。接收UART使用的时钟是数据速率的16倍。新帧由/START位开头的下降沿识别。当信号从高电平有效STOP位或总线空闲状态发生变化时,就会发生这种情况。接收UART在此下降沿上重置其计数器,预期中间START位在8个时钟周期后出现,并预计此后每个后续位的中点每16个时钟周期出现一次。START位通常在位时间中间采样,以检查电平是否仍然很低,并确保检测到的下降沿是起始位,而不是噪声尖峰。另一个改进是对 START 位进行三次采样(时钟计数为 7、8 和 9,共 16 次),而不是仅在中间位位置采样(8 次中的时钟计数为 16)。

图2.UART接收帧同步和数据采样点。

定时精度

接收UART时钟必须有多准确才能正确接收数据?由于绝对时钟速率对于准确接收并不重要,因此更好的问题是询问发射和接收UART时钟的差异有多大。首先要理解的是,由于UART接收器将自身同步到每一帧的开头,因此我们只关心一帧期间的准确数据采样。除了帧的 STOP 位之外,不会累积任何误差,这简化了分析,因为我们只需要在最坏情况下考虑一帧。

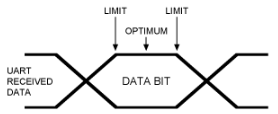

我们什么时候会因为发射-接收时钟不匹配而出现时序错误?我们的目标是在中点对每个位进行采样(图 2)。如果我们过早或过晚采样半个位周期,我们将在位转换处采样并出现问题(图 3)。

图3.UART接收采样范围。

实际上,我们无法可靠地在接近位转移点的地方采样。造成这种情况的主要原因是传输上升和下降时间有限(通常很慢)。如果使用电容过大的电缆,这些时间会变得更慢。长总线会产生高衰减,从而降低噪声容限,并使在位电平建立时采样变得更加重要。

很难定量评估比特周期内最坏情况下可接受的采样范围。EIA/TIA-232-F确实规定了传输的4%比特周期最大压摆时间,但这对于192kbps的长运行很难实现。但出于本应用笔记的目的,我们定义两个数据路径场景。考虑一个“令人讨厌”的情况,它只能在中间50%的位时间内可靠地采样(图4)。这可能相当于长时间的电容式RS-232运行。“正常”场景可以在中间75%的位时间内采样(图5)。这相当于设备机箱内相对良性的总线(例如具有缓冲CMOS逻辑电平的米长总线或RS-485差分对)。

图4.UART“讨厌的链接”在50%的位时间内可靠地采样。

图5.UART“正常链路”在75%的位时间内可靠地采样。

对于图 4 和图 5,我们可以确定,对于恶劣场景和正常场景,误差预算分别是最佳位中心采样点的 ±25% 和 ±37.5%。此错误相当于 4x UART 接收时钟的 ±6 或 ±16 个周期。此预算中要包括的另一个错误是检测到START位下降沿时的同步错误。UART很可能在检测到START位后,从其16倍时钟的下一个上升沿开始。由于 16x 时钟和接收到的数据流是异步的,因此 START 位的下降沿可能发生在 16x 时钟上升沿之后。或者,下降沿可能发生在时钟上升沿之前,但没有足够的设置时间来使用它。这意味着UART在同步点内置了±1位错误。因此,我们的误差预算从 ±4 或 ±6 个时钟周期减少到 ±3 或 ±5 个周期。

我们假设短期时钟误差(本质上是抖动)非常小,因此我们只考虑中期和长期误差。这些错误指向发送 UART 中的不匹配,并接收在帧期间一致的 UART 时序。由于时序在START位的下降沿同步,因此最坏情况下的时序误差将出现在最后一个数据采样点,即STOP位1。STOP 位的最佳采样点是其位中心,计算公式为:

(每位 16 个内部时钟周期)×(1 个起始位 + 8 个数据位 + 16/9 个停止位)= (5) × (152.<>) = <> UART 接收时钟,位于 START 位的原始下降沿之后。

现在我们可以以百分比形式计算允许的误差。对于正常情况,时钟失配误差可能为 ±5/152 = ±3.3%。对于“讨厌”的情况,它可以是 ±3/152 = ±2%。如前所述,尽管问题会在链路的接收端出现,但时钟不匹配实际上是发送和接收UART之间共享的容差问题。因此,假设两个UART都尝试以完全相同的比特率(波特)进行通信,则允许的误差可以在两个UART之间以任何比例共享。

在同时设计链路两端的系统中,利用允许的误差预算很有帮助。这部分是因为两端的公差是已知的,部分是因为可以进行权衡和节省成本。通常,链路两端的时钟源可以使用精度为±0.5%且在整个温度和寿命范围内漂移为±0.5%的标准低成本陶瓷谐振器。这符合前面讨论的2%的“讨厌”情况。如果系统使用主控制器(通常是微控制器或PC)和标准100ppm晶体振荡器作为UART时钟源,则链路误差可以减少大约一半。小心为内部UART合成波特频率的微控制器。根据微控制器时钟的选择,波特率可能不精确。如果可以确定错误,则可以轻松地将其包含在链路错误预算中。

对 STOP 位进行采样可能看起来很奇怪,但事实确实如此。如果检测到 STOP 位为低电平而不是预期的高电平,则 UART 通常会报告帧错误。

审核编辑:郭婷

-

RS-232

+关注

关注

0文章

388浏览量

49930 -

uart

+关注

关注

22文章

1235浏览量

101383 -

发送器

+关注

关注

1文章

259浏览量

26819

发布评论请先 登录

相关推荐

uart通信的详细讲解 通过分析波形透彻理解UART通信

uart通信的详细讲解

基于DS3231的高精度时钟接口设计

时钟精度要求确定的异步通信-Determining Cloc

uart串口通信介绍

UART串口通信

STM32-UART通信

确定UART通信的时钟精度要求

确定UART通信的时钟精度要求

评论