随着微电子技术的迅猛发展,SRAM 逐渐呈现出高集成度、快速及低功耗的发展趋势。在半导体存储器的发展中,静态存储器(SRAM)由于其广泛的应用成为其中不可或缺的重要一员。近年来SRAM在改善系统性能、提高芯片可靠性、降低成本等方面都起到了积极的作用。

在了解SRAM之前,有必要先说明一下RAM。RAM主要的作用就是存储代码和数据供CPU在需要的时候调用。但是这些数据并不是像用袋子盛米那么简单,更像是图书馆中用书架摆放书籍一样,不但要放进去还要能够在需要的时候准确的调用出来,虽然都是书但是每本书是不同的。对于RAM等存储器来说也是一样的,虽然存储的都是代表0和1的代码,但是不同的组合就是不同的数据。

让我们重新回到书和书架上来,如果有一个书架上有10行和10列格子(每行和每列都有0-9的编号),有100本书要存放在里面,那么我们使用一个行的编号+一个列的编号就能确定某一本书的位置。在RAM存储器中也是利用了相似的原理。

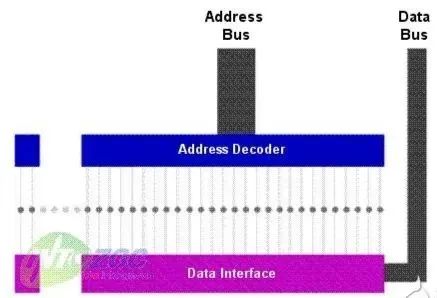

现在让我们回到RAM存储器上,对于RAM存储器而言数据总线是用来传入数据或者传出数据的。因为存储器中的存储空间是如果前面提到的存放图书的书架一样通过一定的规则定义的,所以我们可以通过这个规则来把数据存放到存储器上相应的位置,而进行这种定位的工作就要依靠地址总线来实现了。

对于CPU来说,RAM就像是一条长长的有很多空格的细线,每个空格都有一个唯一的地址与之相对应。如果CPU想要从RAM中调用数据,它首先需要给地址总线发送“编号”,请求搜索图书(数据),然后等待若干个时钟周期之后,数据总线就会把数据传输给CPU。

小圆点代表RAM中的存储空间,每一个都有一个唯一的地址线同它相连。当地址解码器接收到地址总线的指令:“我要这本书”(地址数据)之后,它会根据这个数据定位CPU想要调用的数据所在位置,然后数据总线就会把其中的数据传送到CPU。

下面该介绍一下今天的主角SRAM:

SRAM——“Static RAM(静态随机存储器)”的简称,所谓“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。这里与我们常见的DRAM动态随机存储器不同,具体来看看有哪些区别:

SRAM VS DRAM

SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失。因此SRAM具有较高的性能,功耗较小。

此外,SRAM主要用于二级高速缓存(Level2 Cache)。它利用晶体管来存储数据。与DRAM相比,SRAM的速度快,但在相同面积中SRAM的容量要比其他类型的内存小。

但是SRAM也有它的缺点,集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。同样面积的硅片可以做出更大容量的DRAM,因此SRAM显得更贵。

还有,SRAM的速度快但昂贵,一般用小容量SRAM作为更高速CPU和较低速DRAM 之间的缓存。

总结一下:

SRAM成本比较高

DRAM成本较低(1个场效应管加一个电容)

SRAM存取速度比较快

DRAM存取速度较慢(电容充放电时间)

SRAM一般用在高速缓存中

DRAM一般用在内存条里

SRAM如何运作

刚才总结到了SRAM有着很特别的优点,你该好奇这家伙是怎样的运作过程?

一个SRAM单元通常由4-6只晶体管组成,当这个SRAM单元被赋予0或者1的状态之后,它会保持这个状态直到下次被赋予新的状态或者断电之后才会更改或者消失。SRAM的速度相对比较快,且比较省电,但是存储1bit的信息需要4-6只晶体管制造成本可想而知,但DRAM只要1只晶体管就可以实现。

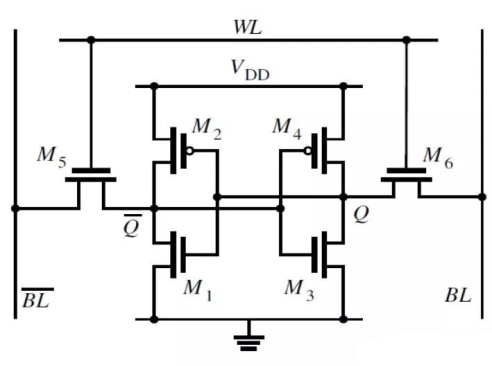

连接一下SRAM的结构,比较出名的是6场效应管组成一个存储bit单元的结构:

M1-6表示6个晶体管,SRAM中的每一个bit存储由4个场效应管M1234构成两个交叉耦合的反相器中。一个SRAM基本单元有0、1 两个状态。

SRAM基本单元由两个CMOS反相器组成,两个反相器的输入输出交叉连接,即第一个反相器的输出连接第二个反相器的输入,第二个反相器的输出连接第一个反相器的输入。这实现了两个反相器输出状态的锁定、保存,即存储了一个位元的状态。

一般而言,每个基本单元的晶体管数量越少,其占用面积就会越小。由于硅晶圆生产成本相对固定,所以SRAM基本单元面积越小,在芯片上就可制造更多的位元存储,每个位元存储的成本就越低。

SRAM工作原理相对比较简单,我们先看写0和写1操作。

写0操作

写0的时候,首先将BL输入0电平,(~BL)输入1电平。

然后,相应的Word Line(WL)选通,则M5和M6将会被打开。

0电平输入到M1和M2的G极控制端

1电平输入到M3和M4的G极控制端

因为M2是P型管,高电平截止,低电平导通。而M1则相反,高电平导通,低电平截止。

所以在0电平的作用下,M1将截止,M2将打开。(~Q)点将会稳定在高电平。

同样,M3和M4的控制端将会输入高电平,因NP管不同,M3将会导通,而M4将会截止。Q点将会稳定在低电平0。

最后,关闭M5和M6,内部M1,M2,M3和M4处在稳定状态,一个bit为0的数据就被锁存住了。

此时,在外部VDD不断电的情况下,这个内容将会一直保持。

下面通过动画来观察一下写0的过程。

写1操作

这里不再重复,大家可以自己推演一下过程。这里仍然提供写1过程动画。

读操作

读操作相对比较简单,只需要预充BL和(~BL)到某一高电平,然后打开M5和M6,再通过差分放大器就能够读出其中锁存的内容。

**SRAM行业发展趋势 **

随着处理器日趋强大,尺寸越发精巧。然而更加强大的处理器需要缓存进行相应的改进。与此同时每一个新的工艺节点让增加嵌入式缓存变得艰巨起来。SRAM的6晶体管架构(逻辑区通常包含4个晶体管/单元)意味着每平方厘米上的晶体管的数量将会非常多。这种极高的晶体管密度会造成很多问题,其中包括:

SER:软错误率;Processnode:工艺节点soft:软错误

更易出现软错误:工艺节点从130nm缩小到22nm后,软错误率预计将增加7倍。

更低的成品率:由于位单元随着晶体管密度的增加而缩小,SRAM区域更容易因工艺变化出现缺陷。这些缺陷将降低处理器芯片的总成品率。

更高的功耗:如果SRAM的位单元必需与逻辑位单元的大小相同,那么SRAM的晶体管就必须小于逻辑晶体管。较小的晶体管会导致泄露电流升高,从而增加待机功耗。

另一个技术发展趋势可穿戴电子产品的出现。对于智能手表、健身手环等可穿戴设备而言,尺寸和功耗是关键因素。由于电路板的空间有限,MCU必须做得很小,而且必须能够使用便携式电池提供的微小电量运行。

片上缓存难以满足上述要求。未来的可穿戴设备将会拥有更多功能。因此片上缓存将无法满足要求,对外置缓存的需求将会升高。在所有存储器选项中,SRAM最适合被用作外置缓存,因为它们的待机电流小于DRAM,存取速度高于DRAM和闪存。

对于所有类型的系统设计者来说,新兴存储技术都变得极为关键。AI和物联网IoT芯片开始将它们用作嵌入式存储器。大型系统已经在改变其架构,以采用新兴的存储器来替代当今的标准存储器技术。这种过渡将挑战行业,但将带来巨大的竞争优势。

今天,业界仍在寻找通用存储器,随着SoC工艺进步设计复杂度增加,嵌入式 SRAM也越来越多。在40nm SoC产品SRAM一般在20Mbits左右,当工艺发展到28nm时SRAM就增加到100Mbits。如果考虑AI产品,SRAM估计更多。如何更好的测试SRAM就成为量产测试的重中之重。这也是推理芯片的最佳方案,也是芯片设计者在设计中应该努力追求的目标。

为了应对这一市场变化,新兴存储器PB的发货量将比其它传统存储技术增长得更快,促使其营收增长到360亿美元。之所以会发生这种情况,很大程度上是因为这些新兴的存储器将占领当今主流技术(NOR闪存,SRAM和DRAM)的既有市场份额。新存储器将取代分立存储芯片和SoC中的嵌入式存储器:包括ASIC,微控制器,甚至是计算处理器中的缓存。

到2030年,3D XPoint存储器收入将飙升至超过250亿美元,这主要是因为该技术的售价低于它所取代的DRAM。这也解释了为什么离散MRAM / STT-MRAM芯片收入将增长到超过100亿美元,或者说是2019年MRAM收入的近300倍。此外,预计电阻RAM(ReRAM)和MRAM将竞争取代SoC中的大量嵌入式NOR和SRAM,从而推动更大规模的收入增长。

目前,尚不清楚哪种存储技术将成为这场战斗的赢家。相变存储器(PCM),ReRAM,铁电RAM(FRAM),MRAM和许多尚未成熟的技术,每种都有各自的竞争优势和劣势。目前处于竞争行列的有将近100家公司,这些公司包括芯片制造商、技术许可方、晶圆代工厂和工具和设备制造商,几乎覆盖了半导

-

存储器

+关注

关注

38文章

7538浏览量

164607 -

cpu

+关注

关注

68文章

10931浏览量

213533 -

sram

+关注

关注

6文章

769浏览量

115005

发布评论请先 登录

相关推荐

STM32的程序和数据在Flash和SRAM上到底是如何存储的

IMXRT1064智能外部存储器引脚多路复用器是什么意思?

SRAM,SRAM原理是什么?

SRAM模块,SRAM模块结构原理是什么?

sram是什么,sram信息详解

单片机、桌面电脑/PC、嵌入式系统的启动思路对比。

sram作用

如何对SRAM进行分类

SRAM与DRAM究竟有何区别?谁能成为存储技术杀手锏

SRAM和DRAM到底有什么区别和SRAM的发展趋势说明

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用户手册

到底什么是SRAM

到底什么是SRAM

评论